什么是抖动和相位噪声?如何区分晶振时钟?

品慧电子讯抖动(Jitter)反映的是数字信号偏离其理想位置的时间偏差。高频数字信号的 bit 周期都非常短,一般在几百 ps 甚至几十 ps,很小的抖动都会造成信号采样位置电平的变化,所以高频数字信号对于抖动都有严格的要求。

什么是抖动和相位噪声?

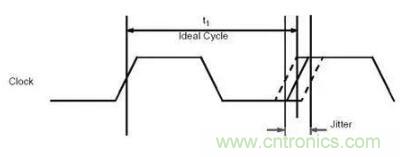

抖动(Jitter)反映的是数字信号偏离其理想位置的时间偏差。高频数字信号的 bit 周期都非常短,一般在几百 ps 甚至几十 ps,很小的抖动都会造成信号采样位置电平的变化,所以高频数字信号对于抖动都有严格的要求。

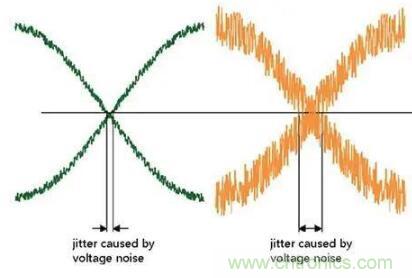

实际信号的很复杂,可能既有随机抖动成分(RJ),也有不同频率的确定性抖动成分(DJ)。确定性抖动可能由于码间干扰或一些周期性干扰引起,而随机抖动很大一部分来源于信号上的噪声。下图反映的是一个带噪声的数字信号及其判决阈值。一般我们把数字信号超过阈值的状态判决为“1”,把低于阈值的状态判决为“0”,由于信号的上升沿不是无限陡的,所以垂直的幅度噪声就会造成信号过阈值点时刻的左右变化,这就是由于噪声造成信号抖动的原因。

要进行信号抖动的分析,最常用的工具是宽带示波器配合上响应的抖动分析软件。示波器里的抖动分析软件可以方便地对抖动的大小和各种成分进行分解,但是示波器由于噪声和测量方法的限制,很难对亚 ps 级的抖动进行精确测量。现在很多高速芯片对时钟的抖动要求都在 1ps 以下甚至更低。这就需要借助于其它的测量方法比如相位噪声(phase noise)的测量方法。

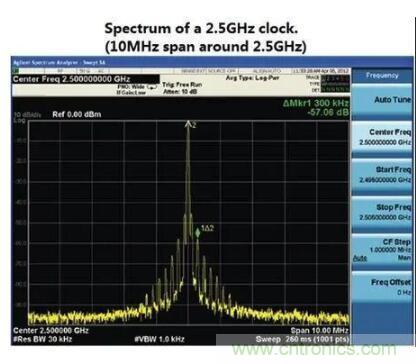

我们知道抖动是时间上的偏差,它也可以理解成时钟相位的变化,这就是相位噪声。对于时钟信号,我们观察其基波的频谱分布。理想的时钟信号其基波的频谱应该是一根很窄的谱线,但实际上由于相位噪声的存在,其谱线是比较宽的一个包络,这个包络越窄,说明相位噪声(抖动)越小,信号越接近理想信号。下图是一个真实时钟信号的频谱,信号的基波在 2.5GHz,我们观察 2.5GHz 附近 10MHz 带宽的频谱。我们可以看到首先信号的频谱不是一根很窄的谱线,其谱线有展宽(随机噪声的影响),其次上面叠加的还有一些特定频率的干扰(确定性抖动的影响)。

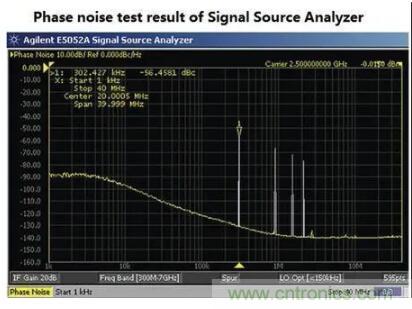

为了更方便观察低频的干扰,在相位噪声测量中通常会以信号的载波频率为起点,把横坐标用对数显示,其横坐标反映的是离信号载波频率的远近,纵坐标反映的是相应频点的能量和信号载波能量的比值。这个比值越小,说明除了载波以外其它频率成分的能量越小,信号越纯净。要进行时钟信号的相位噪声精确测量使用的仪器是信号源分析仪,信号源分析内部有特殊的电路,通过两个独立本振的多次相关处理可以把自身本振的相位噪声压得非常低,从而可以进行精确的相位噪声测量。

对于很多晶振产生的时钟来说,其抖动中的主要成分是随机抖动。如果我们把相位噪声测试结果里不同频率成分的相位噪声能量进行积分的话,我们就能够得到随机抖动。通过信号源分析仪对相位噪声测量然后对一定带宽内的能量进行积分,我们就可以得到精确的随机抖动测量结果。信号源分析仪能测量到的最小抖动可以到 fs 级。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请电话或者邮箱联系小编进行侵删。

推荐阅读:

2020中国(深圳)集成电路峰会将于10月底召开

贸泽与Qorvo联手推出全新电子书聚焦Wi-Fi 6应用与解决方案

Bang & Olufsen在其95周年纪念版旗舰耳罩式耳机中选用艾迈斯半导体ANC解决方案

逐次逼近寄存器型ADC与其它类型ADC的架构有何区别?

Σ-Δ模数转换器(ADC)大揭秘