双 μC 的 PWM 频率和分辨率

品慧电子讯:有两种方法可以降低 PWM DAC 的纹波。可以降低低通滤波器的截止频率,或者提高PWM信号的频率。不可避免地,较低的截止频率转化为较慢的上升时间,而更快的 PWM 频率转化为较低的分辨率(通过在给定时钟频率下减小计数器大小来实现)。

该方法是过滤 PWM 信号的 HF 分量,只留下与占空比成正比的 LF 或 DC 分量。然而,低通滤波器并不能完全滤除PWM频率,因此LF/DC信号一般会有一些纹波。

有两种方法可以降低 PWM DAC 的纹波。可以降低低通滤波器的截止频率,或者提高PWM信号的频率。不可避免地,较低的截止频率转化为较慢的上升时间,而更快的 PWM 频率转化为较低的分辨率(通过在给定时钟频率下减小计数器大小来实现)。

我将讨论一个有趣的设计理念,它专注于在不使用上述方法的情况下降低 PWM DAC 的纹波。

事实证明,我们可以通过使用两个相位差为 180° 的 PWM 信号来降低纹波。直观上,当两个相同频率的正弦信号之间存在 180° 相位差时,它们会相互抵消,所以我们期望当我们使用两个具有 180° 相位差的 PWM 信号时,谐波会相互抵消,对吗?嗯,这是真的,但不是 PWM 信号的所有谐波。其中一些被取消,但其中一些 不。它与傅里叶级数有关,对于这篇文章来说有点太复杂了,所以我不会深入讨论数学。

如何实现两个 PWM 信号之间的 180° 相移?我使用了 TI 的MSP430FR5969 LaunchPad,但该方法大多是通用的。为了实施相移,您将需要两个定时器。其中一个定时器必须有两个比较捕获 PWM (CCP) 模块,另一个只需要一个 CCP。

您可以使用其中一个 CCP 在具有两个 CCP 的定时器中设置 PWM 频率和占空比,并使用另一个 CCP 生成中断以启动另一个定时器,延迟等于 PWM 周期的一半。另一个定时器中的单个 CCP 用于设置相同的 PWM 频率和占空比。您还必须“微调”延迟,因为软件将在 PWM 信号之间引入额外的时间。例如,在我的代码的第 102 行,我将比较寄存器值从 (timer_period+1)/2 更改为 (timer_period+1)/2-27。

我做了一些研究,看看其他微控制器是否有类似的硬件以及实现我使用的方法的能力:许多 Atmel 微控制器有多个定时器,通常每个都有两个 CCP(例如,ATmega 328)。因此,应该可以实施此方法。另一个流行的例子,STM32F051R8(这是一些流行的 ST 板使用的微控制器)有 11 个定时器,其中许多有多个 CCP。Texas Instrument 的基于 ARM 的微控制器通常具有单独的 PWM 和定时器模块(例如 TM4C123GH6PM),因此应该更容易实现相移。通过使用其中一个定时器,两个 PWM 模块可以以半个 PWM 周期的延迟启动。如果您尝试为不同的微控制器实施这种相移方法,请在评论部分告诉我。

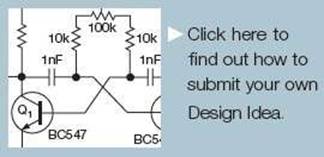

图1 单和双 PWM 电路

在 相移 DAC 的V out 处,两个 PWM 信号相加在一起,希望一些谐波相互抵消,因此我们终得到较低的纹波。

让我们看一下使用不同电阻值的三种情况。每个 PWM 信号在 25% 的占空比下都是 100 kHz。

图2 上面的迹线是传统的 PWM。下方是双相移 PWM。伏特/格 从左到右递减:100mV、50mV、5mV。

通过查看结果,我们观察到两件事。首先,峰峰值纹波降低。其次,传统 PWM DAC 的纹波基频等于 PWM 信号的频率 (100 kHz)。相移 PWM DAC 的纹波基频等于 PWM 信号的二次谐波 (200 kHz),这意味着我们成功地使用相移 DAC 消除了 PWM 信号的谐波。

这种方法的一个优点是在不增加上升时间的情况下降低纹波(或在上升时间的一半时保持相同的纹波)。

另一个潜在的优势是通过将两个 PWM 分开一个计数以获得中间值,从而使 DAC 的有效分辨率加倍。这确实会导致轻微的不对称和纹波增加,但影响可以忽略不计。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

优化高精度倾斜/角度感测:增强性能

推动电气化发展的 4 大电流检测设计趋势

添加阈值滞后以实现平滑的欠压/过压锁定

信号继电器-了解基础知识

使用无电阻传感解决方案扩大电流测量范围