恩智浦利用台积电5nm工艺开发下一代汽车SoC平台

台积电最近几周一直在加强其5nm制程技术,首先是与恩智浦合作,最近又与Cadence和微软合作,以缩减半导体设计时序签发时间表。

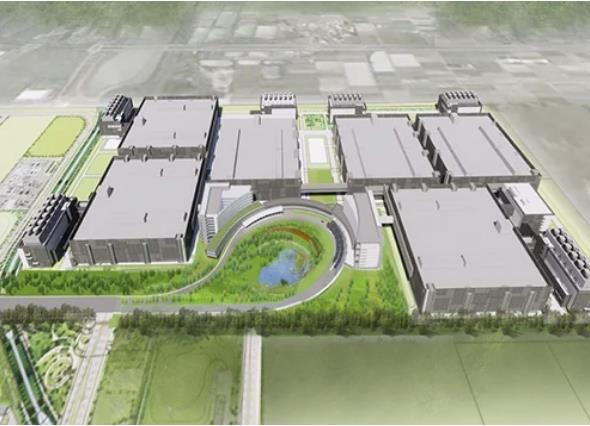

台积电5纳米生产设施之一的渲染图。图片由台积电提供

近期,恩智浦发布公告,该公司表示,他们选择了台积电来帮助他们开发适用于下一代汽车处理器的5nm SoC平台。那么新的5nm工艺提供了什么?这对设计人员意味着什么?

虽然第一批IC仅包括少数具有毫米范围特征的晶体管,但现在IC拥有数十亿个具有单纳米级特征的晶体管。减小晶体管的尺寸不仅允许将更多的器件装配到单个芯片上,而且允许更复杂的设计。

过去,通过改进掺杂工艺,改进光学设备并创建更小的掩模,相对容易实现降低晶体管的功能。但是,由于晶体管的特征尺寸在纳米范围内,因此任务变得更加复杂。由于所有这些复杂性,许多半导体器件都依赖于高度复杂的过程,而只有少数几家晶圆厂能够满足这些过程。

恩智浦已经与台积电建立了合作关系,以利用台积电的5nm鳍式场效应晶体管(FinFET)工艺技术。尽管该技术通常针对移动和高性能计算应用进行了优化,但恩智浦计划将其用于汽车处理器。

近年来,恩智浦已在汽车和航空航天行业进行开发投资,以开发面向未来的智能解决方案。恩智浦(NXP)和台积电(TSMC)即将合作的应用实例包括互联驾驶舱、高性能域控制器、自动驾驶、网络、混合动力和集成底盘管理。

新的基于5nm的SoC将推动汽车的智能连接技术。图片由NXP提供

台积电的新工艺技术N5P是其5nm技术的增强版,已经引起了多家公司的关注。台积电全球市场部负责人郑国富在去年的台积电博客文章中声称,新型N5P将“具有世界上最高的晶体管密度并提供最快的性能”。

新的N5P技术对其前身7nm工艺进行了多项改进。第一个改进是它提供了高达20%的更快速度,从而实现了更高的数据速率。第二个改进是它可以将功耗降低多达40%,与以前的设备相比,在功耗相同的情况下,其晶体管数量约为其两倍。

恩智浦计划使用该技术扩展其S32架构,以创建一个可扩展性和通用软件环境的系统。恩智浦希望这将为未来的汽车应用程序提供跨领域的统一软件基础架构,从而无论最终应用程序如何,其基础架构都是统一的,使用5nm工艺及其更高的处理能力可实现这种架构。恩智浦预计将在2021年将第一批样品发送给主要客户。

自新型冠状病毒肺炎疫情爆发以来,传感器专家网一直密切关注疫情进展,根据国家及地方政府的最新调控与安排,为更好的服务相关企业,在疫情期间,传感器专家网免费发布企业相关文章,免费成为传感器专家网认证作者,请点击认证,大家同心协力,抗击疫情,为早日打赢这场防控攻坚战贡献自己的一份力量。