三星英特尔积极布局FinFET替代工艺

2001年,加州大学伯克利分校胡正明教授提出FinFET方案。2011年,英特尔正式商用FinFET工艺技术,之后台积电也迅速跟进,在16nm节点中使用了FinFET。从16/14nm开始,FinFET成为了半导体器件的主流选择。

FinFET称为鳍式场效晶体管(FinField-EffectTransistor;FinFET)是一种新的互补式金氧半导体(CMOS)晶体管。闸长已可小于25奈米,未来预期可以进一步缩小至9纳米,约是人类头发宽度的1万分之1。

传统平面的晶体管所采用的是FD-SOI工艺。虽然这几年的FinFET工艺占据了大多数人的视线,但是FD-SOI工艺依然非常重要。如果要是FinFET工艺核FD-SOI达到相同性能,FD-SOI工艺在制造过程中相对简单,但是SOI基片价格稍贵,而FinFET工艺虽然制造过程更为复杂,但是由于基片价格便宜,让两者的实际制造成本相差不大。

但是,由于工艺要求更高,FinFET工艺在5nm以下节点遇到了问题。到了5nm节点后,虽然已经使用上了EUV光刻技术,但是基于FinFET结构进行的芯片尺寸的缩小,就变得更加困难。FinFET工艺制造、研发成本也越来越高,即使在7nm、5nm仍能坚持,但是再往前似乎已经是力不从心。

图片来源网络

随着晶体管尺度向5nm甚至3nm迈进,FinFET本身的尺寸已经缩小至极限后,无论是鳍片距离、短沟道效应、还是漏电和材料极限也使得晶体管制造变得岌岌可危,甚至物理结构都无法完成。

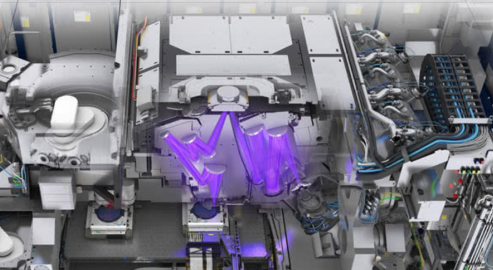

不过,代工巨头们并没有回头再去深究FD-SOI工艺,而是对环绕栅极(GAA)器件产生了极大的兴趣。与FinFET工艺中的立体沟道三面都被栅极围绕不同,到了GAA,沟道由纳米线(nanowire)构成,其四面都被栅极围绕,从而再度增强栅极对沟道的控制能力,有效减少漏电。

总体而言,GAA制造方式主要是通过外延反应器在集体上制造出超晶格结构,这样的结构至少需要硅锗材料或者三层硅材料堆叠而成,并且还需要形成STI浅槽隔离,接下来需要多晶硅伪栅成像、隔离层和内部隔离层成型、漏极和源极外延、沟道释放、高K金属栅极成型、隔离层中空、环形触点成型等。

外界传言,台积电在3nm节点可能没有三星这么激进,继续沿用FinFET工艺的可能性存在,在第二代3nm或2nm上才会升级到GAA晶体管技术。但英特尔和三星很可能押宝在GAA技术上,以此来缩小和台积电之间的差距,甚至是超越台积电。