台积电与博通联合打造1700平方毫米巨型中介层

晶体管越来越小,但是高性能计算需求越来越高,有些人就反其道而行之,尝试制造超大芯片。之前我们就见识过Cerebras Systems打造的世界最大芯片WSE,拥有46225平方毫米面积、1.2万亿个晶体管、40万个AI核心、18GB SRAM缓存……并得到了美国能源部的青睐和部署。

晶体管越来越小,但是高性能计算需求越来越高,有些人就反其道而行之,尝试制造超大芯片。之前我们就见识过Cerebras Systems打造的世界最大芯片WSE,拥有46225平方毫米面积、1.2万亿个晶体管、40万个AI核心、18GB SRAM缓存……并得到了美国能源部的青睐和部署。

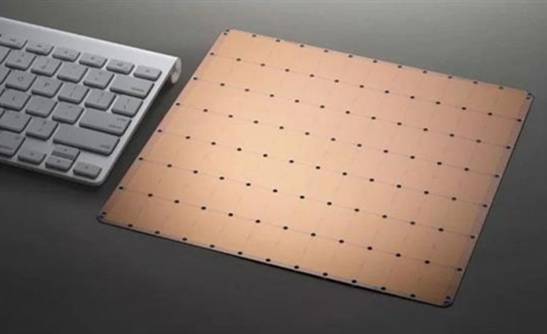

现在,台积电、博通联合宣布,双方将利用晶圆上芯片封装(CoWos)技术,打造面积达1700平方毫米的中介层(Interposer),是芯片蚀刻所用光掩模(光罩)尺寸极限858平方毫米的整整两倍。

这样规模的中介层显然是无法一次性单个制造出来的,台积电实际上是同时在晶圆上蚀刻多个中介层,然后将它们连接在一起,组成一个整体。

工艺上,台积电也用上了最先进的5nm EUV(N5),它将在今年上半年投入量产。

所谓中介层,用途就是串联不同裸片(Die)的桥梁,因为随着现代芯片日益复杂,制造单个大型SoC的代价越来越大,所以行业普遍开发出了各种新的封装技术,将不同的小芯片、模块整合在一起,构成一颗大芯片。

博通就计划用这个庞大无比的中介层,封装多个SoC芯片,以及六颗HMB2内存,单颗容量16GB,总容量达96GB/s,带宽也高达2.7TB/s。

看这规格,应该是三星最新的HBM2E。

台积电和高通未透露这种庞大芯片的具体规格,只是说将用于高性能计算领域。另外,台积电还在改进CoWoS封装技术,所以未来不排除面积超过1700平方毫米的更大芯片。