控制电源启动及关断时序

品慧电子讯微处理器、FPGA、DSP、模数转换器 (ADC) 和片上系统 (SoC) 器件一般需要多个电压轨才能运行。为防止出现锁定、总线争用问题和高涌流,设计人员需要按特定顺序启动和关断这些电源轨。此过程称为电源时序控制或电源定序,目前有许多解决方案可以有效实现定序。

微处理器、FPGA、DSP、模数转换器 (ADC) 和片上系统 (SoC) 器件一般需要多个电压轨才能运行。为防止出现锁定、总线争用问题和高涌流,设计人员需要按特定顺序启动和关断这些电源轨。此过程称为电源时序控制或电源定序,目前有许多解决方案可以有效实现定序。

此外,为有效进行升压和关断而应运而生的各种电源定序器、监视器和监控器还采用了电压和电流水平监控技术来计算功率水平,目的是保护复杂的集成电路和子组件。

本文将详细介绍电源定序,探讨电源定序规范和技术,以及如何使用电源定序器来实现指定的电源轨定时及定序。

为什么要关注电源定序?

FPGA 及类似的复杂集成电路 (IC) 可在内部分解成多个功率域。在启动或关断器件时,此类 IC 大多需要特定的顺序。例如,FPGA 通常需要分别为内核逻辑、I/O 和辅助电路上电。

其内核通常包括 FPGA 的处理器和基本逻辑单元。该功率域具有低电压、高电流功率规范特征。由于电压极低,因此其对精度要求极高,而由于数字负载的动态特性,瞬态性能必须非常出色。I/O 代表 FPGA 的各种输入和输出。电压要求取决于接口类型。一般来说,其电压电平需大于内核的电压电平。电流要求则取决于 I/O 的类型、数量和速度。

辅助电路包括 FPGA 中的噪声敏感型模拟电路,例如锁相环 (PLL) 和其他模拟电路元件。虽然电流要求相当低,但纹波电压是个大问题,必须最大程度地降低纹波电压。模拟部分的纹波可能会导致 PLL 出现过大抖动和相位噪声,还可能导致放大器出现杂散响应。

以错误顺序启动各功率域的电源可能会引起问题,并可能导致 FPGA 受损。需要考虑的是,I/O 部分基于三态总线收发数据,而内核负责处理 I/O 控制。如果 I/O 功率域在内核之前上电,则 I/O 引脚会以不确定状态结束。如果外部总线组件上电,则可能存在总线争用问题,导致 I/O 驱动器出现高电流。因此,内核应在 I/O 功率域之前启动。请务必查阅供应商的 FPGA 规范,了解推荐的电源启动和关断顺序以及电源轨之间的最大差分电压。

同样,功率运算放大器等器件拥有两个功率域:模拟域和数字域。数字域为放大器的诊断状态标记提供电源,识别过热和过流状态。此外,数字域还支持放大器的使能/关断功能。该器件规格要求,数字域应在模拟电源之前上电,以便这些状态标记在模拟域上电之前能够正常运行。这样做的目的是防止可能对器件造成损坏。

电源定序方法

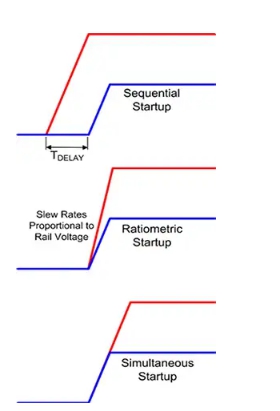

通常有三种类型的多轨定序(图 1)。最常用的方法是顺序定序,这种方法是先接通一个电源轨,然后延时,然后再接通下一个电源轨。设置延时的目的是确保第一个电源轨在第二个电源轨启动之前达到稳压。

图 1:三种电源定序技术。不论采用哪种技术,电压均须以单调方式上升。否则,器件可能会因启动期间电压意外下降而无法正确初始化。(图片:Digi-Key Electronics)

第二种定序技术是比率定序。在该技术中,电源轨会同时启动并同时达到各自的额定电压。这就需要电源轨上升时间与电源轨电压成正比,才能同时实现稳压。

有些器件可能无法承受达到稳压之前发生的瞬时电压差。而这可能导致器件在此期间在一个电源上消耗更高的电流。

第三种方法是同时启动,这种方法可以最大限度地减少瞬时电压差,并且可以减少这些压力的规模和周期。实施这种方法的一种常见方式是同时上电,即:电压轨以相同速率一起上升,较高的电压轨(通常是 I/O 电压轨)在较低电压轨或内核电压轨达到其最终值后继续上升。

不论采用哪种技术,电压均须以单调方式上升。否则,器件可能会因启动期间电压意外下降而无法正确初始化。

另外,可以使用软启动来限制启动期间的涌流。这种做法可以限制启动期间的电流,从而允许启动时逐渐对电源轨电容进行充电。

电源关断顺序通常被指定成与启动顺序相反。

选择使用何种启动或关断技术应取决于器件的规格。

电源定序示例

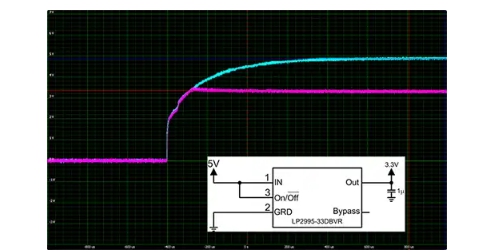

同时启动相对容易设置。您需要将最高电压输出连接到较低电压稳压器的输入上(图 2)。

图 2:通过以菊花链方式连接稳压器可以实现 5 V 电源和 3.3 V 电源的同时启动。(图片:Digi-Key Electronics)

在本示例中,较高电压是 5 V 电源。这个 5 V 电压也馈入 3.3 V 稳压器。图中显示的是 5 V 和 3.3 V 电源同时上升且最小压差达到 3.3 V 电源稳压点时的电压输出。

该定序技术最好使用定序器集成电路(如 Texas Instruments 的 LM3880)来实现。LM3880 是一款简单的电源定序器,可通过稳压器或电源的使能输入来控制多个独立的稳压器或电源。

当 LM3880 启动时,三个输出标志将在各个延迟时间后依次释放,从而允许连接的电源进行启动。在关断期间,输出标志将遵循相反的顺序。下图是一个使用 LM3880 的设计实例,采用 Texas Instruments 的 WEBENCH Power Designer 软件设计而成(图 3)。这款免费软件工具不仅能帮助工程师设计与电源相关的电路,而且还能提供示意图、材料清单及模拟结果。该图显示了示意图、图表、使能以及三个标志输出。

LM3880 的延迟时间和次序是固定不变的,但可通过内置的 EPROM 在工厂进行定制。此外,Texas Instruments 还为 LM3881 定序器提供了电容器可编程延迟功能。

图 3:Texas Instruments 的 WEBENCH Power Designer 软件屏幕截图显示了 LM3880 设计示意图以及用于控制外部稳压器或电源的使能输入及输出标志图表。(图片:Digi-Key Electronics)

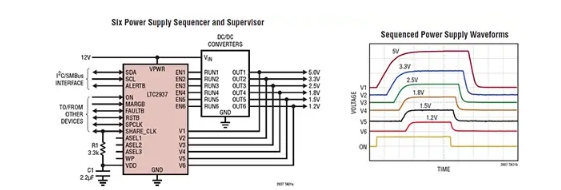

Analog Devices 的 LTC2937 定序器/电压监控器是一款稍微复杂的电源控制器件。与 LM3880 一样,LTC2937 可以控制多达六个电源或稳压器的时序和时间延迟(图 4)。

图 4:LTC2937 最多可以控制六个电源时序,同时还可以监控电源轨电压。通过一根电线可以同步多个器件,最多可控制 300 个电源。(图片:Analog Devices)

除了最多可对六个电源轨进行定序外,这款定序器还可以监控这些电源轨上的电压,进而过压、欠压、压降及失控电源启动检测。如果发生故障,您可以对该器件进行编程以关断或重启电源。错误情况将会记录到内部的 EEPROM 中。LTC2937 可通过 I2C 或 SMBus 进行编程和控制。其编程可借助 Analog Devices 的 LTpowerPlay GUI 软件进行。EEPROM 支持自主运行且无需软件。若系统需要六个以上电源轨,只需将多个 LTC2937 链接在一起,即可控制多达 300 个电源。

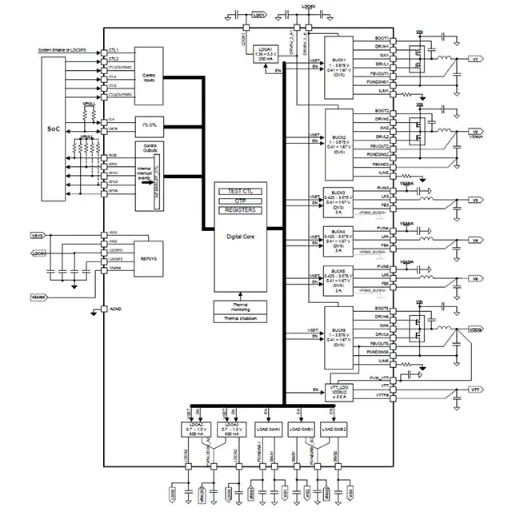

对于复杂的多核处理器、FPGA 以及其他 SOC 器件,Texas Instruments 提供了 TPS650860 可配置多轨电源管理单元。这款单 IC、输入电压范围 5.6 V - 21 V 的电源管理单元包含三个降压控制器、三个降压转换器、一个灌入或拉出低压差 (LDO) 线性稳压器、三个低压输入 LDO、稳压器和三个负载开关(图 5)。

图 5:Texas Instruments 的 TPS650860 功能框图显示了 13 个时序完全受控的稳压输出。(图片:Texas Instruments)

该器件具有 13个稳压输出,可满足 FPGA 或其他负载器件的需求。

其降压转换器含内置功率级,而降压控制器则需要外部功率级。无论是转换器,还是控制器,均集成了电压感应输入来监控电源输出,从而实现定序控制。其负载开关含有压摆率控制,可以针对三种定序类型(顺序、比率或同时)的任意一种对与这些开关有关的电源轨进行编程。

TPS650860 经由 I2C 接口进行控制,因此可通过嵌入式控制器或相关 SoC 管理器实现简单的控制。这种电源管理 IC 具有领先的控制灵活性。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

直接数字合成技术(DDS)

基于MPY634的有效值电路设计

高压放大器将库仑计数器范围扩展至±270V

热敏电阻线性化电流限制

高压差分示波器探头有何作用?