从概念到关键指标,一文弄清PLL频率合成器那些事

品慧电子讯因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

什么是PLL频率合成器?

利用频率合成器,设计人员可以产生单一参考频率的各种不同倍数的输出频率。其主要应用是为RF信号的上变频和下变频产生本振(LO)信号。

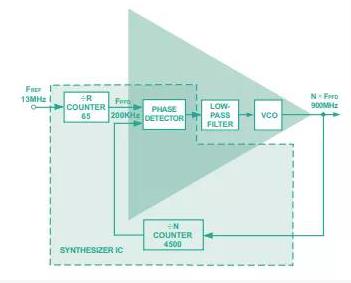

频率合成器在锁相环(PLL)中工作,其中鉴频鉴相器(PFD)将反馈频率与基准频率的某一分频形式相比较(图1)。PFD的输出电流脉冲经过滤波和积分,产生一个电压。此电压驱动一个外部电压控制振荡器(VCO)提高或降低输出频率,从而驱动PFD的平均输出接近零。

图1 锁相环(PLL)框图

频率经过计数器缩放。示例中使用了一个ADF4xxx频率合成器以及一个外部滤波器和VCO。输入基准(R)计数器将基准输入频率(本例中为13MHz)降至PFD频率(FPFD=FREF/R),反馈(N)计数器降低输出频率,在PFD处与经过缩放的基准频率相比较。达到均衡时,这两个频率相等,输出频率N×FPFD。反馈计数器为双模预分频器类型,具有A计数器和B计数器(N=BP+A,其中P为预分频值)。

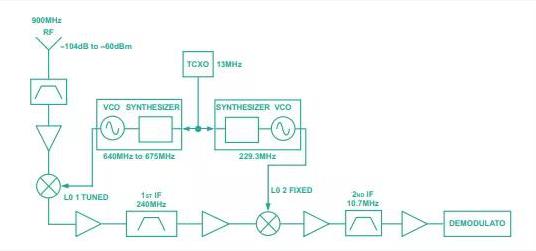

图2显示了频率合成器在超外差式接收机中的典型应用。基站和手机LO是最常见的应用,此外在低频时钟发生器(ADF4001)、无线LAN(5.8GHz)、雷达系统和防撞系统(ADF4106)中,频率合成器也有用武之地。

图2 用来将GSM RF混频降至基带的双路PLL

选择PLL频率合成器时有哪些关键性能参数需要考虑?

相位噪声

对于给定功率水平的载波频率,频率合成器的相位噪声为载波功率与规定频率偏移(对于频率合成器通常为1KHz)处1-Hz带宽上的功率之比。带内(或近载波)相位噪声主要取决于频率合成器,单位为dBc/Hz;VCO噪声贡献在闭环中被高通滤波滤除。

参考杂散

是内部计数器和以PFD频率工作的电荷泵所产生的在离散偏移频率上出现的频率成为。电荷泵产生的不匹配高低电流、电荷泵泄露以及电源去耦不充分均会增加这种杂散。杂散音会混合在所需信号之上,降低接收机的灵敏度。

锁定时间

PLL的锁定时间是指它从一个指定频率跳跃到给定频率公差内的另一个指定频率所需的时间。跳跃大小一般由PLL在所分配的频带内工作时必须完成的最大跳跃决定。GSM-900的步进大小为45MHz,GSM-1800的步进大小为95MHz。要求的频率公差分别为90Hz和180Hz。PLL必须在不到1.5个时隙内完成所需的频率步进,每个时隙为577μs。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

通过转移到SiC技术来获得暖通空调更佳的SEER等级

如何选择合适可编程交流电源

控制电源启动及关断时序

直接数字合成技术(DDS)

基于MPY634的有效值电路设计