使用CD4007阵列构建CMOS逻辑功能

品慧电子讯本实验活动的目标是使用CD4007晶体管阵列构建各种CMOS逻辑功能。CD4007包含三对互补的NMOS和PMOS晶体管。

使用CD4007晶体管阵列构建反相器

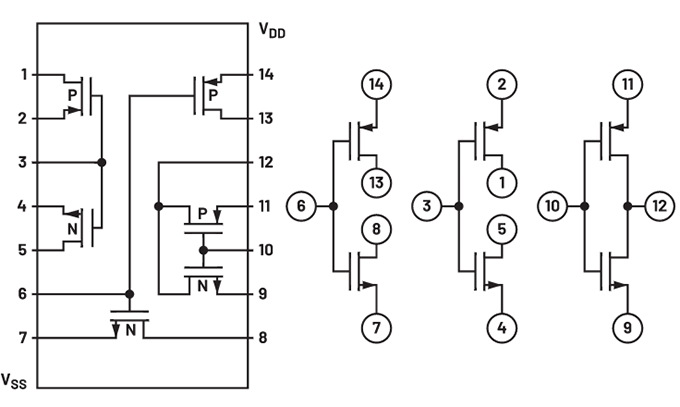

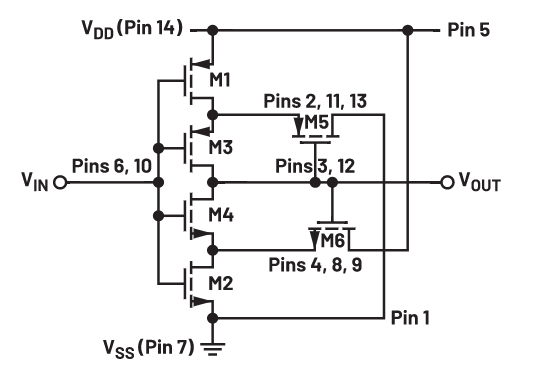

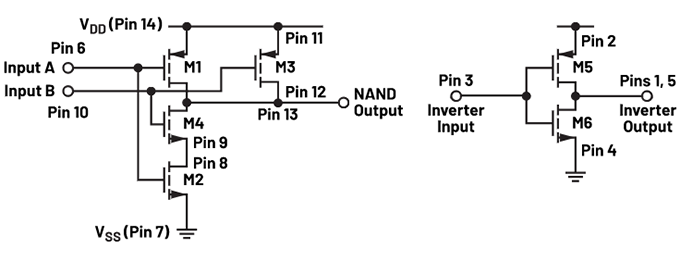

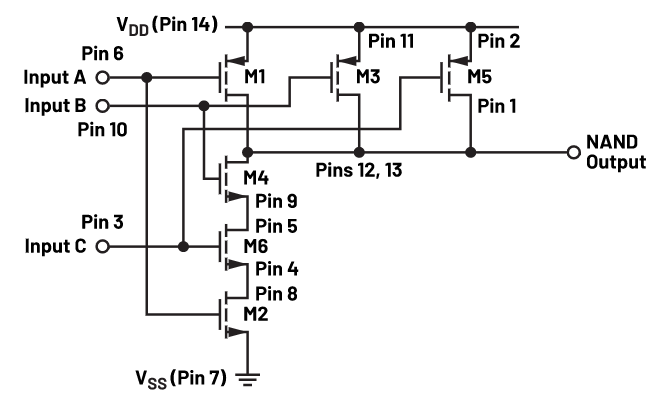

图1显示了CD4007的原理图和引脚排列。

图1. CD4007 CMOS晶体管阵列引脚排列

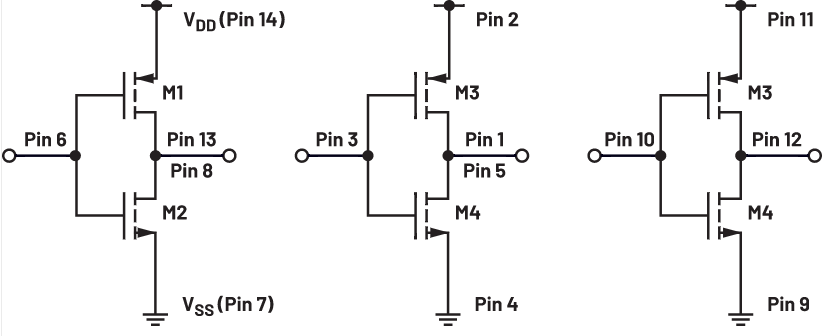

多达三个单独的反相器可由一个CD4007封装阵列构建而成。第一个配置最简单,如图2所示,将引脚8和13连接在一起作为反相器输出即可构建。引脚6将作为输入端。确保将引脚14(VDD)连接到电源,引脚7(VSS)连接到地。

图2. 三个反相器

第二个反相器是通过将引脚2连接到VDD 且将引脚4连接到 VSS来构建的。引脚1和5连接在一起作为输出,引脚3作为输入。第三个反相器是通过将引脚11连接到VDD且将引脚9连接到VSS来构建的。引脚12为输出,引脚10为输入。

CMOS反相器特性表征

CMOS反相器有许多静态(DC)和动态(AC)性能特性,这些参数通常会固定的并需要测量。本部分我们将测量反相器的若干特性,但其他类型的门电路也可进行相同的测量,本次活动的后面部分 会予以说明。我们将从静态特性开始,包括阈值电压、跃迁区域宽度、输出源和灌电流。

阈值电压

通常,CMOS制造工艺经过特别设计,使得NMOS和PMOS器件的阈值电压VTH大致相等,即互补。然后,反相器的设计人员调整NMOS和PMOS器件的宽长比W/L,使其各自的跨导也相等。

说明

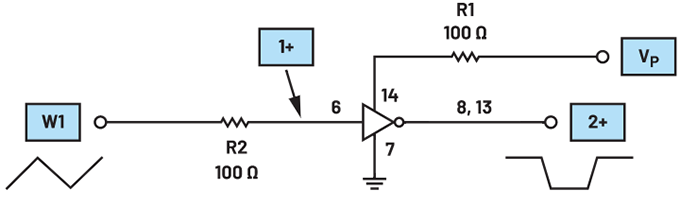

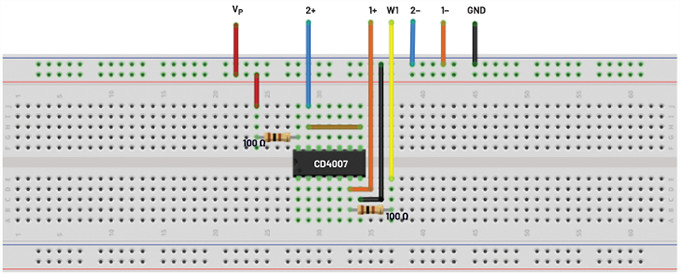

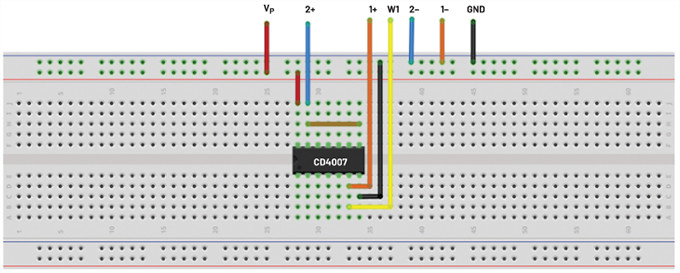

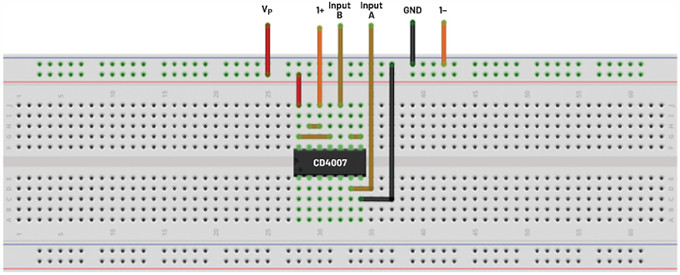

在无焊试验板上构建图2所示的第一个反相器,以测试CMOS反相 器的输入到输出开关特性。图3中的蓝色框表示ADALM2000上的连接器所需进行的连接。通过100Ω电阻将 VP((5 V)电源连接到 VDD (引脚14)以测量电源电流,并接地至VSS (引脚7)。将波形发生器的输出端连接到反相器输入端(引脚6)以及示波器输入端1+,并将反相器输出端(引脚8和13)连接到示波器输入端2+。将未使用的示波器负输入端(1-、2-)接地通常也是一个好办法。

图3. 测量输入阈值和跃迁区域的设置

硬件设置

配置波形发生器生成100 Hz三角波,峰峰值幅度为5 V,偏移为2.5 V。两个示波器通道均应设置为1 V/div。将示波器配置为XY模式,水平轴为通道1,垂直轴为通道2。

图4. 测量输入阈值和跃迁区域的试验板连接设置

程序步骤

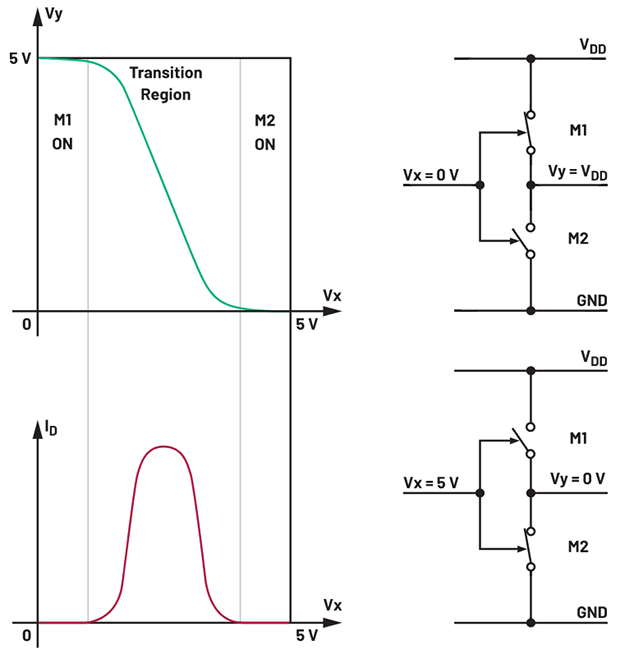

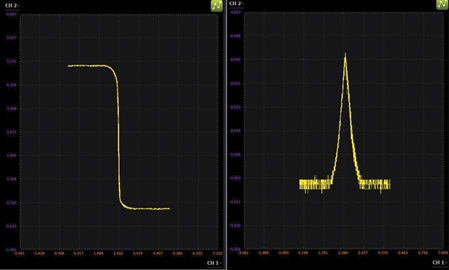

首先使用示波器通道2测量反相器输出电压与输入的关系;输入扫描范围为0 V至5 V,获得类似图5上方所示的曲线。

接着移动通道2示波器输入端2+和2-,以测量图3中100Ω电阻R1上的电压。您可能需要调整通道2的垂直刻度,以便获得电流波形的最佳视图。现在,输入从0 V扫描到5 V,获得ID与输入的关系图。这应当与图5中的底部曲线非常相似。

图5. 反相器输出电压和电源电流曲线与输入电压的关系

图6. Scopy屏幕截图:反相器输出电压和电源电流曲线与输入电压的关系

输入到输出传递特性图显示了输出电压VOUT与输入电压VIN的关 系。请注意,当输入电压从0 V增加到5 V时,输出电压从5 V降低到0 V。电源电流特性图显示了流经VDD和地之间晶体管的电流与输入电压VIN的关系。当输入电压接近地和 VDD时,特性曲线有两部分,并且VDD和地之间没有电流流动,这些情况很有吸引力,因为在此阶段没有功耗。这就是为什么如今几乎所有的数字电路都采用CMOS技术构建的原因。

作为电源的一小部分,跃迁区域宽度会产生通常称之为噪声容限的性能度量,即输出保持在恒定高或低电平下的部分输入范围。考虑到噪声可能叠加于输入信号上,因此希望输出不会响应小的输入变化。窄跃迁区域也可能减少输出在状态之间转换的时间量,从而降低NMOS和PMOS晶体管部分导通时的直通电流。

动态性能

本部分我们将研究CMOS反相器的动态特性,即反相器在输入信号从低电压切换到高电压或从高电压切换到低电压时的行为以及相关功耗。

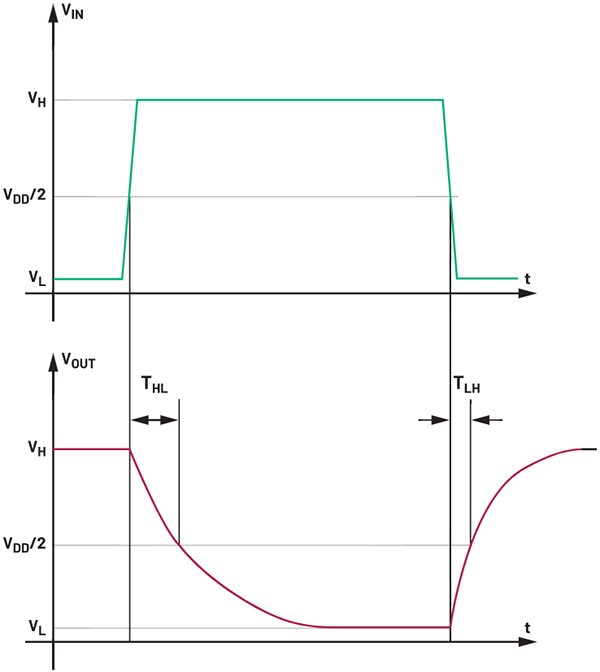

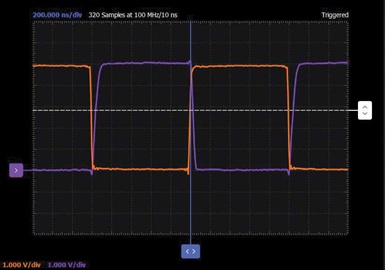

现在我们考虑由电压脉冲驱动的CMOS反相器。典型输入/输出波形如图5所示。反相器的动态行为延迟特性由两个传输延迟时间THL和TLH给出,如图7所示。请注意,这些传播时间根据中间电源电压VDD/2指定。

图7. CMOS反相器传输延迟

图8. CMOS反相器上升/下降时间

硬件设置

现在配置波形发生器生成500 kHz方波,峰峰值幅度为5 V,偏移为2.5 V。务必重新连接示波器通道2以测量输出电压波形。两个示波器通道均应设置为每格1 V。调整水平刻度,以便查看输入和输出波形的上升沿和下降沿,如图7和8所示。

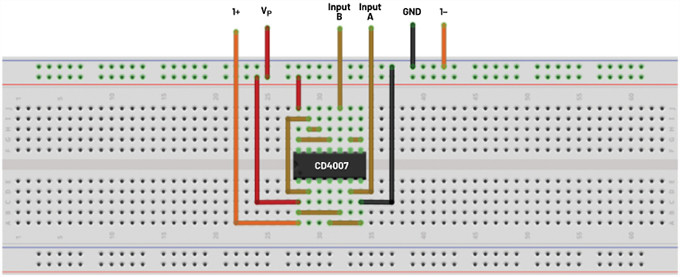

图9. CMOS反相器试验板连接

程序步骤

配置示波器通道1和通道2以捕获输入和输出信号的几个周期。图10为Scopy波形图示例。

图10. Scopy屏幕截图:CMOS反相器传输延迟

测量

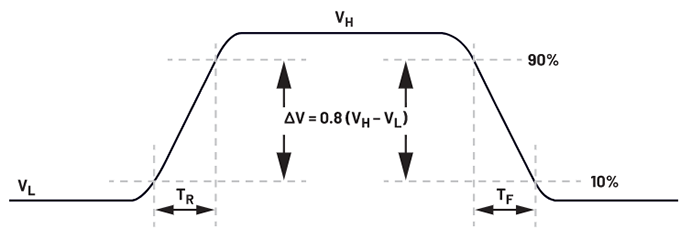

传输延迟THL和TLH = 输入跃迁(当 VIN = VDD/2时)与输出跃迁(当 VOUT = VDD/2时)之间的时间。上升时间TR = 波形从稳态值的10%升至90%所需的时间。下降时间TF = 波形从稳态值的90%降至10%所需的时间。

使用CD4007晶体管阵列构建CMOS施密特触发器

说明

施密特触发器的输入端(如图11所示)连接到四个堆叠器件的栅极。上面两个输入端连接PMOS,下面两个输入端连接NMOS。晶体管M5和M6用作源极跟随器,通过将输出电压VOUT反馈到两个NMOS和两个PMOS器件之间的两个堆叠中间点来引入滞回。

图11. CMOS施密特触发器电路

当 VIN 为0 V时,晶体管M1和M3导通,而M2、M4和M5关断。由于VOUT 为高电平,因此M6导通并充当源极跟随器,而M2的漏极(也是M4的源极)位于VDD至VTH。如果输入电压上升至高于地一个阈值的水平,则晶体管M2开始导通,M2和M6均会接通以形成分压器 网络,以约一半的电源电压对M4源极进行偏置。当输入比1/2VDD高一个阈值时,M4开始导通且即将再次切换。输入端的任何额外电压都会导致VOUT下降。当VOUT下降时,M6的源极跟随其栅极,即VOUT。M6在与M2形成的分压器中的影响迅速减弱,使VOUT 进一步下降。同时,M5已开始导通,其栅极通过快速下降的VOUT变为低电平。处于导通状态的M5使M3源极变为低电平并关断M3。在M3关断的情况下,VOUT 会一直骤降到地。当通过源极跟随器晶体管的正反馈导致通过堆叠的环路增益大于1时,会发生咬合动作。当输入再次变为低电平时,堆叠上部会发生类似过程,并且当达到阈值下限时会发生咬合动作。

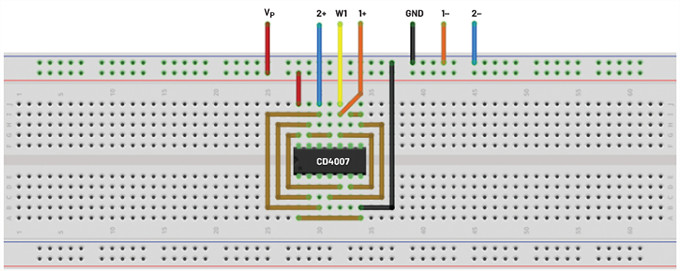

硬件设置

在无焊试验板上,构建图11所示的施密特触发器电路以测试输入到输出开关特性,就像使用普通反相器所做的那样。

配置波形发生器生成1 kHz三角波,峰峰值幅度为5 V,偏移为2.5 V。两个示波器通道均应设置为每格1 V。将示波器配置为XY模式,水平轴为通道1,垂直轴为通道2。

图12. CMOS施密特触发器电路试验板连接

程序步骤

使用示波器通道2测量输出电压与输入的关系;输入扫描范围为0 V至5 V,与使用简单反相器一样,可得到一个波形图。

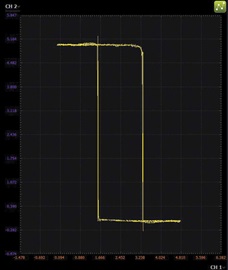

图13. CMOS施密特触发器Scopy图

使用CD4007晶体管阵列制作NAND/AND门

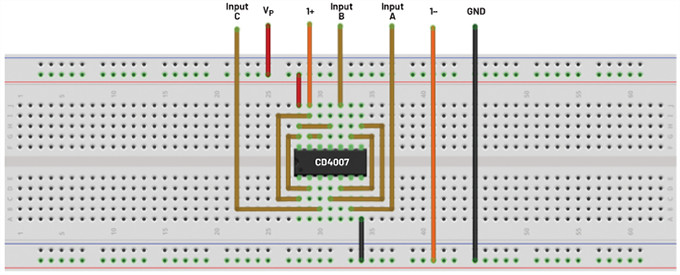

如图14所示,一个2路输入NAND门和一个反相器可由一个CD4007封装阵列构建而成。通过将引脚12和13连接在一起作为NAND输出端来配置NAND门,如图14所示。引脚14和引脚11连接到VDD以获得电源,引脚(VSS)连接到地。应将引脚9连接到引脚8以构成NAND门的N侧。引脚6将作为A输入端,引脚10将作为B输入端。

图14. 2路输入NAND和反相器

图15. 2路输入NAND试验板连接

图16. 2路输入AND试验板连接

该反相器是通过将引脚2连接到VDD且将引脚4连接到VSS来构建的。 引脚1和5连接在一起作为输出,引脚3作为输入。将引脚12和13上的NAND输出端连接到引脚3上的反相器输入端来构建AND门。

使用所有6个器件可构建单个3路输入NAND门,如图17所示。

说明

同时构建2路输入和3路输入NAND门,并通过填写各自真值表来确认其逻辑功能。还可以通过将未使用的输入端连接到VDD来测量每个输入端的输入阈值电压,正如对简单反相器所做的那样。

图17. 3路输入NAND门

图18. 3路输入NAND试验板连接

问题

能否说出并描述可以使用CD4007阵列构建的其他类型的逻辑功能?

您可以在 学子专区论坛上找到问题答案。

来源:ADI

作者:Doug Mercer 和 Antoniu Miclaus