碳化硅功率晶体的设计发展及驱动电压限制

品慧电子讯当在音频范围内的频率下工作时,某些表面贴装电容器会表现出噪声。最近的设计使用10μF,35V X5R 1206陶瓷电容器,该电容器会产生明显的声音噪声。要使这样的板静音,可以使用Murata和Kemet等制造商的声学静音电容器。

传统上在高压功率晶体的设计中,采用硅材料的功率晶体要达到低通态电阻,必须采用超级结技术(superjunction),利用电荷补偿的方式使磊晶层(Epitaxial layer)内的垂直电场分布均匀,有效减少磊晶层厚度及其造成的通态电阻。但是采用超级结技术的高压功率晶体,其最大耐压都在 1000V 以下。如果要能够耐更高的电压,就必须采用碳化硅材料来制造功率晶体。以碳化硅为材料的功率晶体,在碳化硅的高临界电场强度之下,即使相同耐压条件之下,其磊晶层的厚度约为硅材料的 1/10,进而其所造成的通态电阻能够有效被降低,达到高耐压低通态电阻的基本要求。

在硅材料的高压超级结功率晶体中,磊晶层的通态电阻占总通态电阻的 90%以上。所以只要减少磊晶层造成的通态电阻,就能有效降低总通态电阻值;而碳化硅功率晶体根据不同耐压等级,通道电阻(Channel resistance, Rch)占总通态电阻的比值也有所不同。

例如在 650V 的碳化硅功率晶体中,通道电阻( Channel resistance,Rch)占总通态电阻达 50%以上,因此要有效降低总通态电阻最直接的方式就是改善通道电阻值。 由通道电阻的公式,如式(1)可以观察到,有效降低通道电阻的方法有几个方向:减少通道长度 L、减少门极氧化层厚度 dox、提高通道宽度 W、提高通道的电子迁移率 μch、降低通道导通阈值电压 VT,或者提高驱动电压 VGS。然而几种方法又分别有自身的限制。

1.减少通道长度 L,就必须考虑 DIBL 效应

2.减少门极氧化层厚度 dox,会造成门极氧化层的可靠度问题

3.提高通道宽度 W,必须增加功率晶体的面积,使成本增加

4.提高驱动电压 VGS,会造成门极氧化层的可靠度问题

5.降低通道导通阈值电压 VT,会造成应用上可能的误导通现象

6.提高通道的电子迁移率 μch来改善功率晶体的通道通态电阻,但是必须从晶体平面

(crystal plane)选用及制程上着手

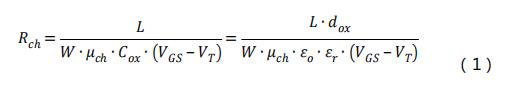

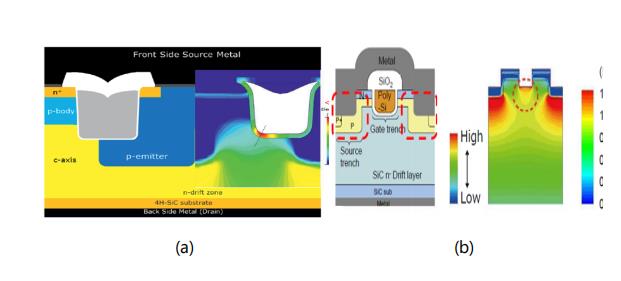

实际上利用提高通道的电子迁移率 μch来改善功率晶体的通道通态电阻,不仅是从制程上做调整,更是从晶体平面的选择上做出选择。在目前已量产的增强型碳化硅功率晶体的晶粒(die)结构来看,大致上可以分为二种,平面式(planar)以及沟槽式(trench),如图 1 所示。

图 1 碳化硅功率晶体的结构:(a)平面式(b)沟槽式

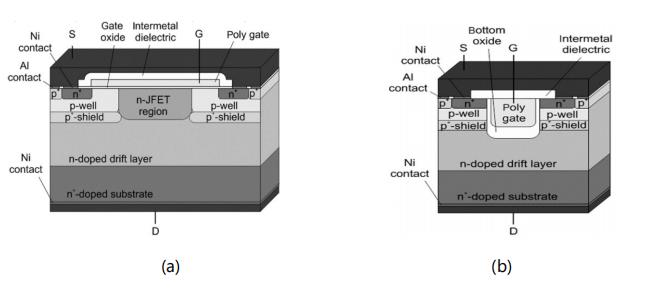

这两种不同形式的结构差异不仅仅在于是否以内嵌的形式制造而成,更主要的差异在于功率晶体的通道是由不同的碳化硅晶体平面制成。硅材料是由纯硅所组成,但是碳化硅材料会依照不同的原子排列而有着不同的晶体平面。传统上平面式结构会采用<0001>的硅平面(Si-face)制作通道,而沟槽式结构功率晶体采用<1120>的晶体平面做为功率晶体的通道,根据实测结果,采用<1120>晶体平面时能够有效利用其较高的电子迁移率,达到低的通态电阻。

图 2 (a)碳化硅功率晶体的晶体平面(b)沟槽式功率晶体采用的晶体平面

(c)<1120>晶体平面的高电子迁移率

值得一提的是,在平面式碳化硅功率晶体制造通道采用的<0001>硅平面中,受到晶体缺陷程度较高,造成电子迁移率较低及产生较高的通道电阻。要克服这个问题,在设计上会使用较薄的门极氧化绝缘层,使其具有较低的门极阈值电压(~2V),进而降低通道电阻,这也是平面式结构功率晶体的特征之一。在实际应用时,会建议用户在设计驱动电路时,截止时驱动电压采用负电压,以避免驱动时的错误操作造成功率晶体烧毁。反之,在沟槽式结构的碳化硅功率晶体因其具有较高的门极阈值电压(>4V),无论哪一种电路结构,都不需要使用负电压驱动。

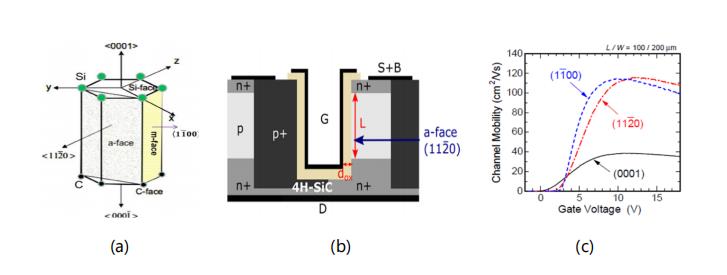

如上所述,碳化硅材料具有高临界电场强度,采用碳化硅做为高压功率晶体材料的主要考量之一,是在截止时能够以硅材料 1/10 的磊晶层厚度达到相同的耐压。但在实际上功率晶体内的门极氧化绝缘层电压强度,限制了碳化硅材料能够被使用的最大临界电场强度,这是因为门极氧化绝缘层的最大值仅有 10MV/cm。按高斯定律推算,功率晶体内与门极氧化绝缘层相邻的碳化硅所能使用的场强度仅有 4MV/cm,如图 3 所示。碳化硅材料的场强度越高,对门极氧化绝缘层造成的场强度就越高,对功率晶体可靠度的挑战就越大。因此在碳化硅材料临界电场强度的限制,使功率晶体的设计者必须采用不同于传统的沟槽式功率晶体结构,在能够达到更低碳化硅材料场强度下,尽可能减少门极氧化绝缘层的厚度,以降低通道电阻值。在可能有效降低碳化硅材料临界电场强度的沟槽式碳化硅功率晶体结构,如英飞凌的非对称沟槽式(Asymmetric Trench)结构或是罗姆的双沟槽式(Double

trench)结构,都是能够在达到低通态电阻的条件之下,维持门极氧化绝缘层的厚度,因门极氧化绝缘层决定了它的可靠度。

图 3 门极氧化层场强度限制了功率晶体内碳化硅材料的场强度

图 4 碳化硅功率晶体结构

(a)英飞凌的非对称沟槽式结构 (b)罗姆的双沟槽式结构

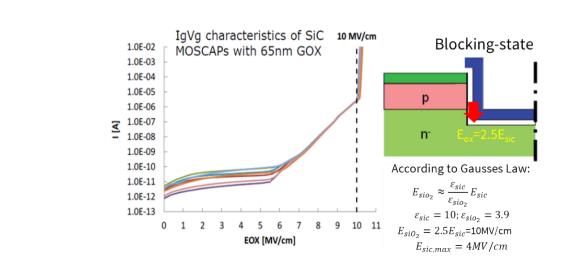

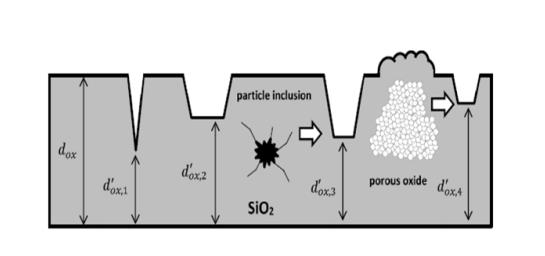

门极氧化绝缘层的电场强度挑战不仅来自碳化硅材料的影响,也来自门极氧化绝缘层它本身。硅材料在被制造半导体的过程中经过蚀刻及氧化作用,可以产生厚度相对均匀、杂质少的门极氧化层。但在碳化硅材料经过蚀刻及氧化作用后,除了产生门极氧化绝缘层外,尚有不少的杂质及碳,这些杂质及碳会影响门极氧化层的有效厚度及碳化硅功率晶体的可靠度,如图 5 所示。

图 5 碳化硅门极氧化绝缘层受杂质影响造成有效厚度改变

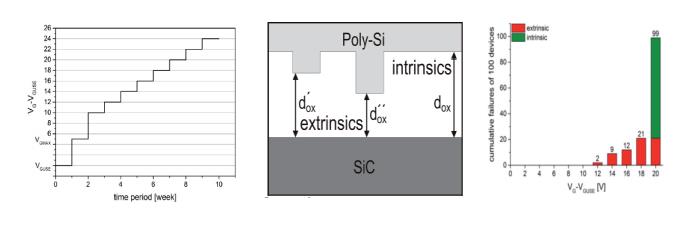

考虑到门极氧化层厚度对碳化硅功率晶体可靠度的影响,在门极氧化层的设计上必需考虑这些可能影响门极氧化层有效厚度的因素。除了采用更厚的门极氧化层设计以提高碳化硅的可靠性之外,还要针对门极氧化层进行远超出额定门极电压的长时间电压测试。如图 6 所示,VGUSE是门极电压建议值,VGMAX 是额定门极电压最大值,随着时间推移增加门极电压值,直到所有的功率晶体门极都烧毁失效。 采用这样的门极测试,可以检测出门极氧化层会在不同的电压下产生失效。一般来说,在较低电压下失效是由于上述杂质造成有效门极厚度减少的外在缺陷(extrinsic defect);而在较高电压下的失效被称为本质缺陷(Intrinsic defect)),是来自 F-N 隧穿效应(Fowler-Nordheim tunneling)的作用,或是门极氧化层超过其最大电场 10MV/cm。

图 6 碳化硅门极氧化层可靠度测试及其本质缺陷及非本质缺陷示意图

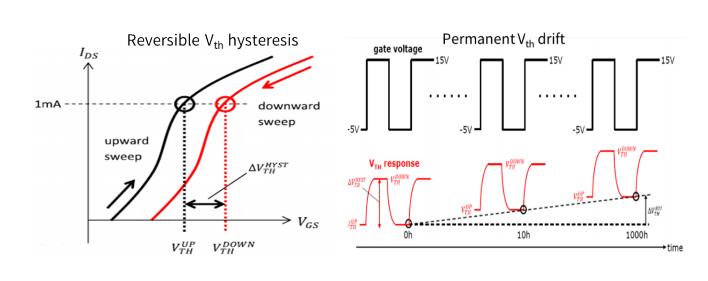

碳化硅功率晶体的另一项设计挑战就是门极阈值电压的不稳定性(threshold voltageinstability)。门极阈值电压的不稳定性,会影响碳化硅功率晶体的可靠度。如果碳化硅功率晶体的阈值电压往上,会造成功率晶体的通态电阻值及导通损耗增加;反之,如果碳化硅功率晶体的阈值电压往下,会造成功率晶体易产生误导通而烧毁。门极阈值电压的不稳定性有两种现象,可回复型阈值电压滞后作用(Reversible threshold voltagehysteresis) 及不可回复型的阈值电压漂移(threshold voltage drift);门极阈值电压的不稳定性来自于门极氧化层及碳化硅的介面间存在缺陷(trap),如同对介面间的电容进行充放电,而门极电压驱动过程造成电子或电洞被捕获,从而形成阈值电压的滞后作用。

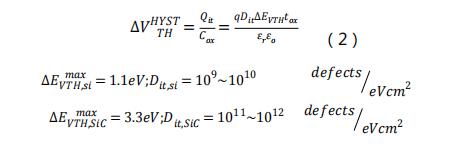

图 7 碳化硅功率晶体门极阈值电压的滞后作用及偏移

如式(2),阈值电压滞后作用是由门极氧化层接面的缺陷密度(Density of defect)及材料的带隙(bandgap)所决定。相比于硅材料,碳化硅的材料缺陷密度比硅材料缺陷密度高 1000~10000 倍;而碳化硅的带隙约为硅的 3 倍,因而造成碳化硅功率晶体的阈值电压滞后作用在未经处理之前,高达数伏特(V)之多,而硅材料只有数毫伏特(mV)。这也是电源供应器设计者在使用碳化硅功率晶体时所必须注意的考量重点之一。

碳化硅功率晶体在门极氧化层及碳化硅之间的电荷分布可简单化区分为固定式电荷(