为什么高速信号ESD设置要flow-through

品慧电子讯目前的芯片工艺越来越精密,主IC都到纳米级别了,具有极薄光刻技术和极易受到 ESD 影响的栅极氧化物的先进技术,所以IC的防静电能力主要是保护自身在生产运输和安装过程中不受损坏。

防静电需求

目前的芯片工艺越来越精密,主IC都到纳米级别了,具有极薄光刻技术和极易受到 ESD 影响的栅极氧化物的先进技术,所以IC的防静电能力主要是保护自身在生产运输和安装过程中不受损坏。

其次具有高元件密度的 PCB 的集成电子板有助于 ESD 耦合和传播,所以整机中ESD现象时常发生。

为什么IC 制造商不愿意制造强大的嵌入式 ESD 保护二极管,因为它们需要大量先进且昂贵的技术的有效面积,防静电不同于别的芯片工艺,静电瞬间电流有数十安培,必须通过有效的芯片面积来防护,不是尖端工艺能解决的。

高速信号芯片防静电特点

ESD 保护器件的寄生电容必须足够低,以允许高速信号传输而不会降级。

ESD 保护器件的高寄生电容会增加过多的信号上升/下降时间并阻止通信,从而丢包。

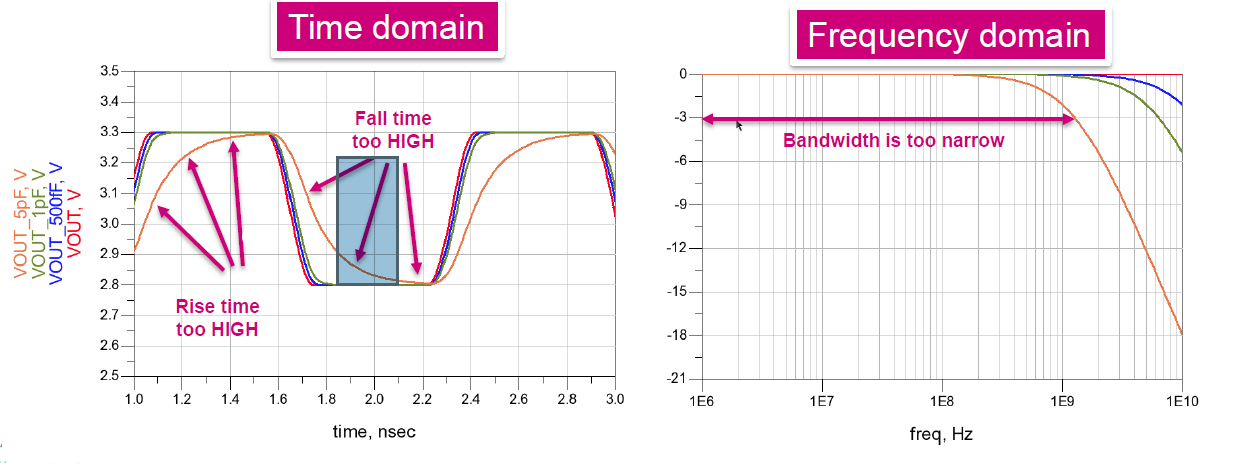

以下是以电容置于高速信号线对信号的影响图形。

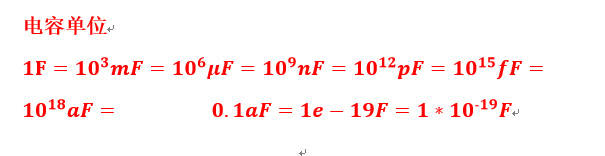

很多人不清楚这个电容的换算,也可以参考下面的图片

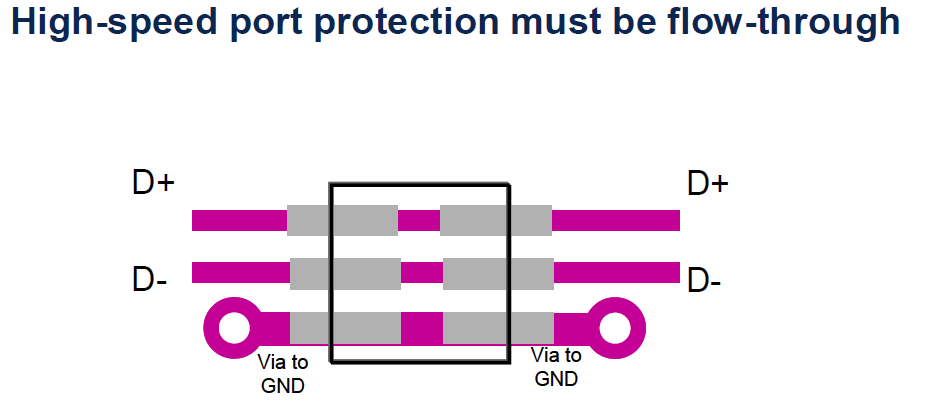

如何保证线路上的寄生电容足够小,而且走线也不影响差分信号阻抗匹配?

首先要选择电容足够小的ESD器件,其次是要合理布线。

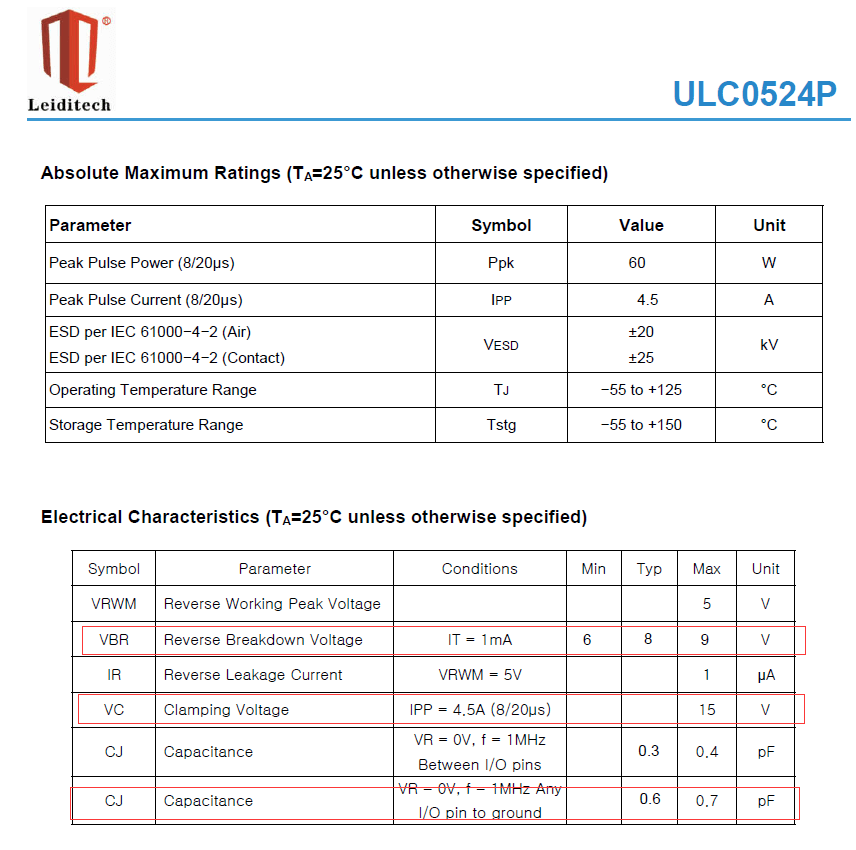

在尽可能情况下,选择DFN封装的ESD器件,如雷卯电子ULC0524P ULC0511CDN这类超低电容的器件。

如何看懂ESD器件参数?

一般入门级只要看懂动作电压Vbr,电容Cj,箝位电压Vc即可。

以下规格书为示例。

DFN封装技术越来越成熟,封装速度快,体积小,雷卯提供了越来越多的防静电DFN封装器件,DFN1006 DFN1610 DFN2020 DFN1616 DFN2010 DFN2510 DFN3310 等,最多支持10路的高速信号静电保护。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

原边与副边调节

Digi-Key开售来自Renesas和Dialog的五种新型强大产品组合

符合IEPE标准的CbM机器学习赋能平台

带eMotion智能电机控制和备用电池的MPS开源急救呼吸机

用集成补偿网络来评估降压稳压器的瞬态性能