分享高效率宽电压输出之小型化电源方案

高功率密度电源设计一直为电源界最热门的议题,近年来各式消费型产品文宣着墨在小型化与轻量化的设计。随着半导体材料与制程的进步,或是突发其来的机构设计灵感,让我们能持续见证电源尺寸不断地突破即有限制,完成不可能的任务。

高功率密度电源设计一直为电源界最热门的议题,近年来各式消费型产品文宣着墨在小型化与轻量化的设计。随着半导体材料与制程的进步,或是突发其来的机构设计灵感,让我们能持续见证电源尺寸不断地突破即有限制,完成不可能的任务。

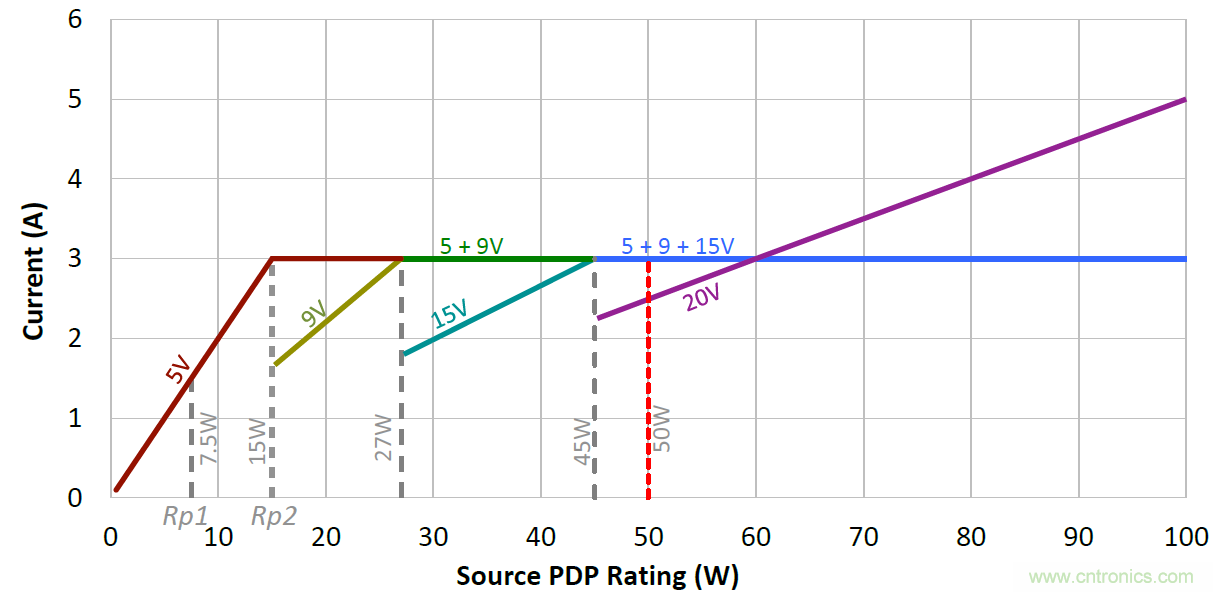

当下电源产业受惠于消费者对于高速网路、运算速度与高画质的追求,系统用电量增加造就新的市场需求,新系统亦配载更高的蓄电力用以延长使用时间,需要更高的充电功率。此外,单电压充电器在市场上已逐渐无法满足需求,因使用者可能拥有多个不同电压的智能设备,例如9V快充功能手机、15V平板电脑与20V的笔记型电脑,为减少外出便携的重量,或维持桌面整洁,消费者倾向使用支援宽电压的电源,同时Type C支援系统线材的整合,推波助澜下带动整个PD市场持续成长。目前规范下的PD电源20V最大可支援100W,可应用于高运算处理规格的笔记型电脑或中大型显示器。此高功率产品的市场需求有增加的趋势,只要电源供应75W以上就须谨守IEC 61000-3-2功率因素相关规范,即便是暂态时间为数分钟或数秒钟,而电源电路包含之功因电路 (PFC),电路架构几乎采用临界导通模式之升压转换器 (Critical Condition Mode Boost),鲜少有变化。针对PFC后端的PWM级,较少文献在此应用条件下比较架构特点,本文将与读者分享各常用架构与混成返驰式 (Hybrid Flyback) 应用于宽电压电源之优势,并分享半导体元件封装选用之概念。本文最终分享一100W小型化PD电路平台采用混成式返驰式架构,提供读者参考。

图1、USB PD规范电流与功率对应图[1]

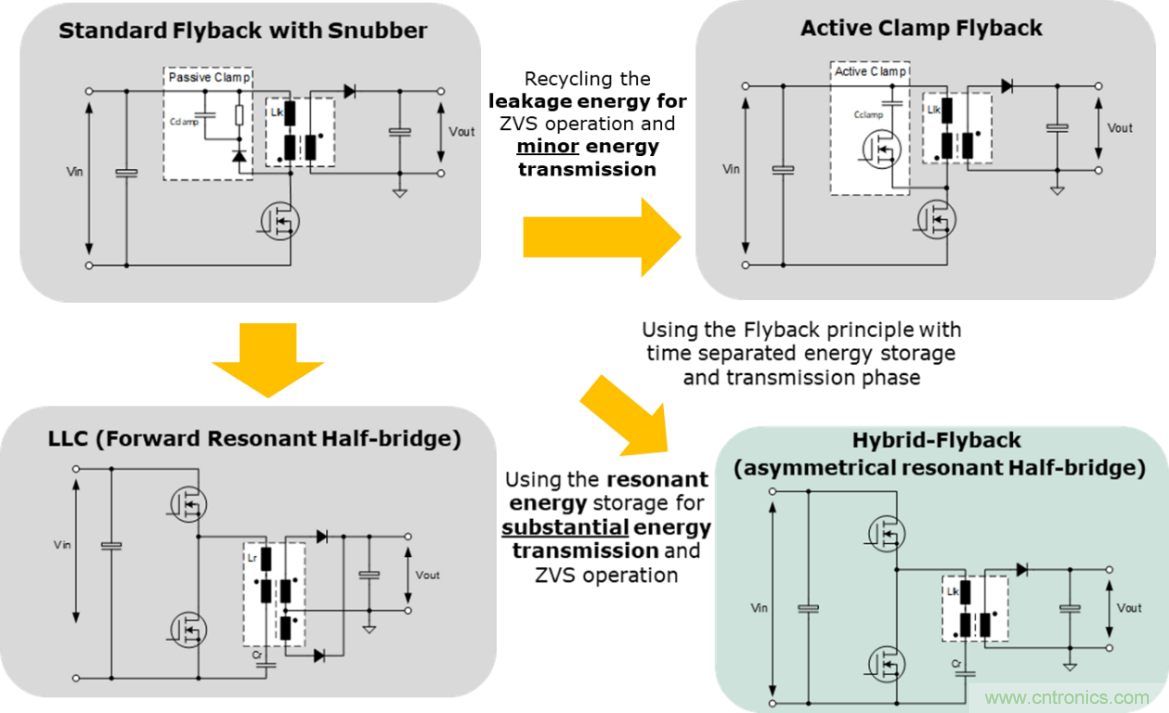

关于高效率DC-DC转换器,一般设计直觉会联想到半桥谐振转换器,在业界方案也较为纯熟。然而,针对宽范围输出的应用,若以LLC(图2右上)设计可支援广范围电压增益的谐振槽,除了采用相对漏感于激磁电感的比例较大的设计方式,或是采用常见于LED照明的LCC架构 [2],可降低输出输出电压范围内的频率变化,但增加磁性元件成本与初级导通损耗仍使产品应用受限。回归至效率优化后的LLC架构,在输出端增加一降压转换器可支援宽电压输出,并在输出满电压条件下旁路降压转换器,在此条件下可取得高效率,但此举也会增加电路空间与零件数量,使功率密度无法最佳化。故当今PD应用首选之架构仍多以返驰式为主。

回归到传统型返驰式架构(图2左上)普遍应用于宽电压输出,若要进一步提升电路效率,必须有漏感能量回收机制,将漏感能量转移至谐振电容或输入端,而转换器须藉由启始的负向电流达成零电压切换(ZVS,Zero voltage switching)以降低开关切换损耗,因此电路拓朴将有2个开关元件。主动位箝位型返驰式转换器(ACF,Active-Clamp Flyback) (图3右上)相较于传统返驰式转换器增加上臂开关,其提供路径将回收漏感能量之电容透过变压器导引至变压器次级侧,并且上臂与下臂开关导通前之初始状态为负电流,开关皆可达成零电压切换。

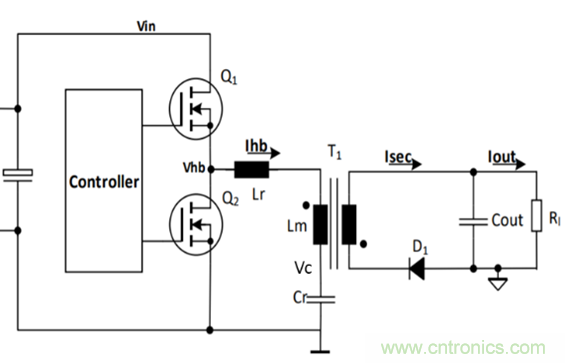

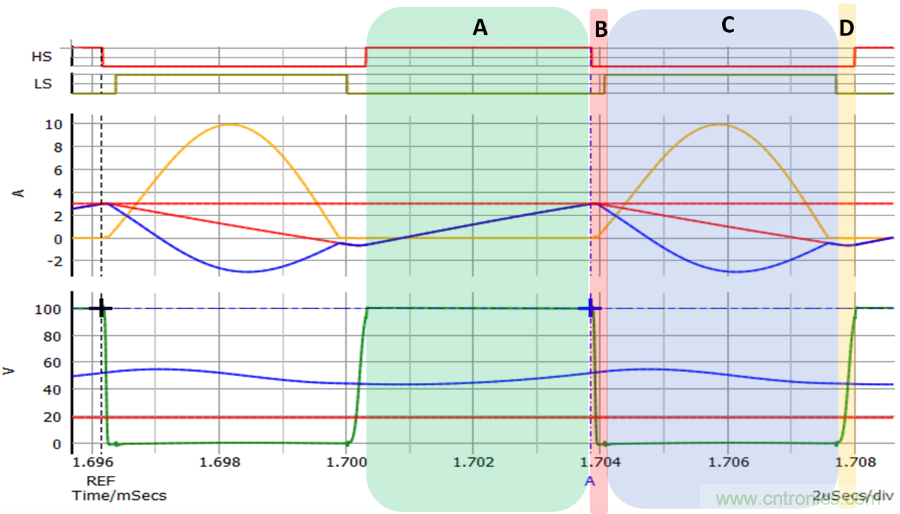

图3右下方架构属于半桥的一种,其主开关位置连接至输入端母线电压,谐振电容则与变压器串联,初级侧看起来近似于LLC架构,次级侧与返驰式转换器同为单边绕组。此架构在业界较为少见,动作原理如下(图3):

上臂开关导通,启始电流为负向,此延续上周期达到零电压导通的状态。此时变压器开始储能,犹如返驰式转换器变压器储能的机制,变压器端电压为输入电压与谐振电容电压的差值,此决定变压器电流上升的斜率。实际上电路主要为激磁电感与谐振电容共振,但由于谐振频率过低,故电流波形近似于线性上升之三角波。

上臂开关截止,变压器电流续流,使下臂开关未导通前的初始电流为负向,下臂开关达到零电压切换。

下臂开关导通,谐振电容向变压器释能同时与变压器漏感共振,故次级电流为弦式波形。直到谐振周期结束,二次侧电流截止,谐振电容则持续对激磁电感负向储能。由此周期可得知,输出电压与谐振电容电压为变压器圈数比之关系,因此输入与输出电压的关系式为:VIN/VO = N/Duty,其中N为变压器初次级的圈数比。Duty为主开关导通时间对开关周期的占比。

下臂开关截止,在上臂开关导通前负向的激磁电流协助上臂开关达到零电压切换。此阶段需求之负电流大小与选用开关的杂散电容(Coss)有关,与ACF雷同。选用Coss较小的MOSFET 或宽能隙半导体,则ZVS的能量需求较小,能更进一步降低回路上的导通损耗。

由于此架构上臂做为主开关,在导通的同时对变压器与谐振电容储能,下臂开关导通时能量传送方式则类似于LLC,故有文献将其名为Hybrid Flyback(HFB)[3]。

图2、电路架构比较图[3]

图3、 HFB简易动作原理

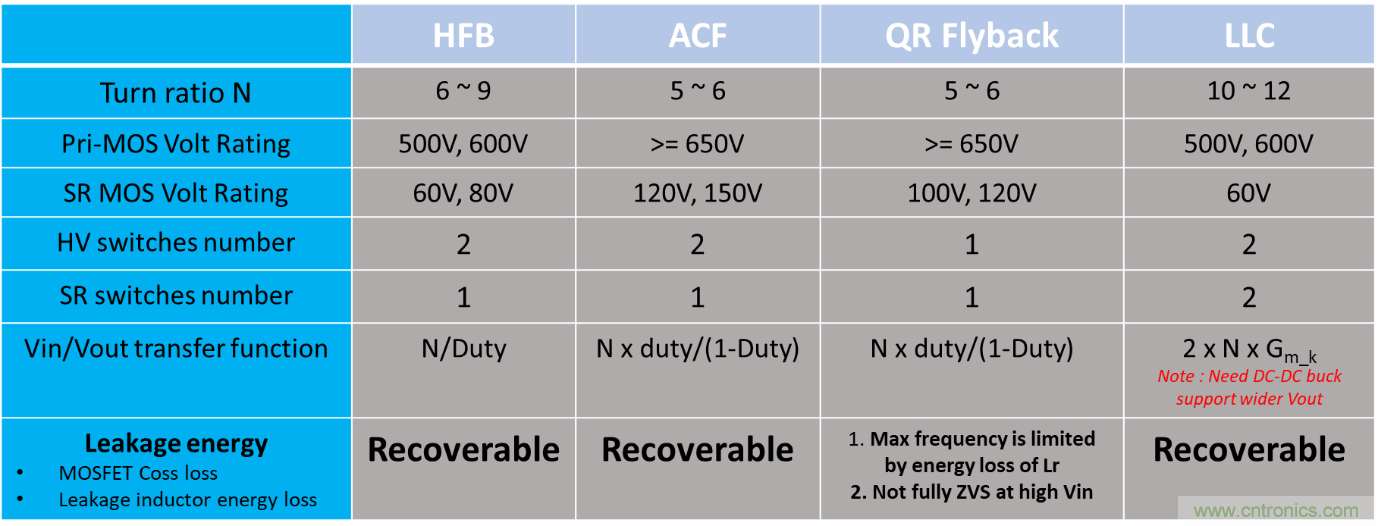

针对中大功率(>75W)之宽电压应用,下表一为架构比较包含开关元件应力,基于常用之变压器圈数比范围,输入端母线电压390Vdc,输出电压范围5V~20V。HFB适用设计为拉高变压器圈数比以降低二次侧开关电压应力,而初级开关应力仅为母线电压。此优势回馈在元件耐压的选用上,对于高压开关常用额定600V仍有足够设计裕度,无论初级或次级侧可选择更低导通电阻或低杂散电容的开关器件。

表一、架构应用比较表

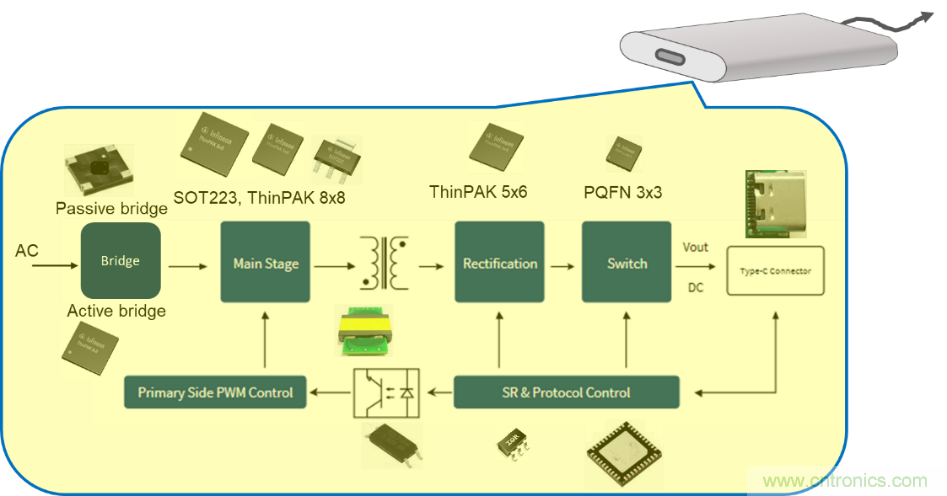

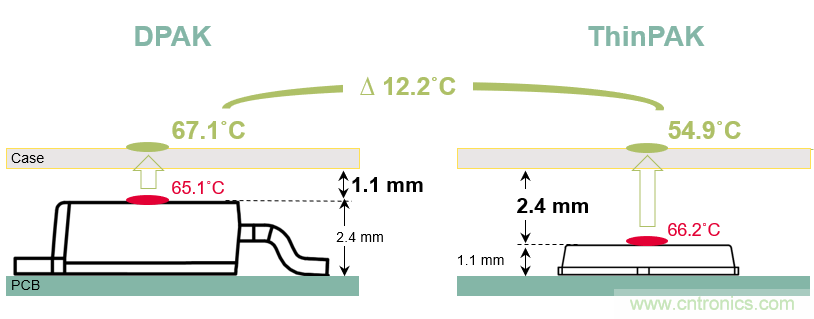

关于小型化电源内部空间分布,变压器等被动元件占大部份容积,由于高频化设计可缩小储能元件体积,部份设计者采用平面变压器有利于产品模组化与薄型化设计,也可进一步降低高频操作时的集肤效应与邻近效应带来的损耗,在消费型产品市场逐渐展露优势。其次为功率半导体封装占用的空间,随着半导体封装技术提升,可采用贴片式功率晶体较易实现薄型化电源或PCB模组化设计。支援的应用涵盖自最前端的主动式桥式整流器(Active Bridge) ,PFC电路至PWM级开关与同步整流电路,目前业界皆有通盘的对策(图4)。SMD封装ThinPAK8x8或ThinPAK5x6高度仅1mm,对于产品厚度的缩减有莫大帮助,大幅提升功率密度的百分比。此外,降低元件厚度可有效阻隔热点,间接降低产品的外壳温度,如图5为半导体封装对壳温之影响。

图4、薄型化SMD元件选用示意图

图5、TO252与ThinPAK封装对于壳温之比较示意图

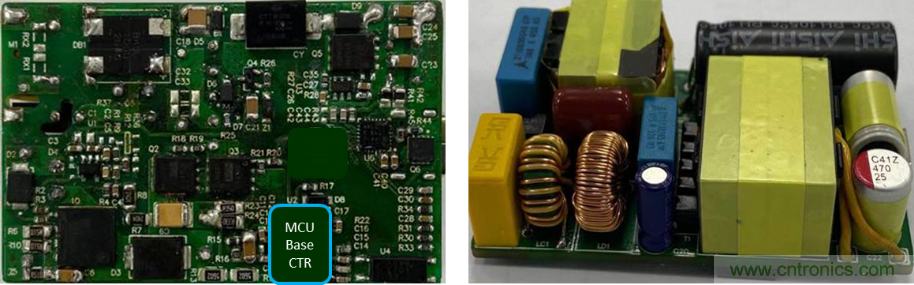

下图为一数位控制器实现之100W混成返驰式电源平台,支援5V~20V 输出,满载操作频率为190kHz。PFC控制晶片采用小型5 pin封装之IRS2505,PD控制晶片采用CYPD3174,功率半导体皆采用英飞凌之1mm之薄型化SMD封装设计:PFC 级采用ThinPAK8x8/600V/180m?,PWM级采用ThinPAK5x6/ 600V/360m?,SR开关采用ThinPAK5x6/80V/2.6m?,电源功率密度不含机构外壳与线材可达42W/inch3。实测极端条件下之90Vac满载效率最高可达92.5%。以下仍有方式可进一步提升效率,可作为未来优化性能之参考: (1) 低压AC输入条件下电路主要损耗为桥式整流二极体,若将其改为主动式 (Active Bridge) 可望提升效率至93%以上。 (2) 宽能隙半导体应用于半桥类架构可减少ZVS需求能量,间接降低初级导通损耗。

图6、以混成返驰式转换器实现100W宽范围输出电源

以上阐述混成返驰式转换器应用于宽电压范围之优势,附带SMD封装选用之经验分享。此架构亦可推广应用于LED驱动电路、支援充电功能之智能家电与其他电池充电之应用。

参考文献

[1] https://www.usb.org/document-library/usb-power-delivery

[2] https://www.edntaiwan.com/20190213ta31-achieve-wide-voltage-led-constant-current-drive/

[3] https://www.mdpi.com/2079-9292/7/12/363

(来源:英飞凌科技,作者:洪士恒,资深主任工程师)