改进的SAR模数转换器进一步扩展了设计选项

品慧电子讯今天,几乎所有的电子设计都涉及到模数转换器(ADC)。在简单的应用中,配套的MCU内的ADC可能已经足够,而极端的高频应用则需要高速ADC。其他设计需要特别注意数据转换器的类型和特性。

像模拟输入滤波器这样的设计挑战通常需要额外的时间。不要忘了像十进位这样的功能,它在一些设计中提供了好处。本文提出的建议可能有助于解决这些不同的设计考虑。

ADC的选择

目前常用的ADC有三种基本类型:delta-sigma、逐次逼近寄存器(SAR)和用于RF的每秒千兆位采样(GSPS)闪存或流水线ADC。您的应用将决定必须进行数字化的信号类型。这些是与你的设计需求相匹配的主要规格:

采样率。基本规则是,采样率必须比要数字化的信号的最高频率内容大2倍或以上。换句话说,采样率的一半的频率被称为奈奎斯特频率;它是可以被转换而不产生混叠的最高频率信号。如果不符合这个标准,就会出现混叠。混叠会产生新的信号,干扰转换过程。

分辨率。该规范定义了转换的精度。分辨率是以可以测量的最小的输入电压增量来表示的。分辨率由输出中的位数设定。位数越多,分辨率就越高。

动态范围。这是最高和最低输入电压水平之间的最大范围,以dB表示。与此规格相关的是无杂散动态范围(SFDR),它定义了最高输入振幅和本底噪声中的峰值刺痛之间的范围。

延迟。采样脉冲的启动和输出位的出现之间的时间。

影响ADC选择的其他因素是噪底和信噪比(SNR)。

在你的应用中,功耗可能是一个主要关注点。功率的使用通常与采样率成正比。

前两个因素通常在一开始就被确定下来;然后选择一个ADC架构。Δ-Σ型ADC具有最高的分辨率,其数字输出高达32位。然而,采样率通常低于每秒10兆次(MSPS)。

SAR转换器的分辨率高达18位,采样率高达125MSPS。这一中档类别适合许多应用。GSPS ADC可提供超过10 GSPS的采样率和10至14比特的分辨率,主要见于射频设备和手机等产品。

对于广泛的一般应用,如工业设备,SAR是一个不错的选择。当需要高精度时,delta-sigma ADC是一个可靠的选择。

基本设计标准

所有ADC都需要一个模拟输入滤波器。它的主要目的是将输入带宽限制在只有要被数字化的信号上。其他信号,特别是输入端的高频成分,可能会产生混叠,造成转换错误。这就需要一个低通滤波器,对所需信号中最高频率成分以上的频率进行急剧滚降。

模拟低通滤波器是有效的,但在试图实现所需的衰减时,它们可能是大而复杂的处理方式。像有限输入响应(FIR)滤波器这样的数字滤波器,有足够数量的抽头,可以提供卓越的选择性。

也许最大限度地减少输入滤波器要求的最简单方法是使用一个大大高于混叠保护所需的最小采样率。这种超采样增加了输入信号和混叠信号之间的距离,从而放松了对输入滤波器的要求。

请记住,较高的采样率对MCU、FPGA或其他接收ADC输出的电路来说可能太快了。在转换之后可以使用一个抽取滤波器来降低输出速率。取样提供了减少抗混叠滤波器要求的额外优势,因为取样电路的低通滤波器效应将降低二阶和三阶谐波。十取法还可以提高信噪比,每2个因子可提高-3dBFS(满刻度分贝)。

任何使用ADC的设计中最关键的部分是模拟前端(AFE)。除了混叠滤波器之外,大多数ADC需要一些阻抗匹配电路、偏置网络以及与ADC参考电压的连接。所有这些都必须根据你的应用进行定制。外部元件通常是必要的,因此在你的设计中要计划一些额外的PCB空间。

一个值得考虑的ADC

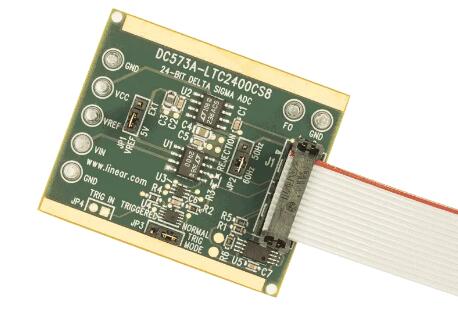

德州仪器公司提供了一系列的SAR ADC,可以与许多应用相匹配。其中一个例子是ADC364x,这是一个双通道14位CMOS器件,可以在10至65 MSPS的速率下采样(见图)。输入可以是单端或差分的。输出可以是并行或串行的,使用标准CMOS的LVDS输出。输出上的外部电阻控制电流。

一个关键特征是它的片上数字滤波器具有抽取功能。十取法有效地降低了输出数据率,从而可以容纳较慢的外部设备,如MCU或FPGA。可以选择2、4、8、16或32的十进位。

使用ADC进行设计是一个复杂的过程,需要考虑许多相互关联的因素。为寻找最佳可用的ADC而花费的时间将在以后的设计时间和成本节约中得到回报。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

芯和半导体携手罗德与施瓦茨成功举办战略合作签约仪式

数字化革新突破动力电池大规模制造化成分容瓶颈,迎接电动汽车 “黄金时代”到来

科锐结合MaxLinear线性化技术,高效赋能新型超宽带5G

Digi-Key主办FastBond设计大赛,推动互联设备创新

电动汽车先驱Arrival与安霸联合推出高级驾驶辅助系统

要采购滤波器么,点这里了解一下价格!