用于高频接收器和发射器的锁相环——第三部分

品慧电子讯本系列第一部分介绍了锁相环(PLL),说明了其基本架构和工作原理。 另外举例说明了PLL在通信系统中的用途。 在第二部分中,我们详细考察了相位噪声、参考杂散、输出漏电流等关键性能规格,还考虑了它们对系统性能的影响。 在本部分中,我们将考察PLL频率合成器的主要构建模块。 我们还将比较整数N和小数N架构。 最后将总结市场上现有的VCO,同时列出ADI的现有频率合成器系列。

PLL频率合成器可以从多个基本构建模块的角度来考察。 我们在前面已经提到过这个问题,下面将更加详细地进行探讨:

鉴频鉴相器(PFD)

参考计数器(R)

反馈计数器(N)

鉴频鉴相器(PFD)

频率合成器的核心是鉴相器,也称鉴频鉴相器。 在鉴相器中,将比较参考频率信号与从VCO输出端反馈回来的信号,结果得到的误差信号用于驱动环路滤波器和VCO。 在数字PLL (DPLL)中,鉴相器或鉴频鉴相器是一个逻辑元件。三种最常用的实现方法为:

异或(EXOR)栅极

J-K触发器

数字鉴频鉴相器

这里,我们只考虑PFD,这也是ADF4110和ADF4210频率合成器系列中使用的元件,因为与EXOR栅极和J-K触发器不同,处于解锁状态时,其输出为频差以及两个输入间相差的函数。

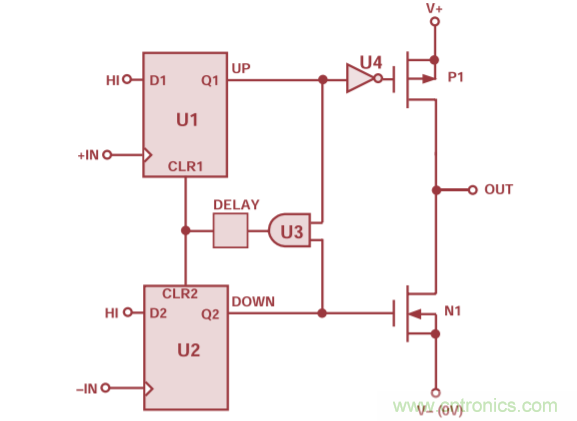

图1所示为PFD的一种实现方案,该类器件基本上由两个D型触发器组成。 一路Q输出使能正电流源,另一路Q输出则使能负电流源。 假设本设计中D型触发器由正边沿触发,则状态为(Q1, Q2):

11—两个输出均为高电平,由反馈至触发器上CLR引脚的AND栅极(U3)禁用。

00—P1和N1均关闭,输出OUT实际处于高阻抗状态。

10—P1开启,N1关闭,输出位于V+。

01—P1关闭,N1开启,输出位于V–。

图1. 运用D型触发器的典型PFD。

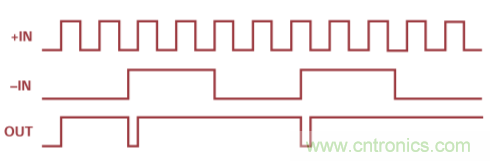

现在考虑系统失锁且+IN处的频率远高于–IN处的频率时电路的性能表现,如图2所示。

图2. PFD波形(锁频和锁相均解除)。

由于+IN处的频率远高于–IN处的频率,因此输出多数时间处于高电平状态。 +IN上的第一个上升沿会发送输出高电平,并且这种情况会一直持续到–IN上出现第一个上升沿。在实际的系统中,这就意味着输出及VCO的输入会被进一步拉高,进而造成–IN处的频率增加。这恰恰是期望达到的效果。

如果+IN处的频率远低于–IN处的,则会出现相反效果。 OUT处的输出多数时间处于低电平状态。 这会在负方向上驱动VCO,并再次使得–IN处的频率更加接近+IN处的频率,从而达到锁定条件。 图3显示了输入处于锁频和接近锁相条件时的波形。

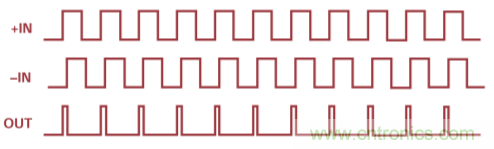

图3. PFD波形(锁频,但相位锁定解除)。

由于+IN领先于–IN,因此输出为一系列正电流脉冲。 这些脉冲往往会驱动VCO,使得–IN信号变得与+IN信号相位对齐。

发生这种情况时,如果U3和U1及U2的CLR输入端之间没有任何延迟元件,那么输出可能会进入高阻抗模式,从而既不会生成正电流脉冲,也不会生成负电流脉冲。 这并不是一种很好的状况。 VCO会发生漂移,直到造成显著的相位误差并再次开始生成正电流脉冲或负电流脉冲。 这种循环会持续相当长的一段时间,其影响是电荷泵的输出会被某个信号(PFD输入参考频率的次谐波)调制。 由于这可能是一种低频信号,因此无法通过环路滤波器进行衰减,从而会导致VCO输出频谱中出现非常明显的杂散,该现象称为“间隙”效应。 通过在U3的输出端和U1及U2的CLR输入端之间添加延迟元件,可以确保不会发生这种情况。 添加延迟元件后,即使+IN和–IN相位完全对齐时,电荷泵输出端仍会生成电流脉冲。 该延迟的持续时间等于在U3输出处插入的延迟,称为反冲防回差脉冲宽度。

参考计数器

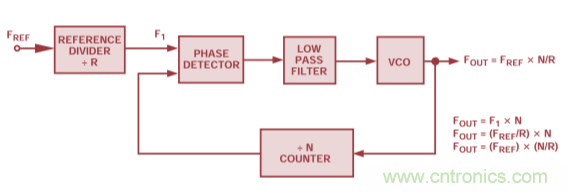

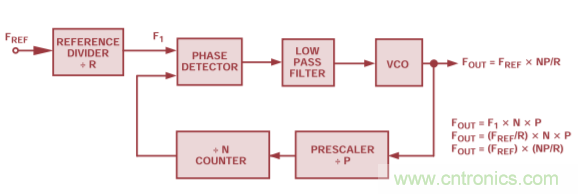

在传统的整数N分频频率合成器中,输出频率的分辨率由施加于鉴相器的参考频率决定。 因此,举例来说,如果需要200 kHz间距(如GSM电话中),那么参考频率必须为200 kHz。 但是,获取稳定的200 kHz频率源并不容易。 一种合理的做法是采用基于晶振的良好高频源并对其进行分频。 例如,从10 MHz频率基准开始并进行50分频,就可以得到所需的频率间隔。这种方法如图4所示。

图4 在PLL频率合成器中使用参考计数器。

反馈计数器N

N计数器也称为N分频器,是用于设置PLL中输入频率和输出频率之间关系的可编程元件。 N计数器的复杂性逐年增长。 除简单的N计数器之外,经过发展,后来还包括“预分频器”,后者可具有“双模”。

这种结构已经发展成为下列情况下固有问题的一种解决方案:需要超高频输出时使用基本N分频结构来反馈至鉴相器。 例如,我们假设需要一个间距为10 Hz的900 MHz输出。 可以使用10 MHz参考频率并将R分频器设为1000。然后,反馈中的N值必须为90,000。这意味着,至少需要一个能够处理900 MHz输入频率的17位计数器。

为处理此范围,需要考虑在可编程计数器之前加上一个固定计数器元件,以便将超高输入频率拉低至标准CMOS的工作频率范围内。 该计数器称为预分频器,如图5所示。

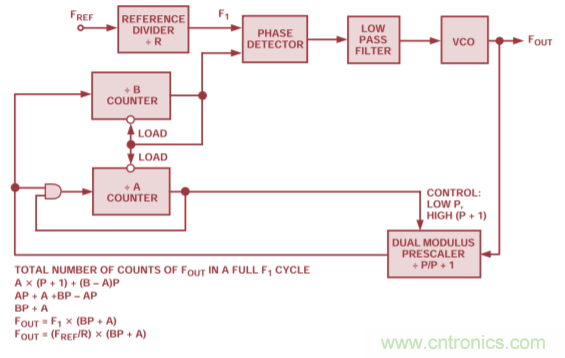

然而,使用标准的预分频器会导致其他并发症。 现在,系统分辨率降低(F1 × P)。 可通过使用双模预分频器来解决这个问题(图6)。 这种方法可以享有标准预分频器种种优势,又不会牺牲系统分辨率。 双模预分频器是一种可通过外部控制信号将分频比从一个值切换为另一个值的计数器, 通过使用带有A和B计数器的双模预分频器,仍可以保持F1的输出分辨率。 不过,必须满足下列条件:

图5. 基本预分频器。

图6. 双模预分频器。

1.如果两个计数器未超时,其输出信号都为高电平。

2.当B计数器超时时,其输出变为低电平,并立即将两个计数器加载至其预设值。

3.加载到B计数器的值必须始终大于加载到A计数器的值。

假设B计数器刚发生超时并且两个计数器均已经重新加载值A和B。我们来看看再次达到相同状态所需的VCO周期数。

只要A计数器未超时,预分频器即会以P + 1进行分频。因此,每次预分频器计数达到(P + 1)个VCO周期时,A和B计数器都会递减1。 这意味着,A计数器会在((P + 1) × A)个VCO周期后超时。 然后,预分频器会切换至P分频。也可以说,此时B计数器还有(B – A)个周期才会超时。 所需时间为: ((B – A) × P)。 现在,系统会返回到刚开始的初始条件。

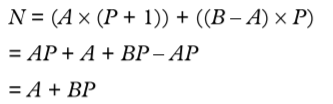

所需的VCO周期总数为:

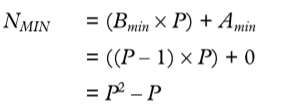

在使用双模预分频器时,必须考虑N的最低值和最高值。这里,我们真正想要的是可以按离散整数步长更改N的范围。考虑表达式N = A + BP。为确保N有连续的整数间距,A必须在0至(P – 1)之间。这样,每当B递增时,就有充足的分辨率来填充BP 和(B + 1)P之间的所有整数值。

就如我们针对双模预分频器提到的那样,B必须大于或等于A,双模预分频器才能正常工作。基于此,我们可以说,若要按离散整数步长递增,最小分频比为:

N 的最高值来自

![]()

本例中,Amax 和Bmax仅仅取决于A和B计数器的大小。接下来,我们将给出一个采用ADF4111的例子。

我们假设,通过编程将预分频器的分频比设为32/33。

A计数器: 6位意味着,A可能为26– 1 = 63

B计数器: 13位意味着,B可能为213 – 1 = 8191

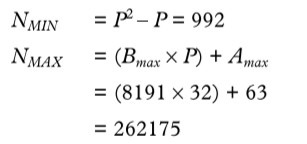

ADF4110系列

前面几节讨论的构建模块在来自ADI公司的新型整数N频率合成器系列中均有使用。ADF4110系列频率合成器由单个器件构成,ADF4210系列由双通道版本构成。ADF4110的框图如下所示。其中含有上面描述的参考计数器、双模预分频器、N计数器和PFD模块。

图7. ADF4110系列的框图。

小数N频率合成器s*

许多新兴无线通信系统都要求本振(LO)具有更快的切换能力和更低相位噪声。整数N频率合成器要求参考频率等于通道间距。该值可能非常低,意味着高N。该高N会产生相应较高的相位噪声。低参考频率会限制PLL锁定时间。小数N合成是在PLL中同时实现低相位噪声和快速锁定时间的一种方式。

这种技术最初出现在20世纪70年代初。早期工作主要由惠普公司和Racal公司完成。该技术最初称为“digiphase”,但后来被广泛称为小数N。

在标准频率合成器中,只能用一个整数除以RF信号。这就需要使用一个相对较低的参考频率(取决于系统通道间距),并在反馈中导致高N值。这两个事实都对系统建立时间和系统相位噪声有着重要影响。低参考频率意味着较长的建立时间,高N值意味着较大的相位噪声。

如果反馈中可能出现除数为小数的情况,则可以使用较高的参考频率,同时实现通道间距目标。小数越小,则意味着相位噪声越低。

事实上,通过交替除以两个整数,可以实现在较长时间内用小数除(通过先后除以2和3可以除以2.5)。

那么,如何除以X或(X + 1)(假设小数在这两个值之间)? 数值的小数部分可以按参考频率速率累加。

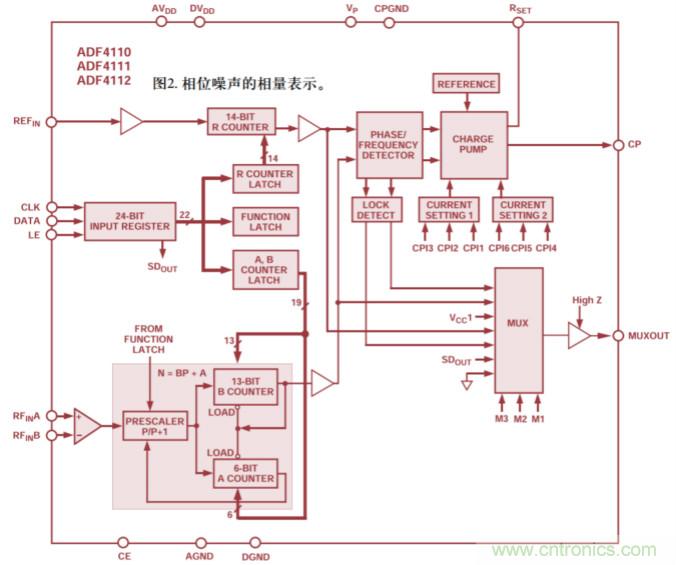

图8. 小数N频率合成器。

然后,每当累加器溢出时,就可以用该信号来更改N分频比。在图8中,这是通过移除馈入N计数器的一个脉冲来实现的。实际上,每当累加器溢出时,结果会使分频比加1。另外,F寄存器中的数值越大,累加器溢出次数越多,以较大数值为除数的次数也就越多。这正是电路的目的所在。但会增加一些并发症。从N分频电路馈入鉴相器的信号在实时表现上并不均匀。相反,其调制速率取决于参考频率和编程小数。结果又调制鉴相器输出,并进入VCO输入端。最后,在VCO输出端会出现较多的杂散内容。目前业界正在努力解决这些杂散问题。 一种方法是采用DAC,如图8所示。

目前为止,单芯片小数N频率合成器仍然未能达到预期,但最终可以实现的效益意味着,其发展正在快马加鞭地进行。

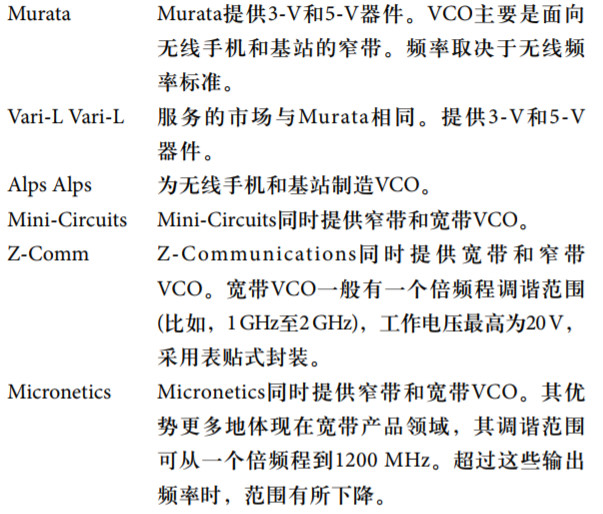

VCO制造商小结

在过去5年中,随着无线通信的爆炸式增长,对频率合成器、VCO等产品的需求也出现了大幅增长。 有意思的是,到目前为止,为市场提供服务的制造商分为泾渭分明的两个阵营。 以下列出了VCO领域的部分制造商。 列表并未穷尽所有制造商,只是让读者获得对一些主要参与者的认识。

VCO

ADI频率合成器系列

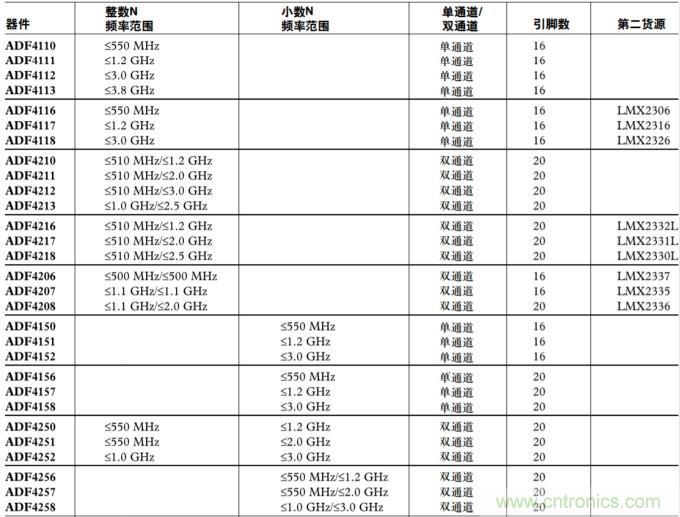

下表列出了ADF4xxx频率合成器系列的未来成员, 其中包括单通道和双通道器件,以及整数N和小数N器件。

致谢

ADF4xxx系列频率合成器在爱尔兰利默里克的ADI工厂中设计。 产品线团队包括: Mike Tuthill、Leo McHugh、Bill Hunt、Mike Keaveney、Brendan Daly、Paul O’Brien、Paul Mallon、Ian Collins、Sinead O’Keefe、Liam McCann、Patrick Walsh、Cristoir O’Reilly、Paul Laven、Samuel Landete、Niall Kearney和Mike Curtin。 团队希望借此机会向ADI公司英国肯特分公司的Jon Strange和Ashish Shah,以及ADI公司西北实验室(美国俄勒冈州比佛顿)的Fred Weiss致以诚挚的谢意,感谢他们提出的宝贵意见。

参考文献

1. Mini-Circuits Corporation, VCO Designer’s Handbook, 1996.

Mini-Circuits公司,VCO Designer’s Handbook(VCO设计师手册),1996年。

2. L.W. Couch, Digital and Analog Communications Systems, Macmillan Publishing Company, New York, 1990.

L.W. Couch,Digital and Analog Communications Systems(数字与模拟通信系统),Macmillan Publishing Company,New York,1990年。

3. P. Vizmuller, RF Design Guide, Artech House, 1995.

P. Vizmuller,RF Design Guide(RF设计指南),Artech House,1995年。

4. R.L. Best, Phase Locked Loops: Design, Simulation and Applications, 3rd Edition, McGraw-Hill, 1997.

R.L. Best,Phase Locked Loops: Design, Simulation and Applications(锁相环:设计、仿真与应用),第3版,McGraw-Hill,1997年。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

新一代AC/DC ZVS高功率密度USB PD解决方案,助力移动设备快速充电

用于高频接收器和发射器的锁相环——第一部分

典型工作环境中分析光伏 I-V 特性,咱得讲究个“精确”

纳微半导体将与Live Oak II合并,以10.4亿美元的企业价值上市

安科诺科技与友尚企业签订代理商合约