如何简化FPGA电源系统管理?

现场可编程门阵列(FPGA)的起源可以追溯到20世纪80年代,从可编程逻辑器件(PLD)演变而来。自此之后,FPGA资源、速度和效率都得到快速改善,使FPGA成为广泛的计算和处理应用的首选解决方案,特别是当产量不足以证明专用集成电路(ASIC)的开发成本合理有效时。

现场可编程门阵列(FPGA)的起源可以追溯到20世纪80年代,从可编程逻辑器件(PLD)演变而来。自此之后,FPGA资源、速度和效率都得到快速改善,使FPGA成为广泛的计算和处理应用的首选解决方案,特别是当产量不足以证明专用集成电路(ASIC)的开发成本合理有效时。

FPGA取得快速发展,并广泛用于大规模部署。例如,继2013年试点项目中使用FPGA成功加快Bing搜索引擎的速度之后, Microsoft® 将配备FPGA的服务器使用范围扩展到云数据中心。

FPGA电源系统要求

FPGA需要几个不同的低压供电轨,每个供电轨都有自己的电压和电流规格,以便为其内核逻辑、I/O电路、辅助逻辑、收发器和存储器供电。这些供电轨可能需要按特定的顺序开启和关闭,以避免损坏FPGA。负载点(POL)稳压器将电路板较高的输入电源电压降低为FPGA所需的多个输入电压。当功率转换效率至关重要时,开关稳压器可用作POL稳压器,而线性稳压器(例如低压差(LDO) 稳压器)则用于噪声敏感型电路,例如PLL和收发器。

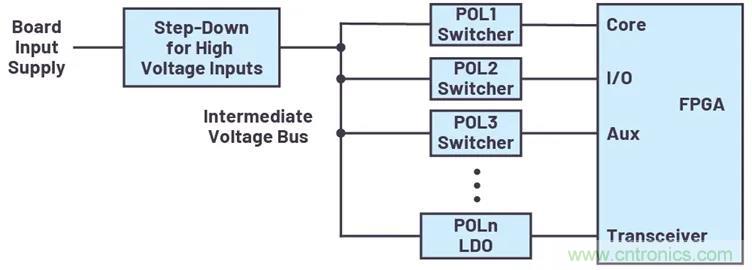

典型的电路板输入电压为5 V、12 V、24 V和48 V,FPGA的输入电压范围则为低于1 V至约3 V。对于高输入电压(12 V、24 V、48 V),可能需要使用额外的降压稳压器来生成馈送给POL稳压器的中间总线电压(参见图1)。在FPGA供电轨中,核电压需要最低的电压(约等于或低于1 V)和最高的精度(±3%或更优),电流电平约为几十安培,具体取决于FPGA资源的利用率。为了防止出现逻辑错误,不仅在直流条件下,而且在FPGA电流瞬态期间,电压波动都需要按照FPGA供电轨公差规格要求控制在几十毫伏之内。电源的直流精度越差,在瞬态条件下维持可用电源电压所需的旁路电容就越多。例如,假设采用±3%内核电压公差规格。使用精度为±1%的直流电源时,对应的瞬态公差为±2%。直流电源的精度较低(±2%)时,瞬态公差会更严格(±1%),相比之前的示例,需要更多的旁路电容。

图1. 一种可行的FPGA电源树设计:高压输入电源(例如12 V、24 V或48 V)降至中间总线电压,然后馈送给为FPGA供电的POL稳压器。

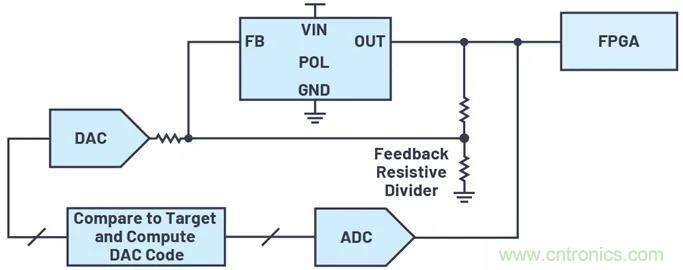

在最终进行设计变更、在另一种应用中重用设计、实施板裕量测试,以及在开发或现场运行期间动态优化系统功耗时,都需要基于默认的设定点调整或微调FPGA电源电压电平。在这种情况下,在电源反馈网络中采用多个不同电阻并联不是最快或最可行的解决方案。实现电压微调的一种方法是使用数模转换器(DAC)来驱动稳压器的反馈网络(参见图2)。需要为微调程序编写软件代码,从模数转换器(ADC)获取电源电压测量数据,以计算正确的DAC代码,然后缓慢将DAC输出调节至计算出的数字码,逐步稳定提高电源电压,在不会产生毛刺或过冲的情况下达到目标电压电平。这种微调程序需要重复实施,以确保不会因为组件随时间或温度变化出现偏移,进而导致电源偏离目标电压。

图2. 使用DAC和ADC将POL电源输出电压微调至目标电压。

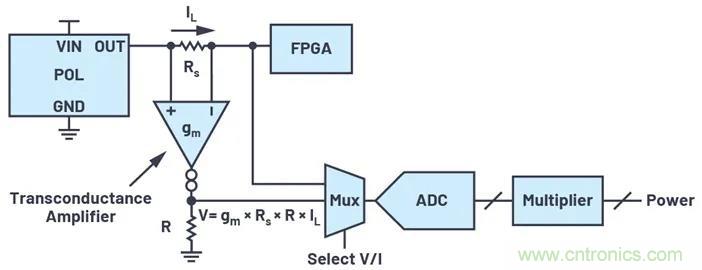

监测FPGA电源电压、电流和故障条件,对于理解系统在不同场景下的健康状况和功耗至关重要,这是因为,FPGA是整个电子系统的核心。将这种理解和微调功能结合起来,可以避免为最坏的情况设计电源,从而节省成本和功率。此外,潜在的系统故障可能表现为FPGA功耗异常,从而在电路板或系统发生故障之前让主机控制器或维修人员及早发现问题。电压监测需要使用ADC,而电流监测还需要使用电平偏移电路将高电平电流检测电压转换为接地基准电压;例如,如图3所示,通过使用跨导放大器。

图3. 用于监测POL电源输出电压、电流和功率的一种分立式电路可行方案。

虽然我们还未探讨故障管理,但看了这一长串要求之后,您可能已头晕脑胀。当POL输出出现欠压或过压时,即在有效的电压窗口范围外时,会出现什么情况?应该只关闭故障电源?还是应该也关闭其他电源?如何消除导致系统板关断的故障?

我们可以看到,FPGA的电源系统管理很快会变得非常复杂,从而分散对基本的FPGA应用的关注。注意,FPGA的电源树只是数字处理电路板上整个电源系统的一部分。上述大部分要求也适用于其他数字器件,例如ASIC、DSP、GPU、SoC和微处理器。我们所需的是一个简单、可扩展且灵活的电源系统管理解决方案。

数字电源系统管理

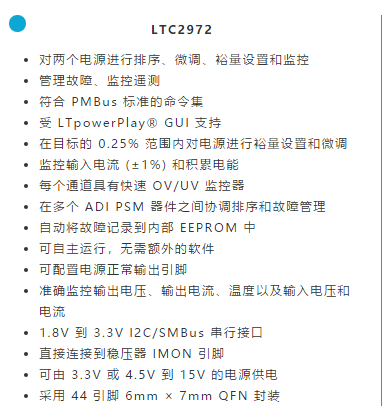

ADI公司提供数字电源系统管理(DPSM)器件产品,以满足数字处理电路板中复杂的电源系统要求。DPSM器件可提供或不提供集成DC/DC转换,以替代POL稳压器,或者与现有的POL稳压器配合使用。电源系统管理器不提供DC/DC转换,对于由开关或LDO稳压器构成的现有模拟电源系统,可增加数字监测和控制功能。使用单个器件(例如 LTC2980),可对16个POL稳压器实施微调、裕量调节、监测、时序控制、电源监控、故障记录和故障管理。可以混合和匹配使用不同通道数器件(2、4、8或16个通道),以管理数百个供电轨。双通道 LTC2972是该系列的最新产品,它提供了一种简单的入门解决方案,可监测和控制此类电源系统中两个最重要的供电轨;例如,FPGA内核供电轨和辅助供电轨。

双通道电源系统管理器

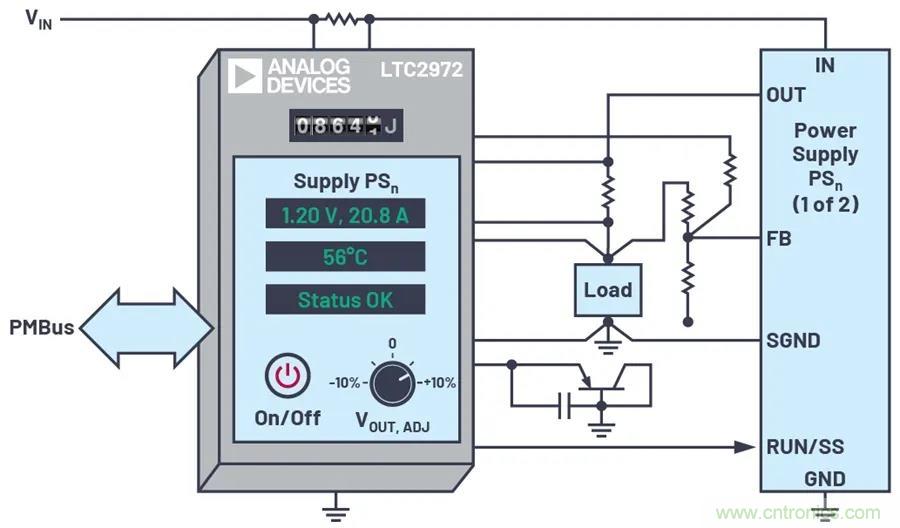

LTC2972是一款双通道电源系统管理器,为FPGA、ASIC和处理器电路板增加了基于软件的全面监测、控制和黑盒故障记录功能,可加快产品上市,提升系统可靠性,以及优化电路板功耗(图4)。使用出色的16位ADC对POL电源输出电压实施微调、裕量调节和监测,总非调整误差(TUE)为0.25%,以提升电路板的功率和长期性能。因为能够严格控制POL输出电压,实现±0.25%的精度,所以在负载瞬态(在±3% FPGA供电轨规格下,精度为±2.75%)期间有很大的裕量,从而大幅减少所需的旁路电容并释放电路板空间。电源输出电流使用检测电阻、电感DCR,或者电源的IMON输出进行测量。电压和电流测量值在内部进行乘法运算,提供POL输出功率读数。

图4. LTC2972是一款双通道电源系统管理器,提供中间总线电源监测和 POL输出功率监测。

LTC2972内置电源时序控制、监控和EEPROM故障记录功能。通过将时间延迟写入内部寄存器或使用级联电源良好信号来完成时序控制。当POL输入电压、输出电压和温度以数字方式偏离可设置阈值上下限时,专用快速比较器发出故障信号。故障触发EEPROM黑盒记录,简化故障分析,并提供有关未来系统改进的相关见解。第一个故障命令提供关于系统故障原因的更多信息。故障信 息可灵活传播到其他电源或其他DPSM器件。

LTC2972支持对POL转换器的中间总线输入实施电压、电流、功率和电能监控。为了管理、优化和降低电路板功耗,进而降低服务器和数据中心的散热和公用设施成本,必须监测电路板功率和电能使用状况。LTC2972通过PMBus接口(与电源管理和转换器件通信的行业标准)方便地提供输出电能(单位:焦耳)和运行时间,以减少繁重的轮询和计算任务。将LTC2972与POL输出电压、电流和功率这些数字测量值结合使用,就可以长期监测电源系统的转换效率。

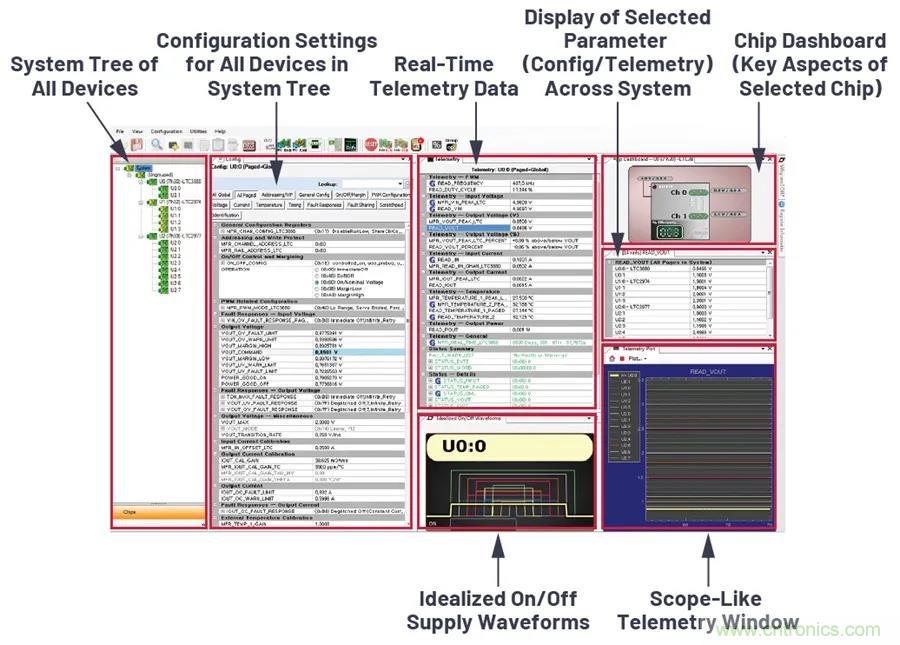

每个通道都配有可编程电源良好引脚或通用输入/输出(GPIO)引脚。LTC2972与其他电源系统管理器连接,可实现两个以上供电轨的时序和故障管理。使用通过 I2C/SMBus 接口传输的兼容PMBus命令,可对电源系统实施灵活编程和数据回读。配置在支持ADI所有DPSM产品的 LTpowerPlay®开发环境下完成(参见图5)。采用所需的应用特定配置进行内部EEPROM编程后,就无需为实现自动运行而编写软件代码。

图5. 适用于DPSM产品的LTpowerPlay开发环境:无需为实现自动运行而编写代码。

FPGA广泛应用于各种电子系统,甚至取代ASIC,但其周围具有复杂的电源系统。ADI公司提供多种DPSM产品来帮助简化电源系统管理。如果您以前从未用过DPSM,您可以试试LTC2972,这是一款入门级产品,能够解决数字处理电路板上复杂的电源系统问题。

(来源:亚德诺半导体)