如何设计满足超宽超高压输入电源的磁隔离驱动电路

在开关电源设计中,主功率有多个开关管时其驱动必须采用隔离设计,比如多管串联反激、双管正激、LLC等多开关管的拓扑中,开关管驱动均需要做隔离处理。当前市面上已经有较成熟的自举驱动芯片来满足设计需求,但是其驱动芯片的耐压等级受限,最高电压只能到600V左右。

背景介绍

在开关电源设计中,主功率有多个开关管时其驱动必须采用隔离设计,比如多管串联反激、双管正激、LLC等多开关管的拓扑中,开关管驱动均需要做隔离处理。当前市面上已经有较成熟的自举驱动芯片来满足设计需求,但是其驱动芯片的耐压等级受限,最高电压只能到600V左右。在更高输入电压等级的应用场合中,比如光伏电源、SVG辅助电源等输入电压达到1500V甚至更高的电源产品设计时,驱动芯片的方案就不再适用,只能选择磁隔离变压器驱动电路。因此磁隔离驱动电路的设计极其重要。

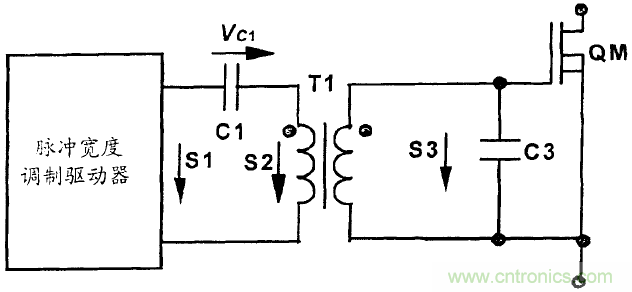

图1 常用的磁隔离驱动电路

常用的磁隔离驱动方案

常用的磁隔离驱动电路如图1所示。

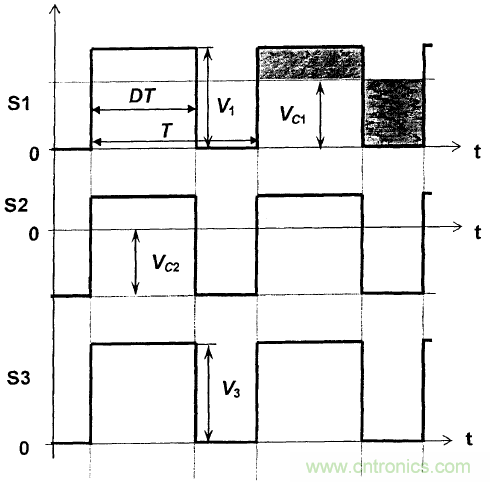

其中,电容C1为输入端直流隔离电容,C3为开关管QM等效的输入电容。电容电压的参考方向如图1所示,T1为磁隔离驱动变压器。S1是脉冲宽度调制驱动器(PWM Driver)的输出信号波形,S2是变压器输入端的波形,S2是该磁隔离驱动器的输出波形。图1所示的电路工作波形如图2所示。

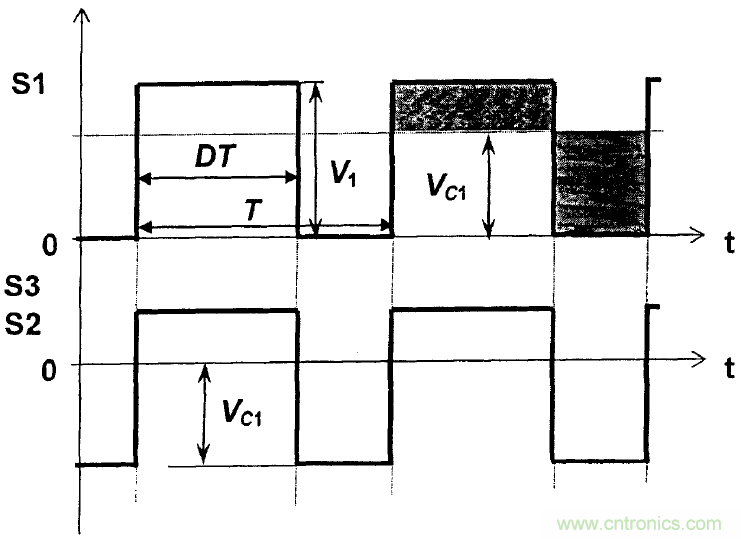

图2 磁隔离驱动波形示意图

假设稳态时该驱动器的输出信号S1的周期为T,占空比为,幅值为,同时假设变压器T1的输入输出匝比为1,则稳态时输入端直流隔离电容C1上的电压为D·VS1。在S1为高电平时,S3也为高电平,其幅值为(VS1-VC1),即(1-D)·VS1。而在S1为低电平时,S3为负电平,其幅值为(-VC1),即D·VS1。

具体的推导过程如下:

由此可见,这种隔离驱动电路线路简单,而且被驱动的MOS管有负向的驱动电压,抗干扰能力强。但其有待改进之处在于,在占空比D较大时,S3的高电平幅值就较小,可能导致QM驱动电压不足。这样,这种驱动器电路不适合应用在占空比变化较大的场合,即输入比范围大的(1-D)·VS1应用条件下,图1所示的驱动电路将不再适用。

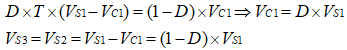

图3 双隔直磁隔离驱动电路

双隔直磁隔离驱动电路

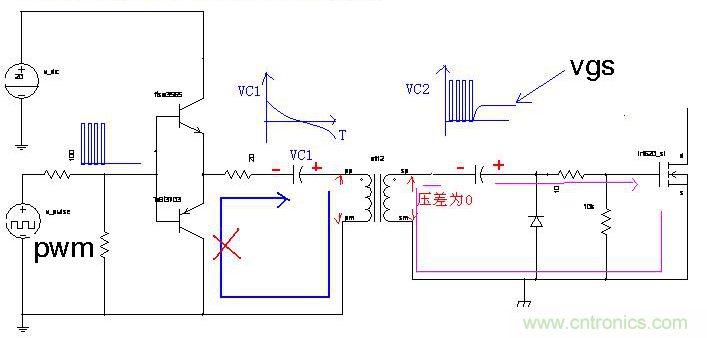

为了解决上述难点问题,需要在图1所示的磁隔离驱动电路次级边也添加隔直电容,如图3所示。

相对图1的磁隔离驱动电路而言,添加了次级的直流隔直电容C2和开关二极管DR。稳态时输入端隔直电容C1上的电压VC1=D·VS1,输出端隔直电容C2上的VC2=D·VS1。其电压参考方向如图3所示。图3电路的工作波形如图4所示。可知,稳态后QM的电压V3不随占空比变化而改变,适合更宽范围输入条件的驱动设计。

图4 双隔直磁隔离驱动电路波形示意图

但是图3所示的电路在某些特殊状态下,比如输入端突然断电或者负载突变过程中脉冲宽度调制驱动器的输出信号会突然消失,即驱动信号S1将为0。随后变压器T1在输入端隔直电容电压(-DVs1)作用下逐渐进入饱和,同时C2上的电压仍为DVs1,T1上的输入输出电压幅值从DV1逐渐减小,此时QM上的电压将从0开始逐渐增加,直到与C2上的电压相等。其波形示意图如图5中红色框所示。

由此可见,在特殊条件下QM会出现失控的驱动信号,该信号造成开关管误导通,引发主功率变压器饱和,导致产品炸机。

图5 双隔直磁隔离驱动电路误导通波形示意图

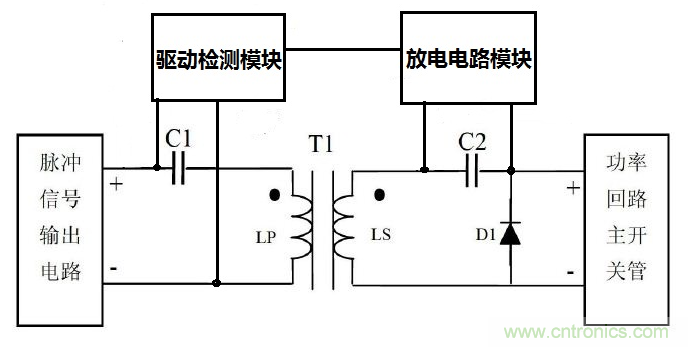

我司优化后的磁隔离驱动方案

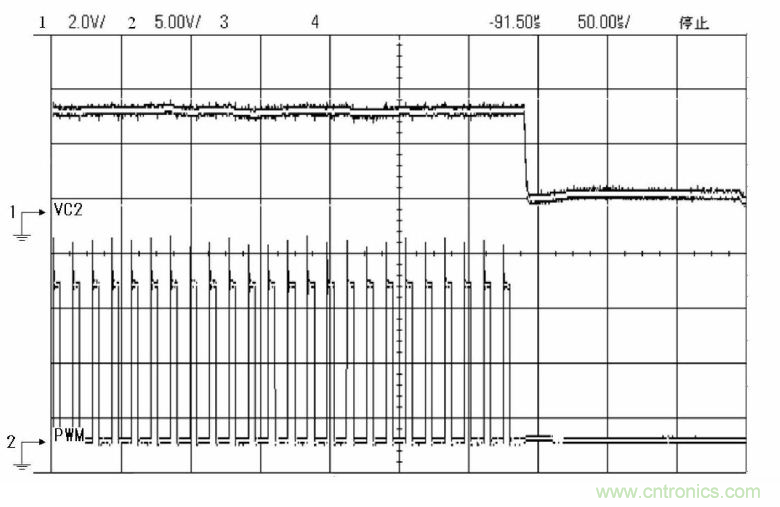

为了解决图3中双隔直磁隔离驱动电路的误导通问题,我司针对次级隔直电容C2做了特殊放电电路。如图6所示,其中添加了原边检测电路和次级隔直电容放电电路,该电路为我司自主发明专利电路。通过高速光耦做信号隔离,有效解决主功率开关管误导通的问题,改进后的驱动波形如图7中2通道PWM波形所示,可以看出在驱动异常关闭状态下,C2上的电压迅速放电完成,开关管不会出现异常开通状态。为我司超高超宽压输入系列产品提供高可靠的驱动,提升产品综合竞争力。

6 改进后的双隔直磁隔离驱动电路

总结

采用变压器做的磁隔离驱动电路,如果只有原边有隔直电容时,在占空比较大的条件下次级输出电压会降低,无法满足开关管驱动的要求。当次级添加隔直电容后可以解决大占空比的问题,但是在异常条件下次级隔直电容放电会导致开关管异常导通,进而出现原边饱和导致产品炸机。我司针对上述问题重点突破,添加次级隔直电容放电电路,使得磁隔离驱动电路不受占空比影响的同时完美解决异常条件下开关管异常导通的现象。该放电电路设计简单、可靠,大幅提升产品可靠性。

图7 改进后的双隔直磁隔离驱动电路波形图