高带宽探头挖潜增效和前端选择及焊接指南

品慧电子讯示波器探头作为测量系统中的组成部分其重要性不言自明,即使在今天一致性测试成为实时示波器的主要应用领域而多采用夹具和电缆组合来拾取信号进行断路测试的情况下,因为类似DDR和MIPI之类总线在测试的时候,依然必须依靠探头接入被测电路进行测试。

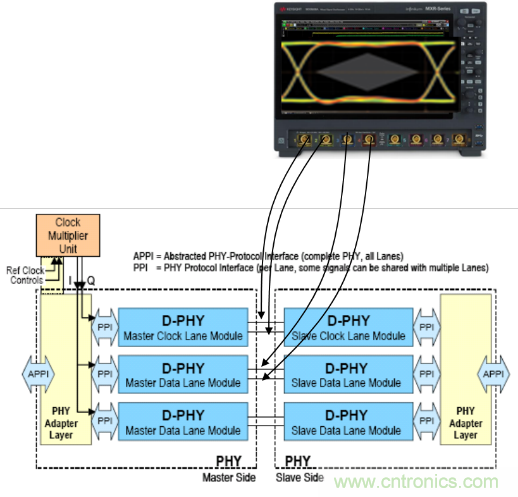

图1 DDR和MIPI-DPHY测试连接典型图

关于这两种典型总线在测试时对探头的要求相关文章和论述有很多,包括对探头的带宽,阻抗容抗,衰减比及探头的电路结构差异等等,可参考《DDR5验证和测试》,无需赘述。

随着LPDDR4标准推进到4.2Gbps和DDR5 从4.8Gbps起步,您是否发现前几年按照3.2Gbps速率购买的典型的13GHz带宽的示波器和探头系统比如DSAV134A和1169A/B已经有点力不从心呢?

这时您会发现,早先购买了一台软件升级带宽的示波器是多么明智,无需返厂只要购买一个带宽升级许可证书即可在自己的实验室完成升级!然而,根据平坦响应系统带宽公式:

![]()

因此即便示波器升级到更高带宽,但是如果探头带宽依然是13GHz,整个系统带宽还是13GHz。

如何解放1169B的生产力发挥更大作用?

锦囊一 :挖潜增效,让资产升值!

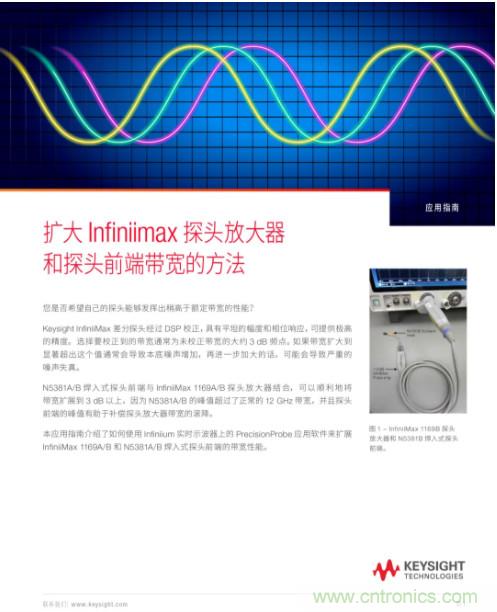

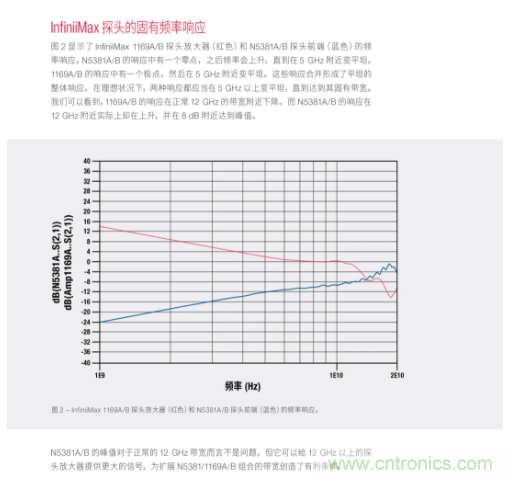

Keysight Infiniimax 差分探头经过DSP校正,具有平坦的幅度和相位响应,可提供极高的精度。选择要校正到的带宽通常为未校正带宽的大约3 dB 频点。

如果带宽扩大到显著超出这个值通常会导致本底噪声增加,再进一步加大的话,可能会导致严重的噪声失真。

N5381A/B 焊入式探头前端与Infiniimax 1169A/B 探头放大器结合,可以顺利地将带宽扩展到3 dB 以上,因为N5381A/B 的峰值超过了正常的12 GHz 带宽,并且探头前端的峰值有助于补偿探头放大器带宽的滚降。

扩大Infiniimax 探头放大器和探头前端带宽的方法

锦囊二 :细节决定成败,如何善用探头?

除了充分挖掘现有探头带宽的潜力外,从操作层面来看,还有哪些注意事项可以有效提高信号连接环节的带宽和信号保真度?很多时候我们对选择示波器非常看重,但是对后续的使用和测试细节却常常敷衍了事,而对这些小的细节的疏忽往往导致我们事倍功半!

细节决定成败!

从设计角度,预先做好可测性设计(Design For Test),包括预留尽可能接近被测信号末端的测试点和地测试点

以MIPI总线测试为例,由于存在共模偏置电压,因此要采用差分探头对差分的数据和时钟信号正和负端分别进行单端测试,然后进行差分和共模运算分别得到有效的差分信号和共模偏置。

这一电路特点决定的信号探测方法,导致信号探测过程中对有效的参考接地要求非常严格。

因此,比如对D-PHY推荐在设计时即考虑在DSI总线末端(显示屏侧)或者CSI总线末端(AP侧),除对差分信号的正和负端分别留测试点外,还要预留尽可能近的同一地平面的地测试点。

对其它一般Serdes信号,也应尽可能在被测线路末端或接收端预留测试点,以降低测试点位于线路中间情况可能引起的反射,另外在高速情况下,线路中间测试点的过孔或焊盘的Stub效应和探头负载对线路的影响极大。

选择恰当的焊接探头前端

● 配合Infiniimax系列探头放大器,有很多探头前端,这些前端之间有何差异?

● 比如测试DDR总线,很多工程师非常偏爱ZIF探头前端N5425A/B,对应有很多ZIF Tip可以选择,比如N5426A,N5451A等,有何差异呢?

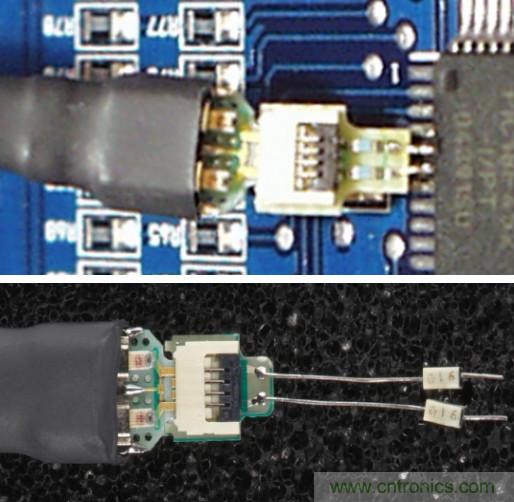

图2 N5426A(上)和N5451A(下)

表1 N5426A和N5451A不同焊线长度和角度带宽

可见,更长的焊线,带宽更低,负载效应也更大,其频响特性平坦度也会下降。长焊线的两腿之间的角度越大也会带来带宽下降。

除了ZIF探头,还有常用的直接焊接探头E2677A/B,N2836A和N5381A/B及N5441A,差别在于前两者阻尼电阻在探头前端PCB外,后两者阻尼电阻在焊接PCB上。

图3 E2677A/B(左)和N5381A/B(右)

差异和优缺点在哪里呢?

表2 直接焊接前端差异

针对焊接探头前端的阻尼电阻选择,请参照产品手册或者使用手册。比如E2677A/B有91?和150?两种,其中91提供了全带宽而150则提供中等带宽能力。

对阻尼电阻在前端PCB外,如果需要伸入到器件进行测试,应选择阻尼电阻到测试点之间的焊线尽量短,以确保最小化Stub效应。对于阻尼电阻在前端PCB上的,当然焊线也应尽量短。

在可测性设计和前端选择都得到保证的情况下,还有什么因素会对信号探测环节的信号保真度产生影响呢?

完美地焊接探头也是确保测试过程中的信号保真度的重要一步,而且对探头的重复使用至关重要,更是对资产的妥善保护!

首先,选择针对不同的探头前端选择恰当的烙铁头:

图4 针对不同探头前端选择大小合适的烙铁头

Keysight InfiniiMax探头焊接指南

结语

本期文章就探头相关方面从扩大带宽到前端选择及焊接等几个角度提供一些参考和建议。

推荐阅读:

陶瓷电容器静电容量随时间变化的原理

Astera Labs全面提供适用于PCIe 4.0和5.0互连的Aries Smart Retimer

贸泽与Amphenol i2s 签订全球分销协议,进一步扩充传感器产品阵容

功率密度基础技术简介

堆叠PowerStack封装电流获得更高功率POL