我摊牌了,我知道PLL/VCO技术应该怎么提升性能~

品慧电子讯多年来,微波频率生成使工程师面临严峻的挑战,不仅需要对模拟、数字、射频(RF)和微波电子有深入的了解,尤其是锁相环(PLL)和压控振荡器(VCO)集成电路组件方面,还需要具备可调滤波、宽带放大以及增益均衡等专业知识。

本文重点介绍近些年微波电路设计取得的进步,这意味着现在采用硅芯片技术中的低相位噪声VCO可以覆盖一个倍频程范围。在这样的IC上集成输出分频器可以支持几个低频倍频程范围,输出集成倍频器则支持单个IC生成高达32 GHz的频率。随着小数N分频PLL频率合成器技术的进步,现在微波频率范围rms抖动可低至60fs,具备无限小的频率分辨率和极小的杂散信号。低插入损耗宽带滤波器可以和这些集成PLL/VCO IC配合使用,以提高整个系统的频谱性能,大大降低了微波和毫米波本地振荡器带来的相关挑战。

简介

本地振荡器(LO)是现代通信、汽车、工业和仪器仪表应用中的关键组件。无论从基带到RF实施上变频还是反过来的下变频,为汽车雷达、材料检测应用生成扫频,或者为上述应用电路的构建和测试而开发仪器仪表,我们生活的很多方面都存在LO。电路和工艺技术的进步已帮助降低了此类电路的成本、复杂性和面积;与过去需要更广泛地混合使用有源和无源技术相比,现代集成电路大大降低了LO的设计难度。

过去,适用于GSM等2G通信应用的大部分LO都使用与ADI公司的ADF4106类似的整数N分频PLL,以及窄带T封装VCO(例如VCO190-1846T)。在大多数情况下,这些VCO的高品质因素(Q)使其非常易于满足该严苛标准下的相位噪声规格。那时的手机一般只支持一种无线标准,标准本身的数据速率也有限(虽然2G网络出色的覆盖率帮助手机获得了广泛的市场认可)。基站LO一般是使用多种IC和VCO子模块组合而成的模块,如图1所示。

图1. 适用于无线通信的LO模块。

对无线数据速率以及与不同的全球无线标准兼容性的需求不断提高,促进了宽带VCO的发展,与窄带VCO相比,宽带VCO有助于实现更宽的频率覆盖范围,支持更多的新可用频谱。支持这种数据吞吐量的微波回程网络也承受着压力,需要支持高阶调制率,可针对不同范围和标准进行配置,同时帮助网络提供商降低工程难度,提高投资回报率。为了支持这些网络开发,典型的信号分析仪使用了庞大笨重的钇铁石榴石(YIG)振荡器,以及使用类似技术的笨重滤波器。

VOC改进

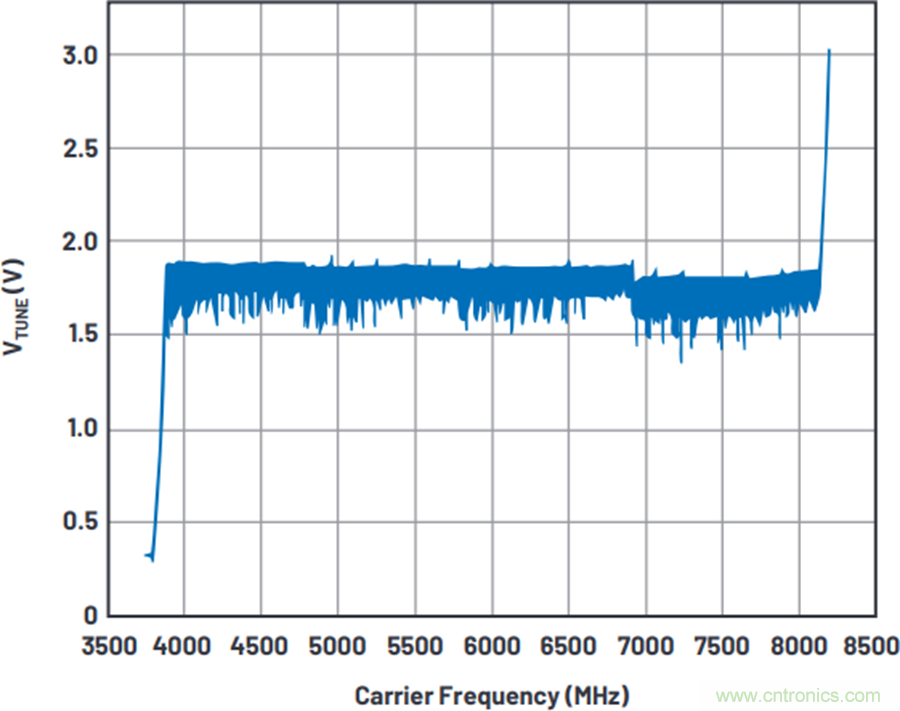

开发集成硅芯片微波VCO面临的最大技术挑战是可用晶圆制造工艺中的Q值有限。在许多情况下,绕线电感(用于T封装VCO中)的Q值可能从数百的典型值降至刚刚超过10,因Leeson方程的限制,Q值会严重影响相位噪声,根据此方程,相位噪声LPM(公式1)与VCO Q值成平方反比,和输出频率成平方正比关系。

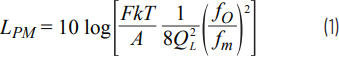

基于砷化镓(GaAs)或锗硅(SiGe)制造的宽带单核VCO通过将VCO的调谐端口范围从5V(大部分硅基PLL电荷泵可用的典型电压)扩展至15V、甚至30V来解决范围与噪声的问题。这意味着,谐振器Q可以保持不变,但扩展的变容二极管可调谐性可以提供更广泛的调谐范围,但不会恶化相位噪声。这种更高调谐范围带来的挑战,可以通过使用有源低通滤波器以将电荷泵电压(典型值为5V)转换为15 V或30 V来解决(参见图2中HMC733的调谐范围)。这些有源滤波器需要使用高压低噪声运算放大器。所以,典型的微波LO将由PLL(如ADF4106),运算放大器以及GaAsVCO组成,在很多情况下,还需要一个外部分频器,将VCO信号分频至PLL允许的最大输入频率(对于ADF4106,为6 GHz)。GaAs VCO一般在S频段和更高频段下运行,因为谐振器电路一般在2GHz以上提供最佳性能。设计电路板时更要格外小心,这需要熟知电源、模拟以及RF和微波领域专业知识。PLL滤波器的设计及其性能仿真都需要具备丰富的控制理论和噪声建模经验,并且需要熟悉每个组件。完成这些任务所需的经验并不容易获得,一般只有从事硬件设计工作几十年的资深人士才具备。

图2. HMC733调谐范围。

目前有多种技术可以解决低Q值问题。在类似ADF4360的产品系列中,裸片(粘接到焊盘上)表面焊线的Q值大约为30。厚金属电感也可以改善Q值,改进变容二极管Q也有助于大幅提高谐振器Q值,从而进一步改善相位噪声性能。适合制造高频率VCO和N分频器电路的BiCMOS工艺,以及用于开关各种电容的CMOS逻辑电路,这些意味着宽带PLL和VCO IC切实可行,其小巧的尺寸和更宽的频率范围则使其迅速得到无线市场的认可。

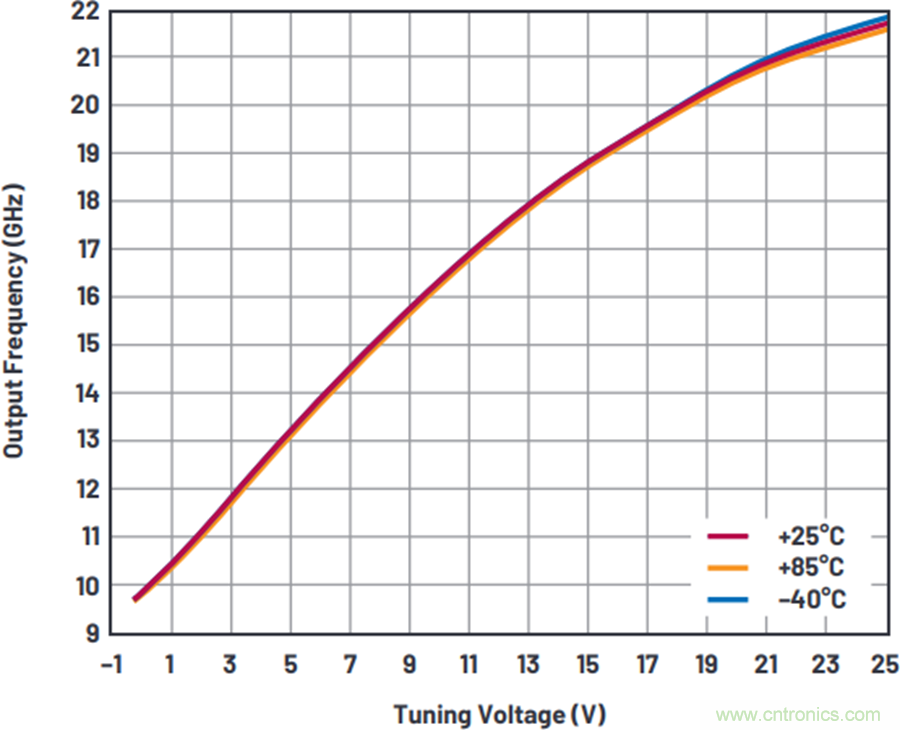

许多宽带LO都采用了这种方法。覆盖整个倍频范围的VCO很有优势,这是因为一组分频器可生成的频率范围只受最低可用VCO频率和最高可用分频比限制。采用硅芯片工艺的VCO设计取得了重 大突破,通过开关不同的电容组,可以将VCO范围划分为多个子频段。这支持实现更广泛的频率覆盖范围,无需通过降低振荡器谐振器Q值来牺牲相位噪声,同时支持使用电压较低的电荷泵,所以无需使用额外的运算放大器,其需要更高的电源电压轨。进一步改善可将VCO频段的数量从数十个增加到数百个,甚至在单片IC上开发其他单独的重叠VCO内核(按需进行开关),从而进一步优化相位噪声,例如ADF4371(图3)。从图2中HMC733的单核VCO与图3的ADF4371的多频段VCO之间,可以看出明显的不同。

图3. ADF4371频率与VTUNE的关系。

从图2的频率与VTUNE关系图中可以看出,HMC733调谐电压与输出频率成正比,而在图3中,调谐电压基本上在VTUNE的1.65V目标值的几百毫瓦以内。智能频段选择逻辑或自动校准电路意味着用户无需针对频率开发频段查找表,且存在足够裕量,可以保证在电源电压范围,尤其是温度电压范围内可靠运行。

PLL改进

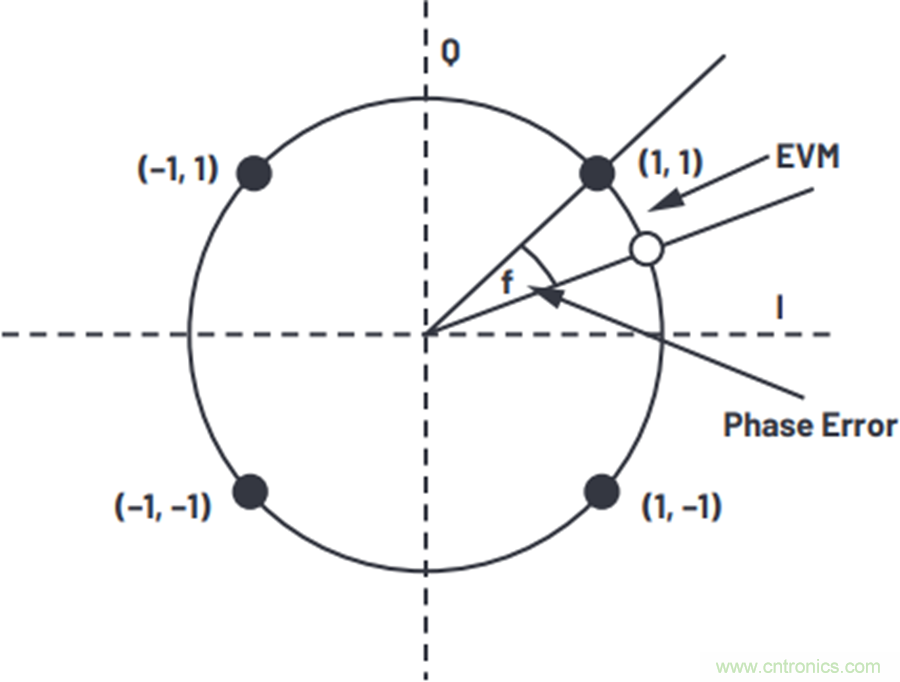

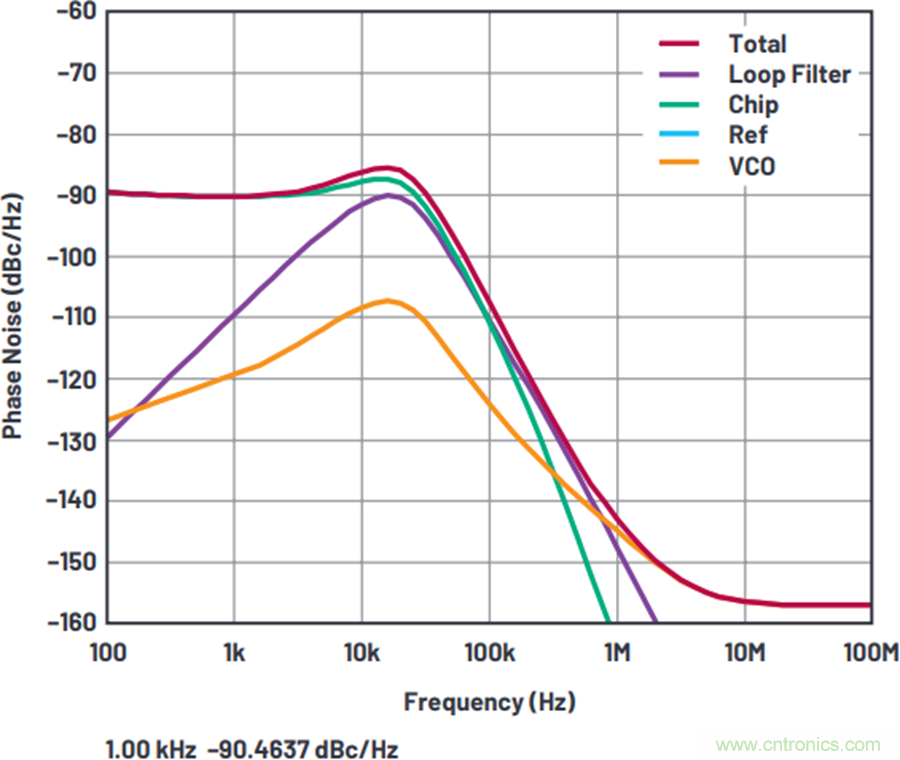

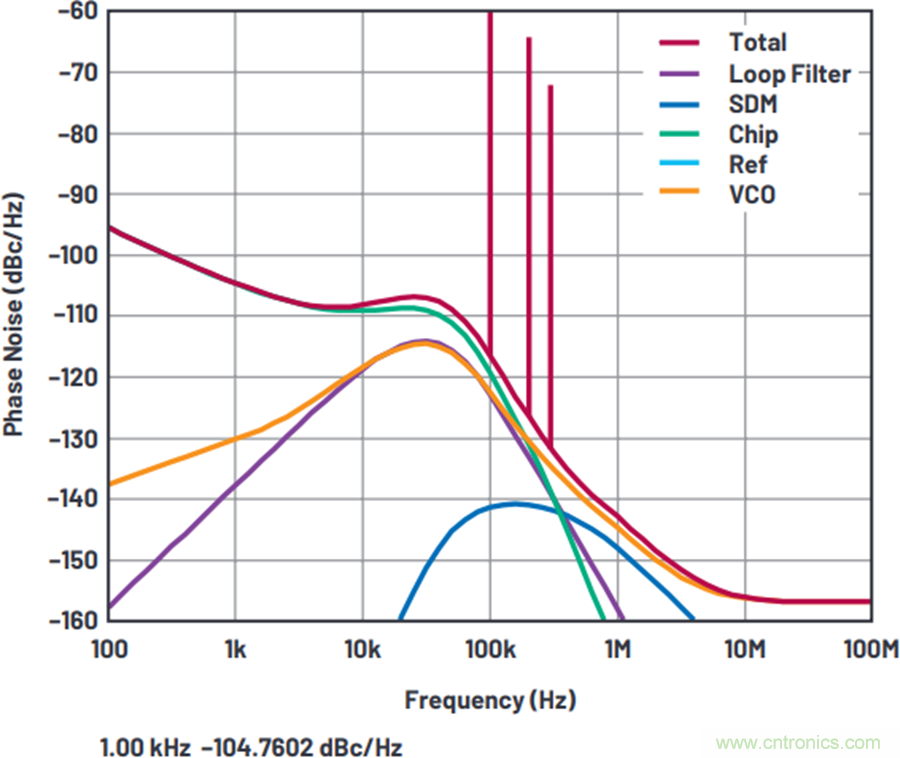

实现更高的数据速率需要具有更低的向量误差调制(EVM)速率(图4),这主要取决于窄带无线应用中PLL频率合成器的带内相位噪声贡献;使用200kHz信道栅提供1.8GHz输出需要很高的N(9000),因而N分频器的20log(N)贡献会在频段内产生严重影响。高阶调制速率(例如64QAM)需要更低的EVM,这会推动开发、采用和部署小数N分频频率合成器,比如ADF4153A和ADF4193,这会使信道栅与PFD频率无关,从而大幅降低带内噪声。将ADF4106和ADF4153A进行比较(比较图5和图6),可以明显看出这一优势,在1kHz频偏下,带内噪声从–90dBc/Hz降至–105dBc/Hz。我们使用ADIsimPLL™来计算,它可以对ADI公司的所有PLL产品进行了仿真。

图4. 相位误差QPSK。

图5. 带VCO-1901846T的整数N分频ADF4106。

图6. 带VCO-1901846T的小数N分频ADF4153A。

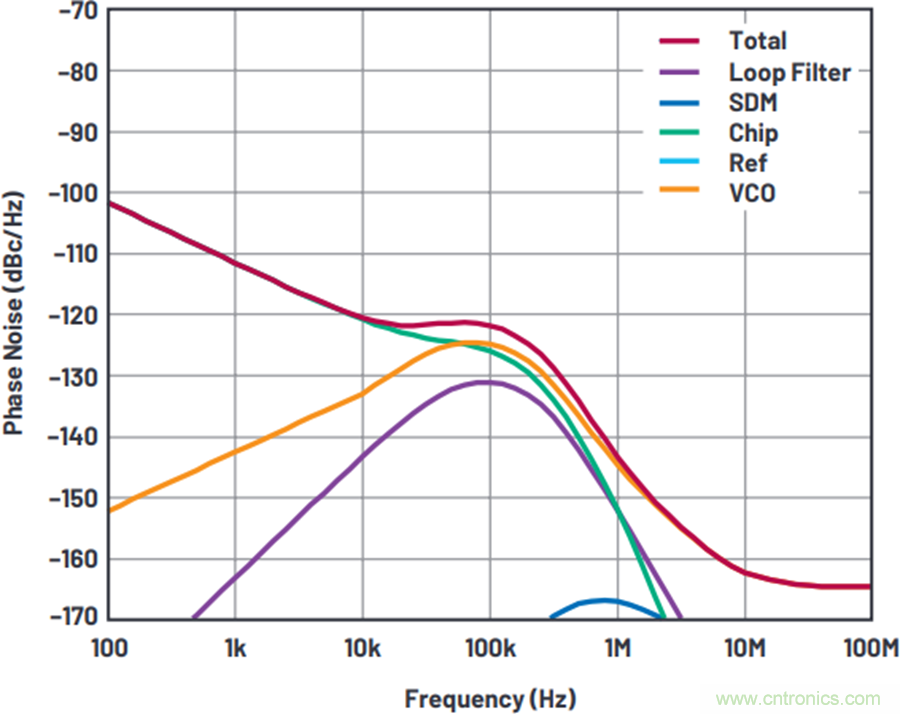

小数N分频还具有额外的优势,由于PFD频率更高,支持的环路带宽更宽,因此锁定时间更短。利用多个电荷泵失调电流和∑-?扰动功能,可将小数N杂散降低到可接受的水平。ADF4193和 ADF4153A分别支持26MHz和32MHz PFD频率,更高的PFD频率也允许用户进一步降低N,由于整数边界杂散(IBS)的发生率和影响较小,因此可进一步改善EVM并简化频率规划。ADF4371采用的最新PLL拓扑支持高达160MHz的PFD频率。小数N分频器件频率分辨率的改善(小数调制器从12位分辨率增加到39位分辨率)也意味着PLL可用于生成几乎所有分辨率达到毫赫(MHz),且精度极高的频率。

图7. ADF4371。

过去,使用小数N分频器件遇到的主要阻碍在于存在很高的小数杂散,这些杂散由∑-?调制器生成,会降低频谱纯度,因此需要工程师付出更多努力,以减少或消除其影响。由于ADF4371具有较低的小数杂散,并且没有整数边界,所以干净频谱意味着可以花费更少时间来研究、调试,或者从一定程度上消除了这些烦人的频率生成伪影带来的影响。较低的带内整数边界杂散(–55dBc)意味着一旦经PLL滤波器滤波,杂散就可以得到有效衰减。例如,如果将40kHz滤波器用于400 kHz信道栅,那么滤波器提供35dB衰减意味着距离整数边界最近信道的杂散为–90dBc。能够使用高达160MHz的高PFD频率意味着整数边界出现的几率更低,相比使用32MHz PFD频率,使用160MHz PFD频率时,其几率低5倍。

由于PFD频率和频率分辨率的提高,PLL品质因数(FOM)也有显著提升,例如从ADF4153的–216dBc/Hz提高到ADF4371的–233dBc/Hz(小数模式)。将图5和图7中的ADIsimPLL曲线进行比较,ADF4106在整数模式下,采用200kHz PFD频率设置,10kHz环路带宽,生成1.85GHz输出,而ADF4371则采用160MHz PFD频率设置,150kHz环路带宽。可以看出,在1kHz频偏时存在20dB的差异,PLL频率合成器技术取得明显进步。

同时可以看出,存在着1ps和51fs的集成rms相位抖动的差异。值得注意的是,与过去由电感Q决定rms噪声性能相比,带内噪声的大幅改善(通过低FOM和小数N分频实现)允许用户将环路滤波器带宽增加至150kHz,从而抑制此带宽内的VCO噪声,并降低10kHz至100kHz范围内的恶化,后者一般决定rms噪声。为实现这一带内相位噪声的改善目标,采用更高规格的PLL频率参考源至关重要,通过改进此类方法的性能和灵活性,大多数用户都能接受这种权衡考量方案。在某些情况下,新型小数N分频PLL提供的更低带内噪声可以和使用偏移或转换环路的PLL的结果相匹敌,后者在VCO至PFD的反馈路径中使用了混频器,可大大简化要求严苛应用的频率生成。

ADF4371VCO的基波频率范围为4GHz至8GHz,这是考虑了制造设备所使用的SiGe工艺的VCO相位噪声性能的最佳点。为了生成更高频率,我们使用了倍频器。通过重新设计VCO来实现双倍频率范围存在一定问题,因为噪声的降低幅度高于通过扩展VCO的频率范围所预期的6dB。所以,采用了倍频器,它将VCO范围从8GHz扩展到16GHz,还采用了四倍频器,将4GHz至8GHz的VCO范围扩展到16GHz至32GHz。在每种情况下,倍频器都会带来一些频率噪声,包括VCO馈通,以及2×、3×和5×VCO频率。为了降低滤波要求,每个倍频器电路都包含跟踪滤波器,以调谐输出,最大限度提高了所需频率与频率噪声的功效比。双倍输出的次谐波抑制一般低至45dB,四部输出则低至35dB。

宽带工作

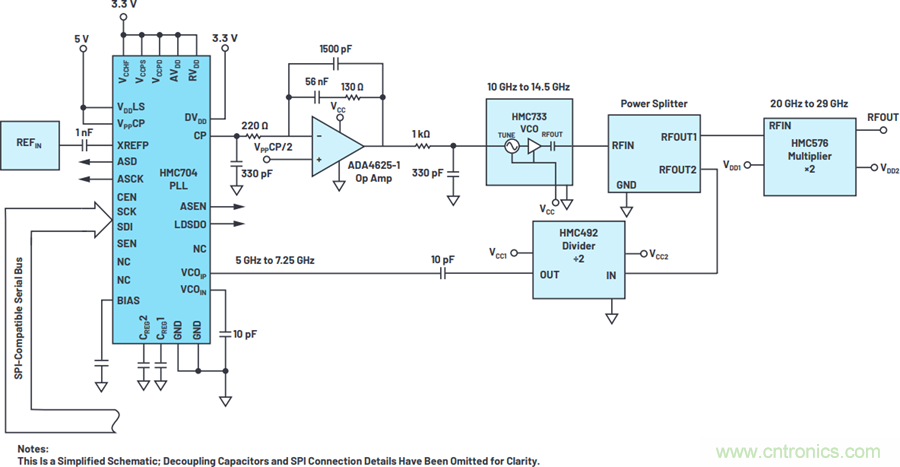

从之前所示的窄带示例中,可以看出新型PLL/VCO技术优势明显,但与使用HMC733VCO的HMC704PLL生成宽带频率相比,使用ADF4371还可以更进一步改善。用户使用分立式解决方案时面临诸多挑战,其目标是生成20GHz至29GHz的干净可变LO。

首先,HMC733VCO的输出功率必须在板上分配,并分频至适合HMC704的频率,所以必须使用外部分频器(如(HMC492),将10GHz至14.5GHz范围分频至HMC704允许的5GHz至7.25GHz。

然后,必须使用倍频器(如HMC576)将10GHz至15GHz频率范围倍增至20GHz至30GHz。

需要使用有源低通滤波器来生成HMC733所需的调谐电压。本示例使用ADA4625-1。这也要求运算放大器的电源电压高到足以生成所需的调谐调压(在本例中,为15 V)。

调谐灵敏度的变化必须在整个VCO频率范围内进行补偿。这通常通过调节电荷泵电流,以保持电荷泵增益和VCO增益的乘积来实现。

HMC576倍频器之后的VCO馈通约为–20dBc。ADF4371的调谐滤波器会将倍频器产生的不必要的频率抑制在35 dBc。这大大简化了后续滤波。

图8. 分立式PLL/VCO倍频器解决方案。

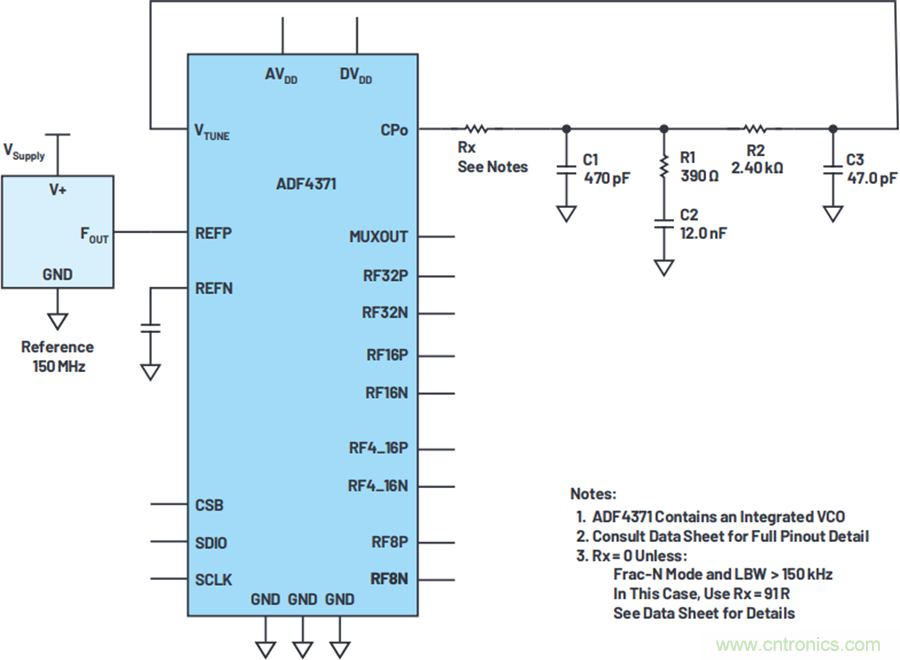

相比之下,ADF4371 PLL/VCO开箱即用,只需使用一个高品质的外部参考频率源,即可生成此频率。可以复制 EV-ADF4371SD2Z的布局,同时复制相应的电源管理解决方案。环路滤波器的设计也会明显简化,因为不需要最终用户补偿灵敏度(kV)的变化,也无需使用有源滤波器元件。用户无需花费数周时间来选择器件,也无需花费大量时间来为每个分立式组件构建仿真模型,他们可以直接使用ADIsimPLL来设计和仿真预期的性能,并通过ADF4371评估板来评估获取准确的预期结果,因为评估结果与仿真性能非常接近。更少的组件数量和更高的集成水平能够大幅改善系统的尺寸和重量,此外,也会大幅改善系统性能,计算得出的ADF4371集成rms抖动为60fs,而分立式解决方案的抖动为160fs。从图9可以看出,组件数量和电路板面积均明显节省,如果不包括必要的退耦电容和其他所需的无源器件,有源器件和功率分路器的总面积相当于96mm2,而ADF4371仅49mm2。用户也可以根据需要为VCO选择3.3V电源,以节省功率。

图9. ADF4371框图。

在基波VCO模式下,ADF4371的频谱纯度达到最高,无用杂散(非带内)仅限于VCO谐波。对于许多转换器时钟应用,方波本身的特性不会造成问题,可能确实合乎需要,但对于仪器仪表应用来说,宽带杂散频率一般必须低于50dBc。可调谐波滤波器可帮助消除这些谐波,专门设计的ADMV8416/ADMV8432非常适合对ADF4371的输出进行滤波。

ADMV8432是一款可调谐带通滤波器,指定中心工作频率范围为16GHz至32Ghz,典型 3dB带宽为18%,典型插入损耗为9dB,宽带抑制大于30dB,专为配合ADF4371四倍频器输出使用而设计。ADMV8416也是一款可调谐带通滤波器,工作频率范围为7GHz至16GHz,典型 3dB带宽为16%,典型插入损耗为8dB,宽带抑制大于30dB,可配合ADF4371倍频器输出使用。

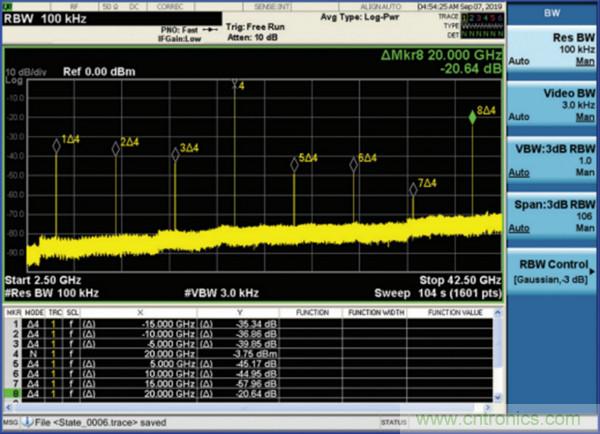

图10. ADF4371 20 GHz输出。

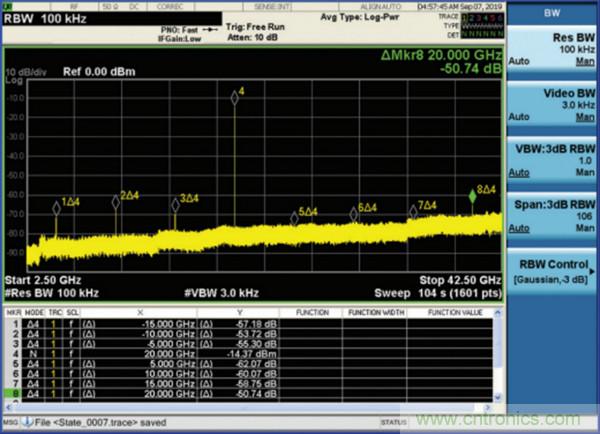

图11. 使用ADMV8432滤波器的ADF4371 20 GHz输出。

ADMV8416/ADMV8432均采用双重叠频段结构,带内部RF开关,可以实现更宽的频率覆盖范围,同时保持出色的抑制性能。频段选择通过对所需的电平转换器实施数字逻辑控制来实现。电平转 换器确保内部RF开关会进行相应的偏置,以获得高于+34dBm的最佳输入三阶交调截点(IIP3)。

在每个工作频段内,可调谐滤波器通过0V至15V的模拟控制电压进行控制,消耗的电流不到1µA。这种控制电压一般通过DAC和运算放大器驱动电路生成。例如AD5760DAC后接ADA4898运算放大器,可以为滤波器提供相对较快的调谐速度和低噪声驱动电压。如果调谐速度不太重要,则可以将DAC直接驱动至滤波器的调谐端口。

考虑到这些模拟调谐滤波器的性能指标,可以在牺牲少量输出功率的情况下,去除ADF4371频率合成器倍频器和四倍频器输出中的无用谐波成分。虽然为了解决插入损耗问题,可能需要额 外的放大级,但滤波器一般比分立式开关组解决方案要小,尤其在需要宽带可调谐性的情况下。此外,频率合成器的杂散电平在滤波前一般为–35dBc,滤波后可以达到–55dBc。未滤波且 未使用的输出的耦合可能会影响馈通,构建模型时应该非常小心,以实现滤波器IC的全阻带抑制。

结论

随着相关工艺、电路和封装技术的各种创新,频率生成技术不断发展,能够为用户提供比以前的分立式解决方案的体积更小、功能和性能更出色的解决方案。宽带频率工作趋势推动了新款IC的开发,即覆盖多个倍频率,频率范围高达32GHz。宽带PLL/VCO提供了很高的灵活性和简洁性,可以帮助最终用户大幅缩短设计时间和加快上市时间。

对频谱纯度的需求推动滤波IC不断创新,这些IC与新开发的频率合成器IC配合使用,可以提供现代无线应用所需的低相位噪声和高频谱纯度毫米波信号源。用户可以使用免费的仿真工具ADIsimPLL来评估和比较PLL性能,还可以使用简单易用、具有直观界面的快速行为模型帮助进行组件选型。这款工具为设计工程师节省了大量时间,使他们无需构建大量不同领域的数学模型来预测性能。

推荐阅读:

3.6V输入、双路输出μModule降压稳压器以3mm × 4mm小尺寸为每通道提供2A电流

头部中外厂商集结,SENSOR CHINA打造传感器供应链全联接时代

如何使用Fly-buck为低电压、低功耗工业应用供电

对您的LED进行高效调光,无需检测电阻器

何时选用多相位