如何利用功率放大器实现功放记忆效应电路的设计?

品慧电子讯功率放大器非线性特性产生的失真分量不恒定,例如三阶或五阶交调的幅度、相位会随输入信号幅度和带宽的变化而改变。这种失真分量依赖于输入信号幅度、带宽的现象通常称之为功率放大器的记忆效应。

1、 功率放大器记忆效应产生原因及影响

功率放大器非线性特性产生的失真分量不恒定,例如三阶或五阶交调的幅度、相位会随输入信号幅度和带宽的变化而改变。这种失真分量依赖于输入信号幅度、带宽的现象通常称之为功率放大器的记忆效应。

轻微的记忆效应本身对功率放大器的线性度并无严重影响。即在双音频测试中,随着音频间隔的增加,如果放大器三阶交调分量的相位旋转不超过10o,且幅度起伏不大于0.5dB,此时功放的记忆效应不会明显影响邻近信道功率比,可以不予考虑。然而,当功率放大器的上下边带的ACPR(an adjacent channel power ratio,相邻信道功率比)出现较大不对称现象时,即使三阶、五阶交调分量的相位和幅度失真很小,也不能忽略记忆效应对放大器的影响。

2 、减弱功放记忆效应的基本思路

功放记忆效应使射频预失真线性化功率放大器的效果有很大退化,为增强射频预失真线性化功率放大器的稳定性和可靠性,需对所设计的功率放大器进行减弱记忆效应的相关处理。

降低记忆效应的基本想法是:通过附加电路滤除由包络和二次谐波控制的三阶交调分量。最简便的方法是在四分之一波长传输线后面的偏置线上,添加辅助电路使包络信号和二次谐波短路,但由于传输线的离散作用,使得这种方法难以实现宽带短路。因此,短路电路网络应当直接加在紧靠栅极和漏极的地方,而不必经过四分之一波长传输线才短路。短路网络可使用LC串联电路实现。

3、 采用附加电路法减弱功放记忆效应分析

使用附加电路滤除由包络和二次谐波控制的三阶交调分量,对减小功率放大器的记忆效应是有效的,现分析如下:

假设信号的中心频率为f_{0}、带宽为f_{U}-f_{L},并带有二次谐波和包络分量。它的频谱如图1所示。

通过利用功率放大器减弱功放记忆效应电路的设计

信号的中心频率可表示为

f_{0}=frac{f_{U}+f_{L}}{2}≈sqrt{f_{U}f_{L}} (1)

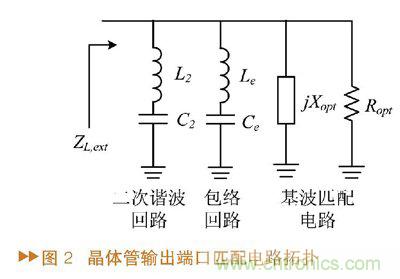

晶体管的一种理想输出端口匹配电路拓扑如图2。

输入端口的匹配电路拓扑同样采用上面的结构。图中包括滤除二次谐波和包络的LC谐振回路和基波的最优匹配电路。为了使滤除二次谐波的LC谐振回路对二次谐波2f_{U}和2f_{L}具有相同的阻抗,则L2与C2组成的谐振回路须在频率2sqrt{ω_{U}ω_{L}}处振荡,即

L_{2}C_{2}=1/(4ω_{U}ω_{L})≈1/(2ω_{0})^{2} (2)

假设滤除包络的LC谐振回路和基波匹配电路的阻抗在二次谐波频率处非常大,则输出负载阻抗Z_{L},_{ext}(2f_{U})和 Z_{L},_{ext}(2f_{L})是共轭的,它们的模为

∣Z_{L,ext}(2f_{U})∣=∣Z_{L,ext}(2f_{L})∣=4πL_{2}(f_{U}-f_{L}) (3)

显然,Z_{L,ext}(2f_{U})和Z_{L,ext}(2f_{L})与电感L2和信号带宽有关。

为了将包络信号短路,须使用一个大电容Cg。同样地,假设滤除二次谐波的LC回路和基波匹配电路在信号带宽频率处的阻抗非常大,则Z_{L,ext}(f_{U}-f_{L})的模可表示为

∣Z_{L,ext}(f_{U}-f_{L})∣=2πL_{e}(f_{U}-f_{L}) (4)

若电感L2与Le的值相同,那么阻抗Z_{L,ext}(f_{U}-f_{L})将是Z_{L,ext}(2f_{U})的二分之一。最后,需要匹配的优化基波阻抗为

jX_{opt}(ω)=[jωL_{2}+1/(jωC_{2})]// jωL_{e}// jωC_{ds} (5)

其中ω_{L}≤ω≤ω_{U},如果滤除二次谐波和包络的LC谐振回路在基波频率处的阻抗非常小,则在实际中难以将这个优化基波阻抗匹配到实际的负载阻抗,故匹配的难度将限制L2、Le和C2的取值。根据要求,可以得到滤除二次谐波和包络的LC谐振回路的最小阻抗值。因此,在设计短路网络的时候,应注意使滤除二次谐波和包络的LC谐振回路在基波频率处的阻抗要大于这个最小值。

4、 某军用集群系统基站降低功放记忆效应的实现

军用集群系统所用的频率范围一般为400~420MHz,其基站的功率放大器通常使用封装后的晶体管,故实际中不得不考虑封装引脚的电感效应。当和外部匹配电路配合使用时,封装引脚的寄生电感具有改善晶体管的稳定性、增加有用带宽的优点。以MRF5P21180HR6 LDMOSFET为例,这种晶体管由两个90W的功率单元构成,能达到180W的功率峰值。封装后单个功率单元的等效电路如图3所示。

在包络这种低频下,小电容的阻抗非常大,并联结构中可忽略不计。则针对包络分量的阻抗和频率ω、Lg1、Lg2和Ld2有关系,并可求出阻抗Z_{S,ext}(f_{U}-f_{L})和Z_{l,ext}(f_{U}-f_{L})的表达式:

∣Z_{S,ext}(f_{U}-f_{L})∣=2π(L_{g1}+L_{g2}+L_{e})(f_{U}-f_{L}) (6)

∣Z_{S,ext}(f_{U}-f_{L})∣=2π(L_{d2}+L_{e})(f_{U}-f_{L}) (7)

另一方面,对于二次谐波分量,栅极和漏极外相应的阻抗Z‘_{S,ext}(ω=2ω_{1}≈2ω_{2})和Z’_{L,ext}(ω=2ω_{1}≈2ω_{2})的表达式为,

Z‘_{S,ext}(ω=2ω_{1}≈2ω_{2})=-﹛1/jωC_{pad}/2)//[jωL_{g2}+ (jωL_{g1}//1/jωC_{g,mos})]﹜(8)

Z’_{L,ext}(ω=2ω_{1}≈2ω_{2})=?[1/(jωC_{pad}/2)//jωL_{d2} (9)

等式(8)、(9)很容易用包含串联LC谐振回路的匹配电路实现,这是因为二次谐波分量的相对带宽要比包络分量的相对带宽窄得多,故滤除包络分量比滤除二次谐波分量的难度更大。因此,包络分量对记忆效应的作用要比二次谐波分量更大。在实际应用中,由于包络分量对功率放大器的记忆效应起主要作用,故一般只对滤除包络分量的辅助电路进行优化,高频下可用某些寄生参数较强的大电容(如钽电容)来代替滤除包络分量的串联LeCe谐振回路。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请电话或者邮箱联系小编进行侵删。

推荐阅读:

Silent Switcher技术解决电磁干扰,提高效率

如何调节MAX2009/MAX2010 RF预失真器来优化系统性能?

嘿,这里有测量小型封装芯片温度的4个方法~

单电感多输出(SIMO)开关稳压器技术

车载供电系统发展方向:48V与分布式