CMOS轨到轨放大器电路

品慧电子讯从数十年前被发明以来,MOS 晶体管的尺寸已经被大大缩小。门氧化层厚度、通道长度和宽度的降低,推动了整体电路尺寸和功耗的大大减少。由于门氧化物厚度的减小,最大可容许电源电压降低,而通道长度和宽度的缩减则缩小了产品的外形并加快了其速度性能。

从数十年前被发明以来,MOS 晶体管的尺寸已经被大大缩小。门氧化层厚度、通道长度和宽度的降低,推动了整体电路尺寸和功耗的大大减少。由于门氧化物厚度的减小,最大可容许电源电压降低,而通道长度和宽度的缩减则缩小了产品的外形并加快了其速度性能。这些改进推动了高频率 CMOS 轨到轨输入 / 输出放大器的性能发展,以满足当今系统设计者对于某种新型模拟电路日益增加的需求,这种电路必须能够以和数字电路同样低的电源电压进行工作。

本应用笔记解答了有关最新一代 CMOS 轨到轨放大器的一些独特问题。文章一开始大致讨论并讲述了传统电压反馈和电流反馈放大器电路的拓扑,以及导致反馈放大器振荡的最常见原因。为了方便分析和讨论,我们将 CMOS 轨到轨放大器电路分成 4 大块:输入、中间增益、输出和反馈网络阶段。文中将展示每个阶段受频率影响的增益和相位移,随后展示并讨论一个包含了所有 4 大基本电路区块的完整系统仿真。而第二部分则将展示并讨论三种用于解决放大器振荡问题的使用方案的机制、各方面的折衷和优势。

电压反馈放大器

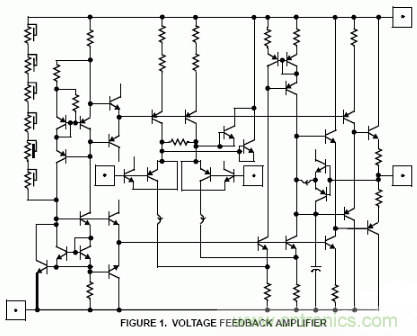

图 1 展示了一个 EL5157 的简化方案 - 这是一款非常流行的高带宽电压反馈放大器。这一方案采用一个经典的差分输入阶来驱动折叠的 Cascode 第二阶,由第二阶在高阻抗增益节点上将输入阶的差分电压转换成一个电流,该电流随着放大器的高电压增益而实现。从本质上来讲,在高阻抗节点上变成一个输出信号的第二阶电流源输出阻抗会增加任何在信号通道晶体管内产生的电流差距。输出阶是一个推挽式 AB 级缓冲器,将高电压增益缓冲成放大器的单端输出。

图 1:电压反馈放大器

输出感应

感应器是一种阻抗受频率影响的电子元器件:低频率时其阻抗较低,高频率时阻抗则升高。“理想的”运算放大器输出阻抗是零,但在实际中放大器的输出阻抗是感应式的,就像感应器一样会随着频率的增加而增加。图 2 展示了 EL5157 的输出阻抗。利用运算放大器的应用中所经常遇到的一个挑战,就是驱动一个电容性负载。之所以具有挑战性,是因为运算放大器的感应输出会与电容性负载联合生成一个 LC 谐振回路拓扑,而在这个拓扑中电容性负载会与感应式驱动阻抗一起,当反馈围绕回路关闭时造成额外的相位滞后。相位余度的缩小有可能导致放大器的振荡。在振荡时,放大器会变得非常热,甚至可能自毁。要解决这一问题,有多种非常著名的方案。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请电话或者邮箱联系小编进行侵删。

推荐阅读:

微带线的相位补偿电路物理模型分析

通科:追求产品品质,真诚对待客户

维信诺:占据先发优势引领OLED产业发展

多重因素交织,从CITE 2020看中国集成电路如何“乘风破浪”

采用不同的测量方法和连接方式对电阻进行有效测量