5G基站应用的复杂性正在推动低EMI DC/DC模块的需求增长

品慧电子讯目前,智能家居、工业自动化、自动驾驶、医疗保健、智能可穿戴设备等智能连接设备和智能手机对于数据容量需求的不断增长,为了满足这一需求,5G电信标准应运而生。通过使用“大规模多输入多输出”(massing-MIMO)天线阵列,5G让每个基站能够进行更多的数据连接。

现有的4G基站,每个阵列最多使用四个发射器和四个接收器(4x4 MIMO)。与之相比,预计采用大规模MIMO阵列的5G基站,每个阵列可使用多达64个发送器和64个接收器。加之每个基站节点有更多的信道,5G网络能比4G网络的数据传输速率高100倍,并且网络延迟低至1ms。

这将意味着每个5G基站需要更多的调制解调器,数据转换器和高速基带数字处理器,也就不可避免地需要更多的电源供给。预估表明,5G基站可能比现有4G基站多三倍的功率需求,需要硬件设计师找到合适的电源解决方案,为新增的处理器供电,并将所有元器件能被压缩到和现有4G基站机壳差不多的尺寸中。对比传统分立式 DC / DC IC和外部电感的解决方案,5G基站的电路板组件密度要求更高,尺寸要求更小,且需要实现更高的效率和更低的EMI。

基站的输入电压通常为48V,该电压被DC / DC转换器降压至24V或12V,然后进一步降压到多个电源轨,范围从3.3V至1V以下,这些电源轨为基带处理器中的ASIC电路供电。

传统的电源解决方案是使用分立式降压DC/DC变换器,采用一个控制IC,使用内置或者外置的功率MOSFET,再加上外部电感和电容等元件,产生所需的电源轨。由于5G基站需要的电源轨众多,如果使用传统的解决方案,产生这些电源轨将会是一个非常复杂而耗时的任务。不仅必须要考虑每个转换器的电感尺寸和结构、输入输出电容容值、输入滤波,还要考虑到其他因素,例如工作频率和时序等问题。

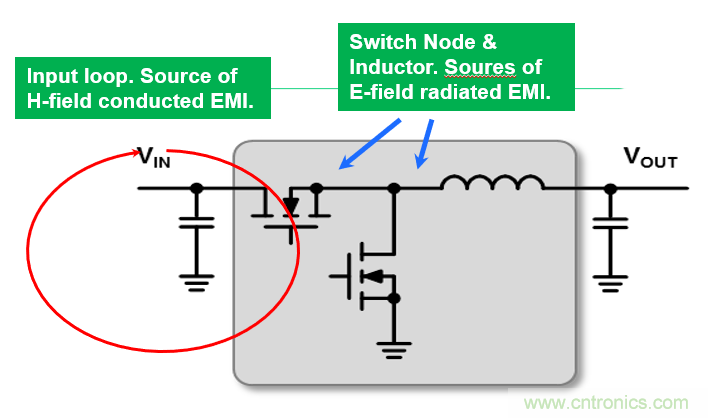

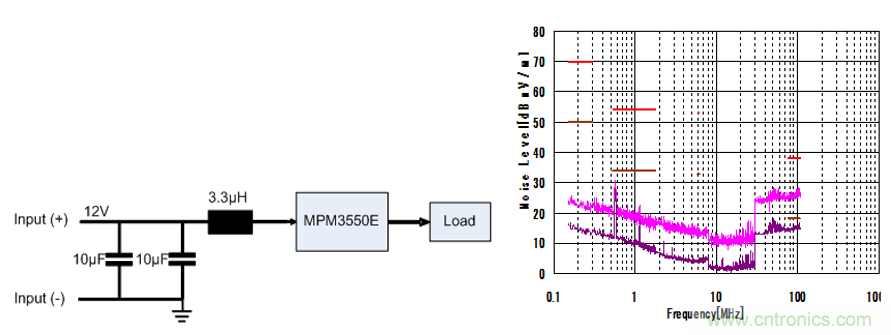

同时,为了减少开关电流引起的传导和辐射EMI,还需要精心对元件布局和放置滤波器组件。DC / DC转换器通常会通过电流回路中的磁场产生传导EMI,而电流回路主要形成在输出功率MOSFET开关节点与地之间以及输入电容与地之间。MOSFET开关节点与电感连接处也会产生辐射电场EMI,由于需要不断在输入电平与地电平切换,因此dV / dt很高,并且电感本身产生的电磁场也会产生辐射(见图1)。

图 1:DC / DC降压转换器的典型EMI噪声源

如果设计不当,会造成极其耗时耗费的设计迭代和重复EMI测试。

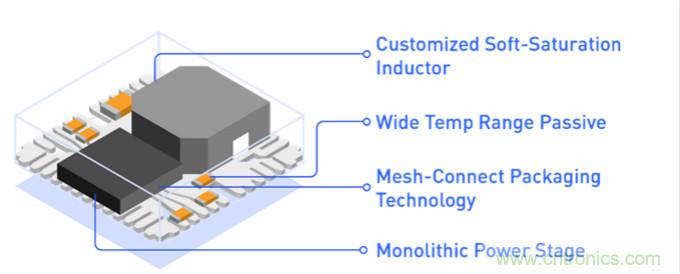

为了简化设计并加快产品上市速度,一种替代的解决方案是在每个电源轨上使用独立的DC / DC转换器模块。随着半导体工艺技术和封装结构的进步,MPS最新一代的DC / DC模块可以实现小尺寸、高功率密度、高效率和良好的EMI性能。同时,新的封装技术,例如倒装工艺和“mesh-connect”引线框架技术,可以将IC、电感和无源器件直接安装在引线框架上,无需打线或额外的内部PCB (见图二)。

图2:集成模块DC / DC降压变换器结构

引线框架结构优点明显,它可以更好地控制EMI,改善散热,并能减少占板面积。

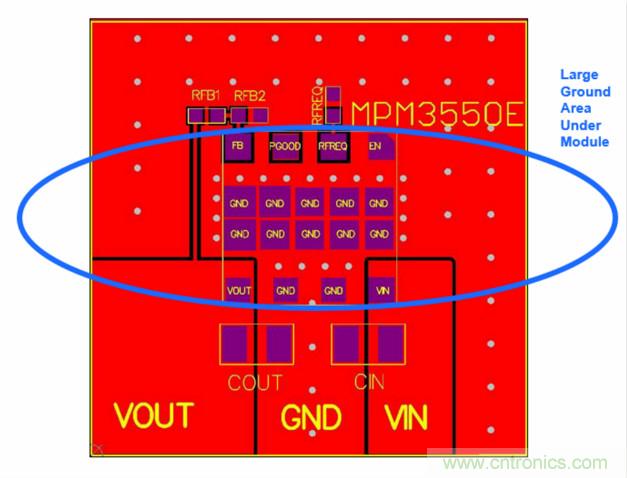

与采用内部PCB基板或打线的结构相比,此种结构可以最大限度地减少走线长度,并能直接连至无源元件,大大降低了寄生电感,减少了EMI。而且表面直接贴装在目标PCB上的焊盘栅格阵列(LGA)封装,和SIP/SIL封装的变换器相比,其EMI更少,因为SIP/SIL封装的引脚会辐射EMI。同时,LGA封装允许接地层覆盖模块下方的大部分区域,有助于闭合涡流环路而进一步降低EMI(见图3)。 对于有些类型的模块电源,其金属外壳还可以减少额外的EMI辐射。

图 3:模块较大接地层面积有助于降低EMI

T使用铜柱直接将MOSFET裸片的源极和漏极连接到模块的引线框架上,可以改善从功率MOSFET到目标PCB覆铜的热传导,实现更小的模块尺寸,而传统结构中的打线或内部电路板结构则会阻碍散热。

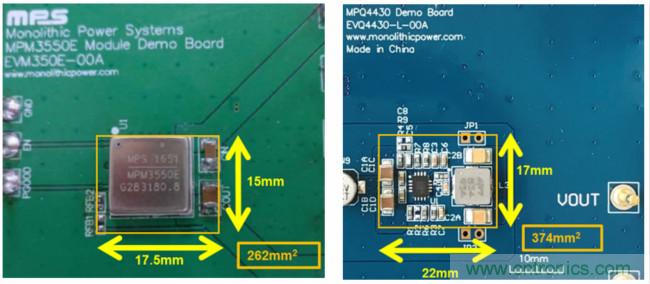

MPS 产品MPM3550E采用集成模块的方法,大大节省了布板空间。该模块可以在 1V 至 12V 可调输出电压范围内实现 5A 的最大持续输出电流,最大输入电压高达36V,采用尺寸为12mmx12mmx4.2mm 的LGA封装。

与带有外部电感和无源元件的传统36V、3.5A分立式DC / DC布局相比,MPM3550E的占板面积可节约30%的空间 (见图四)。

图 4: DC / DC降压模块尺寸对比传统分立式DC / DC解决方案尺寸

除了节省空间外,设计人员也无需再考虑独立元件的选型或转换器的布局。这些问题已经在MPS的模块设计时被考虑。MPS的电源模块集成了软饱和磁芯的封闭式磁路电感、优化的电流环路和集成输入滤波,能大大简化最终设计,确保满足辐射和传导EMI要求。

由两个10μF电容和一个3.3μH电感的组成的LC低通滤波器,足以满足传导发射规范,包括CISPR22 Class B 和CISPR25 Class 5规范 (见图5)。

图 5:带有外部EMI滤波器的模块性能图及传导EMI结果

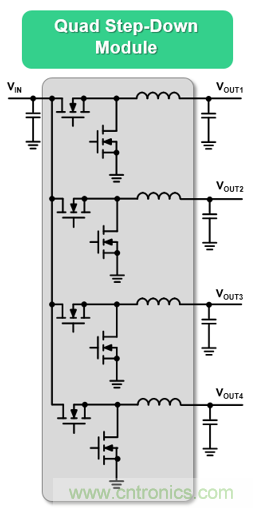

为了进一步节省电路板空间,一种可行的办法是将多个DC/DC变换器集成到一个模块中。这尤其适用于低压电路,例如ASIC。较低的功率等级允许多个变换器集成到一个模块的同时,仍能实现可控的功率密度和功耗水平。(见图六,图七)。

图 6:集成4个DC/DC变换器模块示例

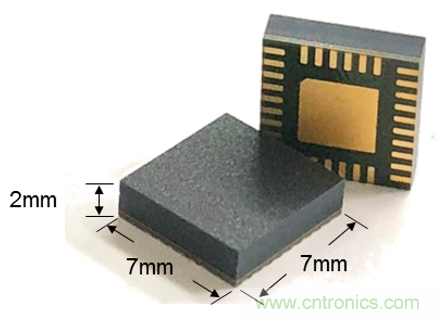

图 7:集成4个DC/DC模块的小尺寸封装图

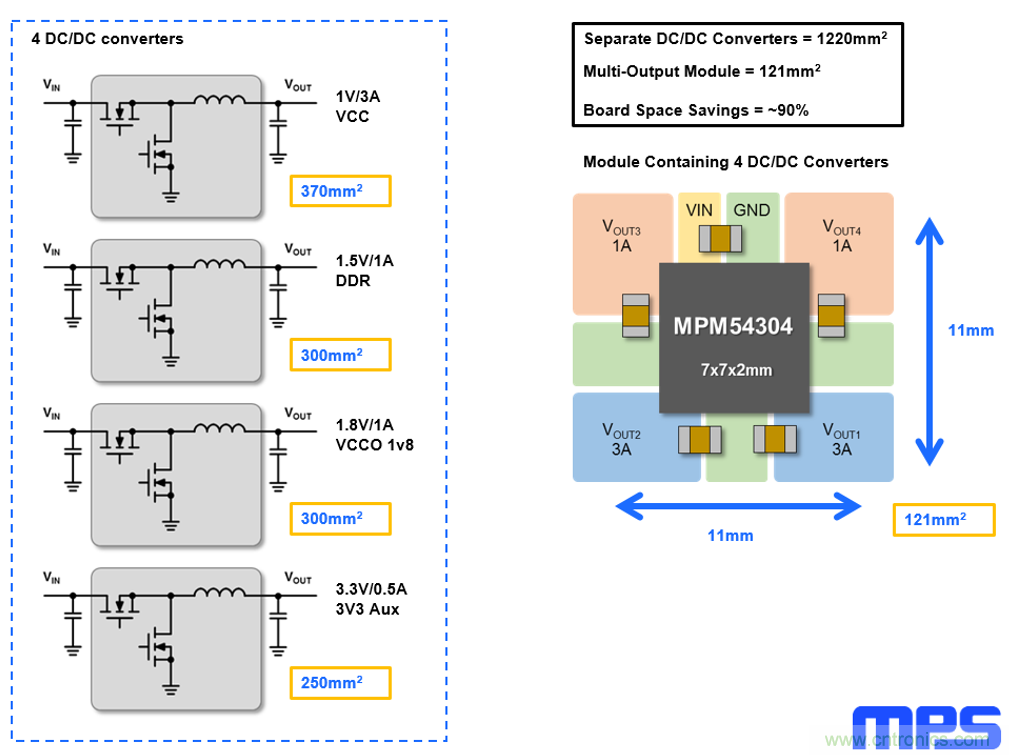

与使用独立DC/DC电源变换器的解决方案相比,采用多电源轨模块方案,可以节约高达90%的占板面积。图8显示的是MPS 的电源模块MPM54304,与四个分立的降压转换器占用面积的比较,MPM54304将四个降压转换器包括电感和无源元件集成在单个7mmx7mmx2mm模块中。

图 8:四个分立式DC / DC转换器与MPM54304的占板空间的比较

毋容置疑的是,5G基带和无线电板设计对于元件集成度和功率密度的要求更高,同时还会受到安装机柜尺寸和无线电天线杆负载能力的限制。而使用DC / DC集成模块可以帮助节省电路板空间,简化布局和降低EMI。 综上所述,MPS的解决方案不但可以降低设计风险,还能缩短产品上市时间。

推荐阅读:

安森美半导体任命Bernie Colpitts为首席会计官

利用工业以太网连接技术加速向工业4.0过渡

高分辨率数字系统中的电阻器

现可轻松用于高精度电路中的零漂移放大器

二阶系统的运算放大器总输出噪声计算