精密逐次逼近型ADC基准电压源设计

品慧电子讯高分辨率、逐次逼近型ADC的整体精度取决于精度、稳定性和其基准电压源的驱动能力。ADC基准电压输入端的开关电容具有动态负载,因此基准电压源电路必须能够处理与时间和吞吐速率相关的电流。某些ADC片上集成基准电压源和基准电压源缓冲器,但这类器件在功耗或性能方面可能并非最佳——通常使用外部基准电压源电路才可达到最佳性能。本文探讨基准电压源电路设计中遇到的挑战和要求。

基准电压输入

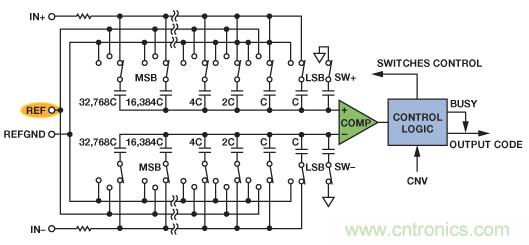

逐次逼近型ADC的简化原理图见图1。采样间隔期间,容性DAC连接至ADC输入,并且与输入电压成比例的电荷被存储在电容器中。转换开始后,DAC从输入端断开。转换算法逐个开关每一位至基准电压或地。电容上的电荷再分配可导致电流流入或流出基准电压源。动态电流负载是ADC吞吐速率和控制位检验的内部时钟的函数。最高有效位(MSB)保持大部分的电荷,需要大部分电流。

图1. 16位逐次接近型ADC原理简化图

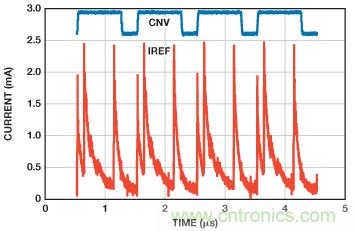

图2显示AD7980、16位、1 MSPS、PulSAR®逐次逼近型ADC基准电压输入端的动态电流负载。通过观察基准电压源和基准电压引脚之间500 Ω电阻上的电压降,得出测量值。曲线显示电流尖峰高达2.5 mA,并且在整个转换期间分布着较小的尖峰。

图2. AD7980动态基准电流

若要支持该电流,同时保持基准电压的无噪声特性,需在尽可能靠近基准电压输入放置一个高数值、低ESR的储能电容,通常为10 µF或更大。较大的电容会进一步平滑电流负载,并降低基准电压源电路的负担,但极大的电容会产生稳定性问题。基准电压源必须要能提供灌满基准电容所需的平均电流,而不会导致基准电压下降过大。在ADC数据手册中,基准输入电流平均值通常在特定的吞吐速率下指定。例如,在AD7980数据手册中,将1 MSPS下5 V基准电压源的平均基准电流指定为330 µA典型值。两次转换之间不消耗电流,因此基准电流随吞吐速率成线性变化,在100 kSPS时降至33 µA。基准电压源——或基准电压缓冲器——在最高的目标频率下必须具有足够低的输出阻抗,以便在ADC输入端保持电压水平,使电压不至于因为电流而产生太大的压降。

基准电压源输出驱动

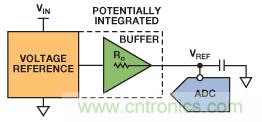

图3显示典型的基准电压源电路。基准电压源可集成具有足够驱动电流的缓冲器,也可采用适当的运算放大器作为缓冲器。为避免转换误差,特定吞吐速率下所需的平均电流不应使基准电压下降超过½ LSB。该误差在突发转换中最为明显,因为此吞吐速率下基准负载将从零变化到平均基准电流。

图3. 典型精密逐次逼近型ADC基准电压源电路

AD7980为16位ADC,其IREF = 330 µA , VREF = 5 V;使用该ADC作为确定基准电压源是否具有足够驱动能力的示例,则对于½ LSB压降,最大允许输出阻抗为:

大部分基准电压源不指定输出阻抗,但会指定负载调整率,通常以ppm/mA表示。将其乘以基准电压并除以1000即可转换为输出阻抗。例如,"ADR435 超低噪声XFET® 5-V 5 V基准电压源指定流出电流时的最大负载调整率为15 ppm/mA。转换为电阻,可得:

![]()

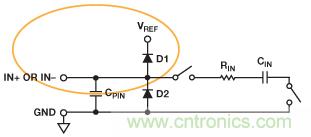

因此,就输出阻抗而言,ADR435应该足够了。它可流出的最大电流为10 mA,足够处理330 µA的平均基准电流。当ADC输入电压超出基准电压,哪怕只有很短的一段时间,它也会向基准电压源注入电流,因此基准电压源必须要能吸取一定量的电流。图4显示ADC和基准电压输入之间的二极管连接,在输入超量程条件下它可造成电流流入基准电压源。与某些老的基准电压源不同,ADR435能吸收10 mA电流。

图4. AD7980模拟输入结构

由于基准电流的参数要求与吞吐速率成线性关系,较低的吞吐速率或使用较低吞吐率的ADC(如500 kSPSAD7988-5 或100 kSPSAD7988-1 (IREF = 250 µA)时,可采用较高输出阻抗(功耗较低)的基准电压源。通过降低基准电流,可算出最大输出阻抗。请注意,这些公式仅作参考准则,对选择的基准电压源必须测试硬件驱动能力。

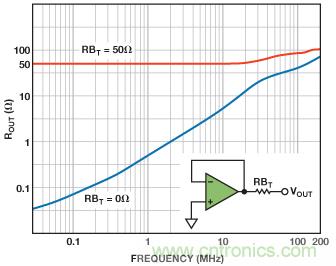

当所选基准电压源的驱动能力不够时,或者首选微功耗基准电压源时,可使用基准电压缓冲器。可通过将适当的运算放大器配置为单位增益而实现。运算放大器必须具有低噪声和适当的输出驱动能力,并且要能够稳定工作在较大容性负载下。它还必须要能提供所需电流。通常不指定运算放大器的输出阻抗,但一般可通过输出阻抗与频率的关系图确定,如图5中的AD803180 MHz轨到轨运算放大器所示。

图5. AD8031ROUT 与频率

位于100 kHz以下,则输出阻抗低于0.1 Ω;而直流时则低于0.05 Ω,因此就我们1 MSPS下驱动AD7980的示例而言,它是不错的选择。在宽频率范围内保持低输出阻抗对于驱动基准电压输入而言非常重要。即便是较大的电容值,储能电容也永远无法消除基准电压输入端消耗的电流。电流纹波的频率成分是吞吐速率和输入信号带宽的函数。大储能电容处理与吞吐速率相关的高频电流,而基准电压缓冲器必须能够在最大输入信号频率(或储能电容阻抗变得足够低,可提供所需电流的频率)保持低阻抗。基准电压源数据手册中的典型曲线显示输出阻抗与频率的关系,选择基准电压源时应加以考虑。

AD8031就是一个很好的选择,它在容性负载大于10 µF时性能稳定。其它运算放大器(比如ADA4841也会在大电容下稳定,因为它们主要驱动稳定的直流电平,但某些特定的运算放大器必须测试确定加载特性。在电容之前使用串联电阻以保持稳定并不是个好主意,因为这会增加输出阻抗。

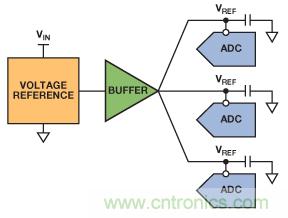

以一个基准电压源驱动多个ADC时,基准电压缓冲器非常有用,比如图6中显示的同步采样应用中的情形。

图6. 基准电压源电路驱动多个ADC

所有ADC基准电压输入都有各自的储能电容,尽可能靠近基准电压输入引脚放置。每条从基准电压输入出发的走线经路由后返回位于基准电压缓冲器输出端的星型连接,最大程度降低串扰效应。具有低输出阻抗和高输出电流能力的基准电压缓冲器可驱动许多ADC,具体取决于电流要求。请注意,缓冲器必须要能在额外电容下稳定,该额外电容与多个基准电压电容有关。

噪声和温度漂移

一旦确定了驱动能力,必须确保基准电压源电路的噪声不影响ADC性能。为了保持信噪比(SNR)和其它规格,必须将基准电压源噪声贡献限定为ADC噪声的一小部分(比较理想的是20%或更低)。AD7980集成5 V基准电压源,额定SNR为91 dB。转换为rms可得:

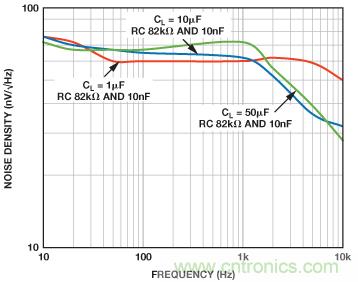

因此,基准电压源电路应具有不超过10 µV rms的噪声,以便最大程度减少对SNR造成的影响。基准电压源和运算放大器的噪声规格通常可分为两部分:低频噪声(1/f)和宽带噪声。结合这两部分可得到基准电压源电路的总噪声贡献。图7显示ADR4312.5 V基准电压源的典型噪声与频率关系曲线图。

图7. 带补偿网络的ADR431噪声曲线

ADR435补偿其内部运算放大器,驱动大容性负载并避免噪声峰化,使其非常适合与ADC一同使用。更详尽的叙述可参见数据手册。采用10 µF电容,其噪声额定值为8 µV p-p 1/f(0.1 Hz至10 Hz),宽带噪声频谱密度为115 nV/√Hz。估计噪声带宽为3 kHz。若要将1/f噪声从峰峰值转换为均方根(rms),可除以6.6:

![]()

然后,使用10 µF电容下的估计带宽计算宽带噪声贡献。有效带宽由下式确定:

![]()

使用该有效带宽计算rms宽带噪声:

![]()

总rms噪声是低频噪声和宽带噪声的平方和开根:

![]()

结果低于10 µV rms,因此不会对ADC的SNR造成太大影响。这些计算可用来估算基准电压源的噪声贡献,以判断其稳定性,但需要在工作台上使用真实硬件对数据进行验证。

若缓冲器在基准电压源之后使用,则同样的分析可用于计算噪声贡献。例如,AD8031具有15 nV/√Hz的噪声频谱密度。由于输出端具有10 µF电容,其测量带宽下降至大约16 kHz。使用此带宽和噪声密度,同时忽略1/f噪声,则噪声贡献为2.4 µV rms。对基准电压源缓冲器噪声和基准电压源噪声进行平方和开根计算,即可得到总噪声的估算值。通常,基准电压源缓冲器的噪声密度远低于基准电压源噪声密度。

使用基准电压源缓冲器时,可通过在基准电压输出添加一个极低截止频率的RC滤波器,对来自基准电压源的噪声进行带宽限制,如图8所示。考虑到基准电压源通常是噪声的主要来源,这样做可能会非常有效。

图8. 带RC滤波的基准电压源

选择基准电压源时的一些其它重要考虑因素包括初始精度和温度漂移。初始精度以%或mV为单位。许多系统允许校准,因此初始精度不如漂移那么重要,而漂移通常以ppm/°C或µV/°C为单位。大多数优秀的基准电压源漂移低于10 ppm/°C,而ADR45xx系列更是将漂移驱动至仅有数ppm/°C。该漂移必须纳入系统误差预算中。

基准电压源故障排除

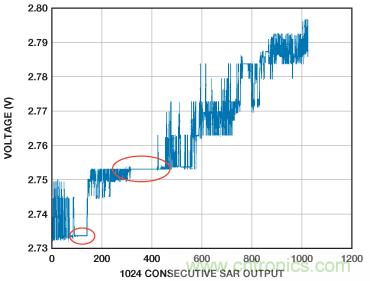

设计不佳的基准电压源电路可能导致严重的转换错误。最常见的基准电压源问题是来自ADC的重复或"粘连"代码问题。当基准电压源输入端噪声足够大,便可能造成ADC作出错误的位判断。哪怕输入有所改变,它也以同样的代码重复出现多次,或者在较低的有效位中填充重复的1或0字串,如图9所示。红色圆圈区域中,ADC出现粘连,重复返回相同的代码。通常满量程附近的问题更严重,因为基准电压源噪声对较高有效位的判断产生的影响更大。一旦作出错误的位判断,其余位便填充1或0。

图9. ADC传递函数中的"粘连"代码

导致出现"粘连"位的最常见原因是基准电压源电容的尺寸与位置、基准电压源/基准电压源缓冲器的驱动能力不足,或是基准电压源/基准电压源缓冲器选型不当导致过量噪声。

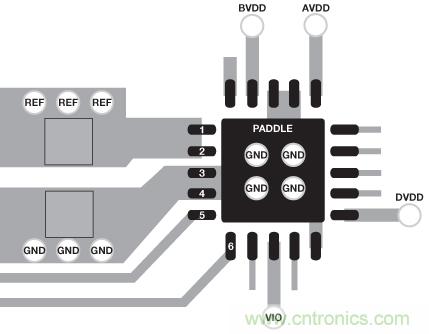

将储能电容放置在ADC的基准电压源输入引脚附近并使用宽走线实现连接很重要,如图10所示。使用多个过孔将电容连接至接地层,可获得较低的阻抗路径。若基准电压源具有专用地,则电容应当通过宽走线连接至该引脚附近。由于电容用作电荷库,它必须足够大,以限制衰减,并且必须具有低ESR特性。具有X5R电介质的陶瓷电容是个不错的选择。电容典型值为10 µF至47 µF范围内,但根据ADC的电流要求,有时也可使用较小数值的电容。

图10. 典型基准电压源电容布局

驱动能力不足是另一个问题,特别是使用低功耗基准电压源或微功耗基准电压源缓冲器,因为它们通常具有高得多的输出阻抗,随频率而明显增加。使用吞吐速率较高的ADC时,这个问题尤其明显,因为吞吐速率较低时,电流要求更高。

来自基准电压源或基准电压源缓冲器的过量噪声与转换器的LSB大小有关,也可能会造成粘连代码,因此基准电压源电路的电压噪声必须保持为LSB电压的一小部分。

结论

本文讨论了如何针对精密逐次逼近型ADC设计基准电压源电路,并强调了如何判断某些常见问题。文中的计算公式用于估算基准电压源电路的驱动能力和噪声要求,以便有更高的概率使该电路通过硬件测试。

参考电路

AN-931 Application Note. “Understanding PulSAR ADC Support Circuitry.”

Kester, Walt. Data Conversion Handbook, Chapter 7. “Data Converter Support Circuits.”

Kester, Walt. “Which ADC Architecture Is Right for Your Application?” Analog Dialogue. Volume 39, Number 2, 2005.

Walsh, Alan. “Front-End Amplifier and RC Filter Design for a Precision SAR Analog-to-Digital Converter.” Analog Dialogue. Volume 46, Number 4, 2012.

推荐阅读:

可编程增益跨阻放大器使光谱系统的动态范围达到最大

瑞萨电子支持Microsoft Azure RTOS,实现快速、无缝且开箱即用的云连接

贸泽电子再次荣膺TE年度全球卓越服务分销商奖

深度解读UWB技术:厘米级安全实时定位是如何实现的?

适用于滑环应用的60 GHz无线数据互联