如何提高系统的ESD的承受能力?

品慧电子讯ESD关乎电路的生存,但您也应该考虑功能性的干扰。这也许包括需很长恢复时间的模拟电路过载。在数字电路或系统处理器中的受干扰比特会是个更大的问题……

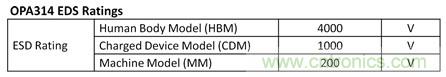

我们已经把芯片级的ESD性能写入数据手册多年,但这些参数仅适用于在芯片焊接到电路板前。那么在电路板上的ESD性能如何呢?

我们用多次电击若干个芯片的每个引脚的方法来确保其ESD性能。它模拟了在触摸和装配过程中芯片遭遇的恶劣情景。如果没有ESD保护电路,只需要低至10V的静电即可造成芯片损坏。

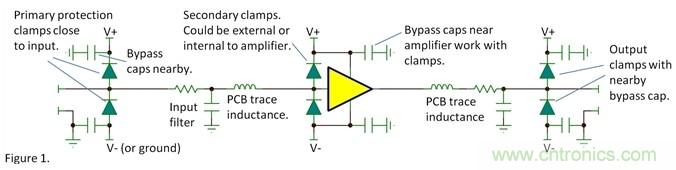

但是您也许更关心在pcb板装配后和使用时的ESD承受能力。一个芯片在安装到板子上后一般是有更好的可靠性。电源连接处有旁路电容,可以承受相当大的放电。连接到板子的输入输出一般有串联的电阻以及PCB走线的电感。到地的电容,即使是从PCB走线上的到地电容,增强了避免损害、承受静电放电的能力。

您可以使用额外的钳位二极管或者类似齐纳管的器件,它们能大大提高您整个产品或设备的ESD承受能力。Figure1展示了一个最基本的方法,更多方法请点击这里。

ESD关乎电路的生存,但您也应该考虑功能性的干扰。这也许包括需很长恢复时间的模拟电路过载。在数字电路或系统处理器中的受干扰比特会是个更大的问题。当您触摸电脑,划出一道电火花时您也许会和我一样缩手。即使此时硬件上没有受到永久的损坏,一个ESD的“打击”可以引起系统复位或者数据丢失。以确保您的系统或是产品能在不丢失数据或是重启的情况下承受此电击,懂得模拟技术的你也许是指导PCB布局、系统布局以及接地的最合适人选。

深思熟虑的规划以及实施能帮助实现好的结果。考虑在静电放电过程中电流的流向,考虑电流的两个极性来确保安全的电流路径。最好能把放电路径限制到接入点附近。在输入的地端口的放电会找到一个从容的路径到大地,而不用在板子上乱转。让电流路径远离平行线,它的电容耦合或是电感耦合都会让人不安。输入端口放电一定要找到一条电流路径到地,Figure1中的钳位二极管则提供了一条很短的路径到电源线上,然后通过旁路电容到地。

在输出端口或者其他任何可能与您的产品或者设备有导电接触点处,请考虑相同的问题。

认真的设计和PCB布局后,您可以提高系统的ESD的承受能力,包括生存和功能性的承受能力。

(来源:EDN电子技术设计,作者: Bruce Trump 资深模拟工程师)

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

基于低压差分信号的SerDes器件简化汽车音频连接

OFweek2020中国医疗科技在线论坛暨佳兆业生命健康产业推介会重磅来袭

LED显示屏控制系统是如何实现的

南京大数据产业协会加盟智能制造在线展,为您揭秘智能制造真谛

各种“地”,各种“GND”