高速数字系统的仿真设计

品慧电子讯高速数字系统设计成功的关键在于保持信号的完整,而影响信号完整性(即信号质量)的因素主要有传输线的长度、电阻匹配及电磁干扰、串扰等。

高速数字系统设计成功的关键在于保持信号的完整,而影响信号完整性(即信号质量)的因素主要有传输线的长度、电阻匹配及电磁干扰、串扰等。

设计过程中要保持信号的完整性必须借助一些仿真工具,仿真结果对 PCB 布线产生指导性意见,布线完成后再提取网络,对信号进行布线后仿真,仿真没有问题后才能送出加工。目前这样的仿真工具主要有 cadence、ICX、Hyperlynx 等。Hyperlynx 是个简单好用的工具,软件中包含两个工具 LineSim 和 BoardSim。LineSim 用在布线设计前约束布线和各层的参数、设置时钟的布线拓扑结构、选择元器件的速率、诊断信号完整性,并尽量避免电磁辐射及串扰等问题。BoardSim 用于布线以后快速地分析设计中的信号完整性、电磁兼容性和串扰问题,生成串扰强度报告,区分并解决串扰问题。作者使用 LineSim 工具,对信号的阻抗匹配、传输线的长度、串扰进行了仿真分析,并给出了指导性结论。

阻抗匹配

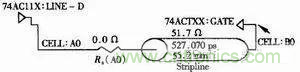

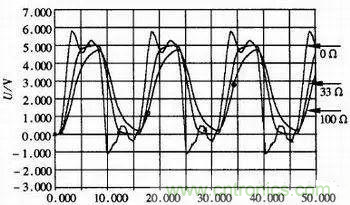

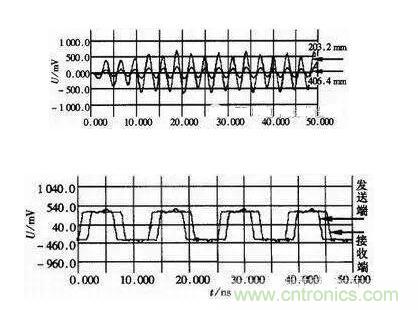

高速数字信号的阻抗匹配非常关键,如果匹配不好,信号会产生较大的上冲和下冲现象,如果幅度超过了数字信号的阈值,就会产生误码。阻抗匹配有串行端接和并行端接两种,由于串行端接功耗低并且端接方便,实际工作中一般采用串行端接。以下利用 Hyperlynx 仿真工具对端接电阻的影响进行了分析。以 74 系列建立仿真 IBIS 模型如图 1 所示。仿真时选择一个发送端一个接收端,传输线为带状线,设置线宽 0.2mm 和介电常数为 4.5(常用的 FR4 材料),使传输线的阻抗为 51.7Ω。设置信号频率为 50MHz 的方波,串行端接电阻 Rs 分别取 0Ω、33Ω和 100Ω的情况,进行仿真分析,仿真结果如图 2 所示。

图中分别标出了匹配电阻是 0Ω、33Ω、100Ω时接收端的信号波形。从波形看出,0Ω时波形有很大的上冲和下冲现象,信号最差;100Ω时信号衰减较大,方波几乎变成了正弦波;而匹配电阻是 33Ω时波形较好。理想的匹配电阻值,可以利用软件的 terminatorWizard 工具,自动根据器件的参数模型算出最佳匹配电阻为 33.6Ω,实际应用中可以选用 33Ω。利用仿真和器件的 IBIS 模型,可以很精确地知道匹配电阻值的大小,从而使信号完整性具有可控性。

图 1 74 系列仿真模型

图 2 不同串行端接电阻的仿真结果

传输线长度的影响

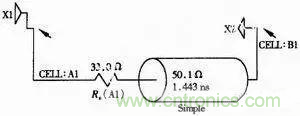

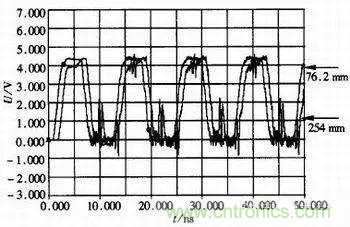

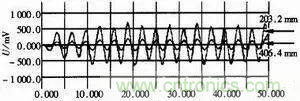

在高速数字电路的设计中,除了阻抗匹配外,部分器件对传输线的长度有着严格的要求,信号频率越高,要求传输线的长度越短。以 X1 器件和 X2 器件为例建立仿真模型如图 3 所示。在仿真模型中加了 33Ω的匹配电阻,选择仿真信号频率为 66MHz 方波,改变传输线长度分别为 76.2mm 和 254mm 时进行仿真。仿真结果如图 4 所示。

图 3 X1、X2 器件仿真模型

图 4 不同长度传输线仿真结果

从图中看出,信号线加长后,由于传输线的等效电阻、电感和电容增大,传输线效应明显加强,波形出现振荡现象。因此在高频 PCB 布线时除了要接匹配电阻外,还应尽量缩短传输线的长度,保持信号完整性。

在实际的 PCB 布线时,如果由于产品结构的需要,不能缩短信号线长度时,应采用差分信号传输。差分信号有很强的抗共模干扰能力,能大大延长传输距离。差分信号有很多种,如 ECL、PECL、LVDS 等,表 1 列出 LVDS 相对于 ECL、PECL 系统的主要特点。LVDS 的恒流源模式低摆幅输出使得 LVDS 能高速驱动,对于点到的连接,传输速率可达 800Mbps,同时 LVDS 低噪声、低功耗,连接方便,实际中使用较多。LVDS 的驱动器由一个通常为 3.5mA 的恒流源驱动对差分信号线组成。接收端有一个高的直流输入阻抗,几科全部的驱动电流流经 10Ω的终端电阻,在接收器输入端产生约 350mV 电压。当驱动状态反转时,流经电阻的电流方向改变,此时在接收端产生有效的逻辑状态。图 5 是利用 LVDS 芯片 DS90LV031、DS90LV032 把信号转换成差分信号,进行长距离传输的波形图。在仿真时设置仿真频率为 66MHz 理想方波,传输距离为 508mm,差分对终端接 100Ω负载匹配传输线的差分阻抗。从仿真结果看,LVDS 接收端的波形除了有延迟外,波形保持完好。

表 1 LVDS、ECL、PECL 逻辑标准对照表

图 5 LVDS 电路仿真结果

串扰分析

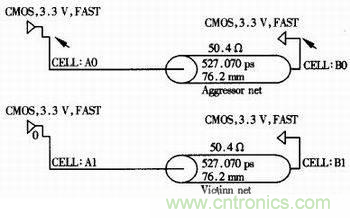

由于频率的提高,传输线之间的串扰明显增大,对信号完整性也有很大的影响,可以通过仿真来预测、模拟,并采取措施加以改善。以 CMOS 信号为例建立仿真模型,如图 6 所示。在仿真时设置干扰信号的频率为 66MHz 的方波,被干扰者设置为零电平输入,通过调整两根线的间距和两线之间平行走线的长度来观察被干扰者接收端的波形。仿真结果如图 7,分别为间距是 203.2mm、406。4mm 时的波形。

图 6 串扰模型

图 7 不同间距的串扰仿真结果

从仿真结果看出,两线间距为 406.4mm 时,串扰电平为 200mV 左右,203.2mm 时为 500mV 左右。可见两线之间的间距越小串扰越大,所以在实际高速 PCB 布线时应尽量拉大传输线间距或在两线之间加地线来隔离。

结束语

在高速数字电路设计中,不用仿真而只凭传统的设计方法或经验很难预测和保证信号完整性,仿真已成为高速信号设计的必要手段,利用仿真可以预测信号的传输情况,从而提高系统的可靠性。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

开关电源纹波,抑制或减少的5种方法

影响信号完整性的7大原因,你“中枪”了哪个?

了解这3个特性,再也不担心传输线问题了!

揭露三个关键PHY性能指标,保证你的JESD204B链路质量

ADC的放大器噪声性能评估分析