如何为裸片到裸片( Die-to-die)间连接选择正确的IP?

品慧电子讯自大数据问世以来,用于超大规模数据中心、人工智能(AI)和网络应用的片上系统(SoC)设计人员正面临着不断演进的挑战。由于工作量的需求以及需要更快地移动数据,具有先进功能的此类SoC变得益发复杂,且达到了最大掩模版(reticle)尺寸。本文介绍了die-to-die连接的几种不同用例,以及在寻找用于die-to-die链接的高速PHY IP时要考虑的基本注意事项。

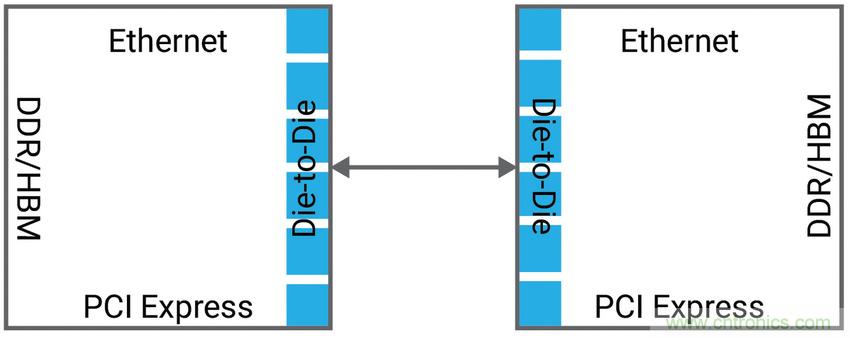

自大数据问世以来,用于超大规模数据中心、人工智能(AI)和网络应用的片上系统(SoC)设计人员正面临着不断演进的挑战。由于工作量的需求以及需要更快地移动数据,具有先进功能的此类SoC变得益发复杂,且达到了最大掩模版(reticle)尺寸。因此,设计人员将SoC划分为多芯片模块(MCM)封装的较小模块。这些分离的芯片需要超短(ultra-short)和极短(extra-short)距离链接,以实现具有高数据速率的die间连接。除带宽外,裸片到裸片(die-to-die)的连接还必须确保是极低延迟和极低功耗的可靠链接。本文介绍了die-to-die连接的几种不同用例,以及在寻找用于die-to-die链接的高速PHY IP时要考虑的基本注意事项。 Die-to-die连接用例 MCM中die-to-die连接的新用例正在出现,其中一些包括: 高性能计算和服务器SoC接近最大掩模版尺寸 以太网交换机和网络SoC超过最大掩模版尺寸 可扩展复杂算法的具有分布式SRAM的人工智能(AI)SoC 高性能计算和服务器SoC的面积正变得越来越大,达到550 mm2至800 mm2,从而降低了SoC的良率并增加了每个Die的成本。优化SoC良率的更好方法是将SoC分为两个或多个相等的同质die(如图1所示),并使用 die间PHY IP连接 die。在这种用例中,关键的要求是极低延迟和零误码率,因为更小的多个 die的表述和表现必须像单一die一样。

图1:需要die-to-die连接的高性能计算和服务器SoC示例

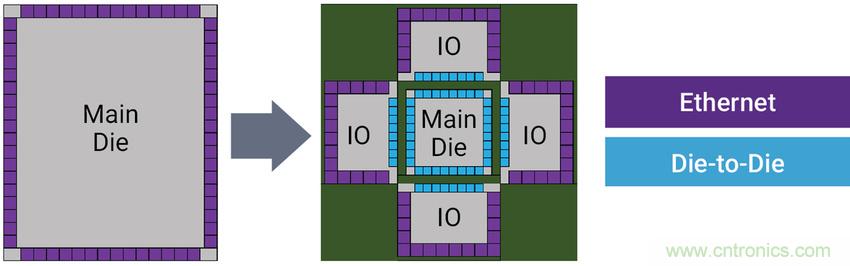

以太网交换机SoC是数据中心的核心,必须以快于12Tbps到25Tbps的速率传送数据,这需要256个通道的100G SerDes接口,因此无法将这种SoC装入800 mm2大小的掩模版。为克服这一挑战,设计人员将SoC拆分为这样一种配置:其中,内核die被I/O die包围,如图2所示。然后,使用Die-to-die收发器将内核die连接到I/O die。

在这种用例中,仅当die-to-die收发器的带宽密度远优于I/O die中的长距离SerDes时, die拆分才有效用。因此,关键参数是每毫米的die边缘(die-edge)带宽密度。

图2:需要die-to-die连接的以太网交换机SoC示例

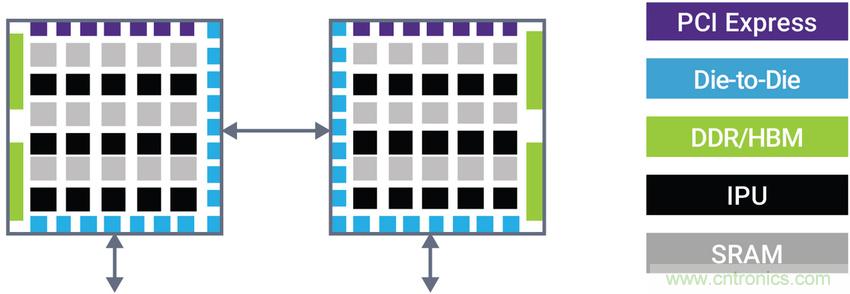

在一款AI SoC中,每个die都包含智能处理单元(IPU)和位于每个IPU附近的分布式SRAM。在这种用例下,一个die中的IPU可能需要依赖于极低延迟的短距离die-to-die链接来访问另一die中SRAM内的数据。

图3:需要die-to-die连接的AI SoC示例

在所有这些用例中,用于die-to-die连接的理想高速PHY可以简化MCM封装要求。由于每个通道的吞吐量高达112 Gbps,因此在通道数量相对有限的情况下可实现非常高的总吞吐量。在这种情况下,封装走线间距和堆叠可能比较保守(L /S通常为10u /10u)。在这些用例中,也可以使用传统、低成本、基于有机基材料的封装。

Die-to-die连接的高速PHY IP要求

光互联论坛(OIF)正在定义电气I/O标准,以在超短距离(USR)和极短距离(XSR)链路上以高达112Gbps的数据速率传输数据。这些规范定义了die-to-die的链接(即:封装内)以及die-to-die到与该SoC位于同一封装内的光学引擎的链接,从而显着降低了功耗和复杂性,并实现了极高的吞吐量密度。

在研究用于MCM中的die-to-die连接的高速PHY IP方案时,SoC设计人员必须考虑几个基本功能,包括:以千兆位或兆兆位每秒(Gbps或Tbps)度量的数据吞吐量或带宽;以每比特皮焦耳(pJ/bit)为单位检视的能源效率;以纳秒(ns)为单位测量的延迟;以毫米(mm)为单位表度的最远链接距离;以及误码率(无单位)。

数据吞吐量或带宽

为了实现与其它收发器的互操作性, die-to-die PHY IP必须确保符合USR和XSR链路的相关OIF电气规范。支持脉冲幅度调制(PAM-4)和不归零(NRZ)信令对于满足两种链路的要求并实现每通道最大112Gbps带宽至关重要。这种信令支持非常高的带宽效率,因为在MCM中的die之间传输的数据量非常大,因此带宽效率是至关重要的要求。数据移动速率通常在每秒兆兆位水平,这就限制了分配给USR和XSR链路的芯片边缘(前端/ beach front)的大小。

但是,同样重要的是支持多种数据速率。通常,期望在假设其数据速率与内部建构数据速率相匹适或支持chip-tp-chip协议所需的所有数据速率的条件下,实现die-to-die的链接。例如,即使在诸如32Gbps这样的高速下,PCI Express也必须支持低至2.5Gbps的数据速率以进行协议初始化。

链接距离

在die-to-die的实现中,大量数据必须流经桥接die间间隙的短数据路径。为保证将die放置在封装基板上时的最大灵活性,PHY IP必须支持TX和RX之间50mm的最长距离。

能效

能效成为重要的因素,尤其是在将SoC功能划分为多个同质die的用例中。在这种情况下,设计人员寻求在不影响SoC总功耗预算的情况下在die之间推送大量数据的方法。理想的die-to-die PHY IP的能效应好于每比特1皮焦耳(1pJ/bit)或等效的1mW/Gbps。

延迟和误码率

为了使die之间的连接“透明”,延迟必须极其低,同时必须优化误码率(BER)。由于采用了简化的架构, die-to-die PHY IP本身可实现超低延迟,而BER优于10e-15。根据链路距离,可能需采用前向纠错(FEC)机制保护互连,以实现如此低的BER。 FEC延迟会影响方案的整体延迟。

Macro 摆放

除了这些与性能相关的参数外,PHY IP还必须支持在die所有位向的放置,以实现die以及MCM的高效平面规划。宏(macro)的优化布局可实现低耦合的高效die间布线、优化的die和MCM大小、并最终提高能效。

选择die-to-die的PHY IP时,还有许多其它考虑因素,包括整合进可测试性功能,以便能够在封装之前对die进行生产测试,但前述几点是最重要的。

结论

更高的数据速率和更复杂的功能正在增加用于超大规模数据中心、AI和网络应用的SoC的大小。随着SoC尺寸接近掩模版尺寸,设计人员被迫将SoC分成较小的die,这些die封装在多芯片模块(MCM)中,以实现高良率并降低总体成本。然后,MCM中的较小die通过die-to-die互连进行链接,这些互连具有极低功耗和 而且每个die边缘都具有高带宽。在高性能计算和AI应用中,大的SoC被分为两或多个同质die;在网络应用中,I/O和互连内核被分为单独的die。这种SoC中, die-to-die的互连必须不影响整体系统性能,并且要求低延迟、低功耗和高吞吐量。这些要求推动了对诸如Synopsys的DesignWare®USR/XSR PHY IP这样的高吞吐量die-to-die PHY的需求,该IP支持MCM设计中的die-to-die链接,每通道的数据速率高达112Gbps,且能效极高。DesignWare USR/XSR PHY IP符合用于USR和XSR链接的OIF CEI-112G和CEI-56G标准。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

单片机与晶振究竟有什么关系?

如何选择合适的电路保护装置?

如何提高 48V 配电性能?

如何轻松稳定带感性开环输出阻抗的运算放大器?

线上时代来临,医疗从业者如何走过最艰难时间点