降低ADC信噪比损失的设计技巧

品慧电子讯在使用模数转换器(ADC)进行设计时,人们很容易错误地认为,缩小输入信号以满足ADC的满量程范围,会造成信噪比(SNR)的明显降低。

需要处理宽电压摆幅的系统设计人员对此更是尤为关注。此外,与较高电压供电的ADC相比,低压供电(5V或更低)的ADC更是种类繁多。

较高电压供电通常会导致更大的功耗和更复杂的电路板布局(例如,需要更多的去耦电容)。

本文将讨论影响SNR损失(由信号缩放引入)的主要因素,如何对其进行定量分析,以及更重要的是:如何把这种影响降至最低。

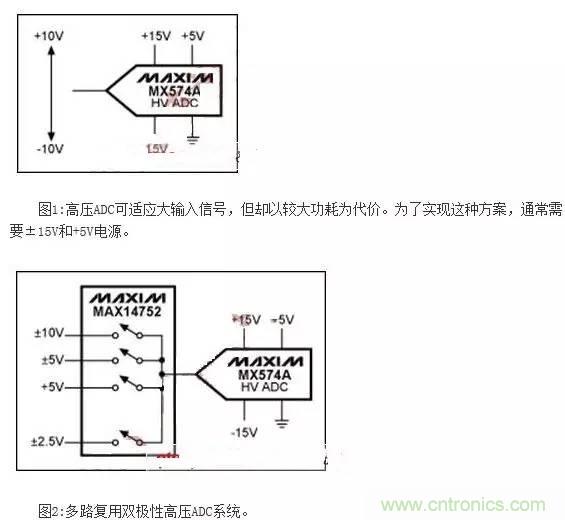

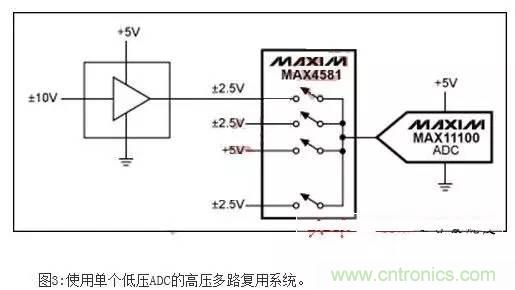

传感器或系统产生的许多信号都是双极性高压信号(如广泛使用的±10V信号)。不过,有很多简单的方法可以使这种信号通过ADC;也可以采用各种集成高压ADC解决方案:可处理这种满量程的大输入信号,而又不牺牲SNR。这些解决方案需要极高的供电电压来满足输入范围的要求,并且其功耗也相当大(图1)。这些高压ADC还缩小了信号调理(运放)解决方案的选择范围。如果信号需要与高压和低压输入组合多路复用,系统成本会大幅提升(图2)。

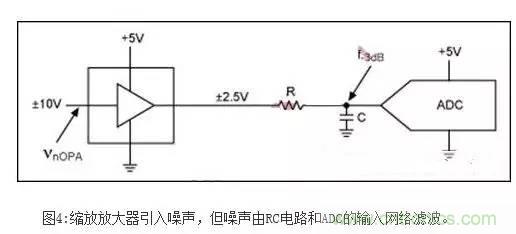

还可以使用输入放大器对信号进行缩放,使其与低压ADC的满量程输入范围相符合。这种信号调理电路可以连接到一个多路复用输入,从而使所有的信号都能与ADC的范围相符合(图3)。

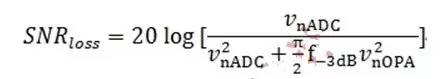

当使用放大器进行信号电压缩放时,噪声以放大器输入为参考。此时,有两个主要的噪声源:放大器本身的输入参考噪声,以及ADC的缩小输入参考噪声。这两个噪声源按照二次项的方式组合。此外,放大器的噪声还会通过ADC的输入带宽以及放大器与ADC输入之间的抗混叠滤波器进行滤波,参见图4.

图4:缩放放大器引入噪声,但噪声由RC电路和ADC的输入网络滤波。

系统SNR(放大器输入端)的计算公式为:

式中:VnADC为ADC的输入RMS噪声;VnOPA为放大器的输入参考噪声(输入参考的X倍)=单极点-3dB频率。

给定ADC的满量程范围、ADC的输入参考噪声和放大器的比例因子后,有两个变量会影响到SNR损失降低的目标:滤波器的截止频率和放大器的输入参考噪声。

如果信号源具有低频分量,可以设计滤波器,使放大器能够容许较大的输入噪声(较高的输入噪声通常与较低的功耗和成本有关)。如果ADC限制了系统的带宽,放大器需要具有足够低的输入参考噪声,以便把SNR损失控制在可接受的范围内。

举例来说,给定一个±10V输入信号和一个SNR为92dB的5VP-P满量程范围ADC,则比例因子(输入与满量程范围之比)为4.数据表中的ADC输入参考噪声为44.4nV RMS .假设滤波器的截止频率为10kHz,放大器的输入参考噪声为10nV/ (Hz) 1/2,则SNR的损失为:SNR(loss)=0.035dB.

如果没有滤波器,并假定ADC带宽为10MHz,为了达到相同的SNR损失,所需的输入参考噪声则变为0.3nV/(Hz) 1/2,这一要求非常严格。

对于10MHz相同带宽的ADC,如果允许SNR(loss)=0.5dB,则对放大器的噪声要求为4nV/(Hz) 1/2,相对来说较容易实现。

因此,如果给定了系统带宽和可容许的SNR损失,增加比例放大器以使高压信号转换到满量程范围的低压ADC,将是完全可行的解决方案。当把多路不同摆幅的信号馈送到一个多路复用的低压ADC时,这种解决方案能够实现高性价比的系统。

推荐阅读:

老工程师多年经验总结,开关电源传导EMI太重要了!

0.5% 高精度充电IC及相关方案

从容解决设计难题,应对电源排序挑战

汇集电子信息产业发展热点,第94届中国电子展盛大开幕

如何产生低噪声电压?这篇文章告诉你~