为何射频电容电感值是pF和nH级的?

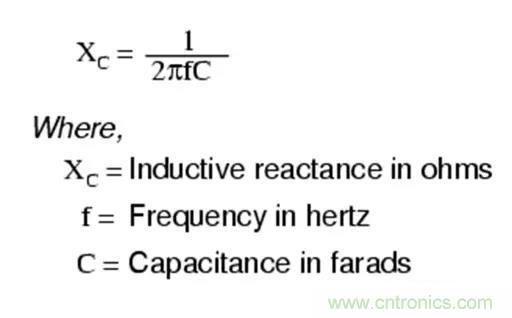

频率为0 就是开路所以只要串电容不管电容值为何就是可以挡DC,再来由上述公式也知电容值越大其容抗越小亦即Loss 越小,同时也得知电容值越大对RF 讯号而言会越接近0 奥姆电阻。

1. 在射频电路中串100pF相当于直连,这是为何?

依照下述容抗公式

频率为0 就是开路所以只要串电容不管电容值为何就是可以挡DC,再来由上述公式也知电容值越大其容抗越小亦即Loss 越小,同时也得知电容值越大对RF 讯号而言会越接近0 奥姆电阻。

而0 奥姆理论上对于RF 阻抗是不会有任何改变,所以得到一个结论,理论上串一个大电容不但可以当DC Block 同时也不会影响RF 的阻抗。

2.为什么都是pF 级别的呢,按理说nF 级别的电容容抗更小啊,为什么不用呢?

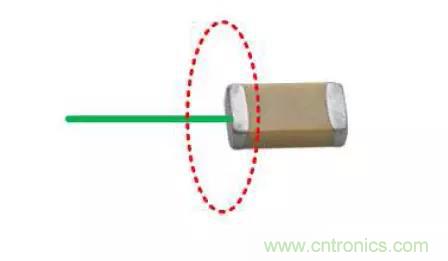

RF 走线跟电容的接合处是一个阻抗不连续面如下图:

一般而言电容值越大其Size 也会越大其接合处阻抗偏移程度也会越严重,这就失去了上述『同时也不会影响RF 的阻抗』的作用。

换言之你串一个大Size 的电容尽管其电容值很大容抗很小,但很可能其阻抗偏移造成的Loss 还更大。

既然100 pF 就能做到的事何必硬要用个3.9 nF 来徒增麻烦???看Loss 不是只看Insertion Loss 还要考虑Mismatch Loss。

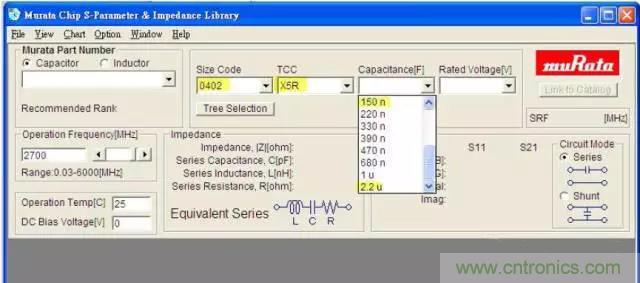

3. 那假设同样都是0402 的尺寸好了为啥只能用pF 等级?

0402 尺寸的电容中所有材质都可到达nF 等级有些甚至可到达uF 等级

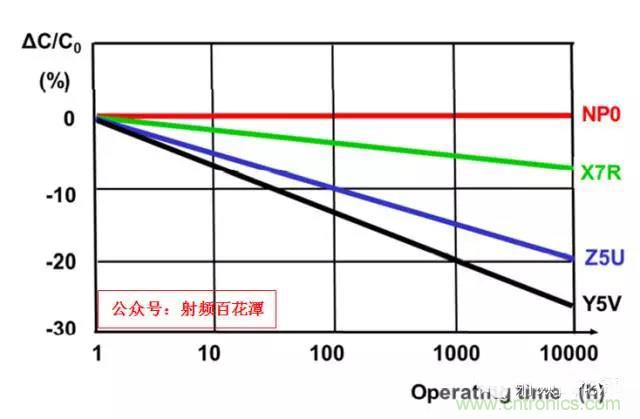

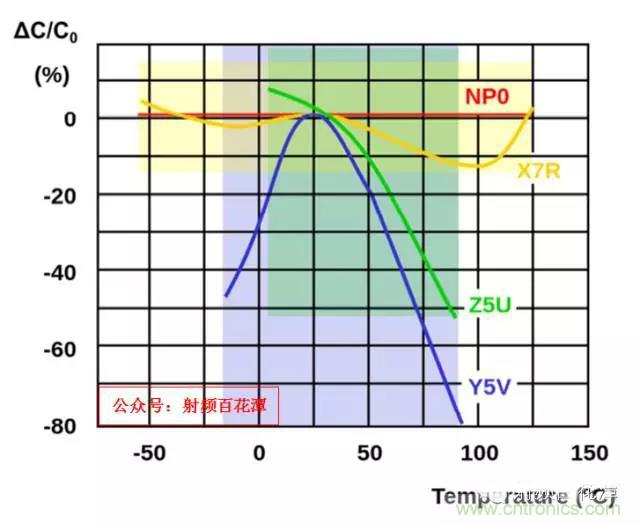

4. 但这些材质中只有C0G(或叫NP0)材质的电容其稳定度是最高的

时间稳定度:

温度稳定度:

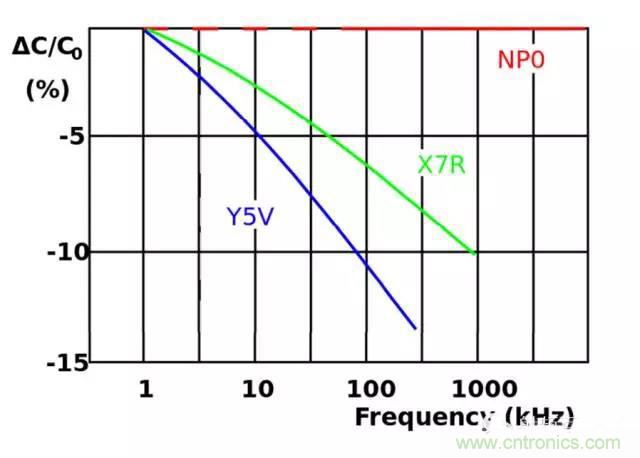

5. 频率稳定度:

6. 换言之只有C0G(NP0)材质的电容其电容值不随时间,温度, 频率而有所偏差

因此在RF 应用中只有C0G(NP0)材质的电容为首选其他都不是好选择,而C0G(NP0)材质的电容值最大也只到1nF,所以多半只能用pF 等级。

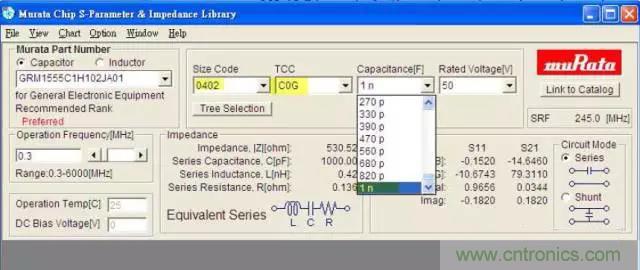

7. 假设同样都是0402 的尺寸同样都是C0G(NP0)材质

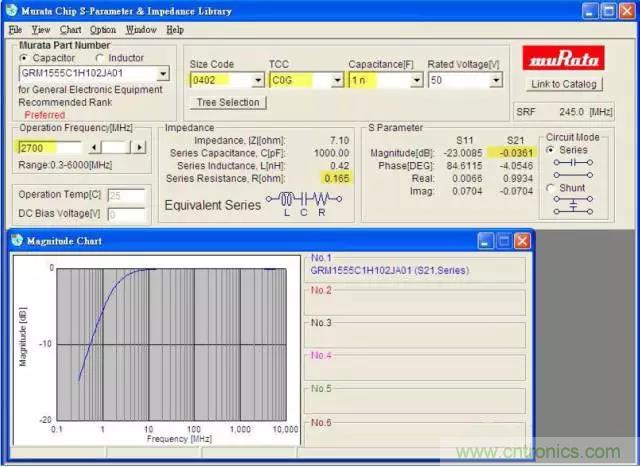

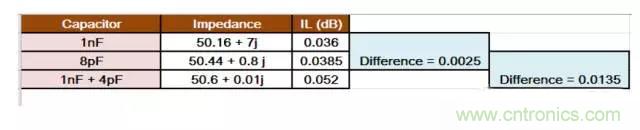

最大也还有1nF 为啥只能用pF 等级?先来比较IL (Insertion Loss) 假设RF 频率为LTE Band 7 的2700 MHz 好了。

1nF 的IL 为0.036 dB

8. 8pF 的IL 为0.0385 dB

IL 方面确实8pF 比较大因为电容值越小其ESR 越大当然IL 就越大,所以1nF 跟8pF 之所以IL 有差主要是来自于ESR 的差异。但话说回来一个0.036 dB 一个0.0385 dB,其实也没啥太大差别不需要计较到0.0025 dB 的差异。

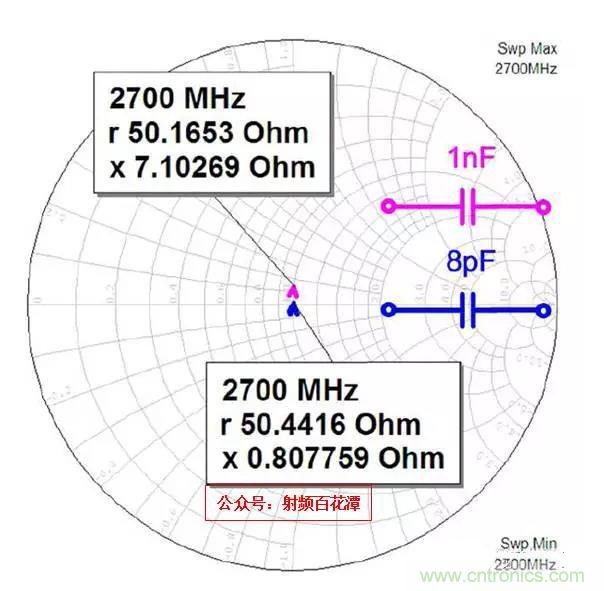

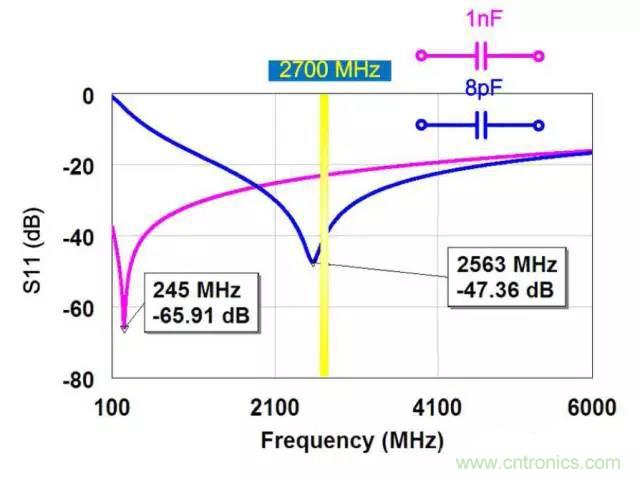

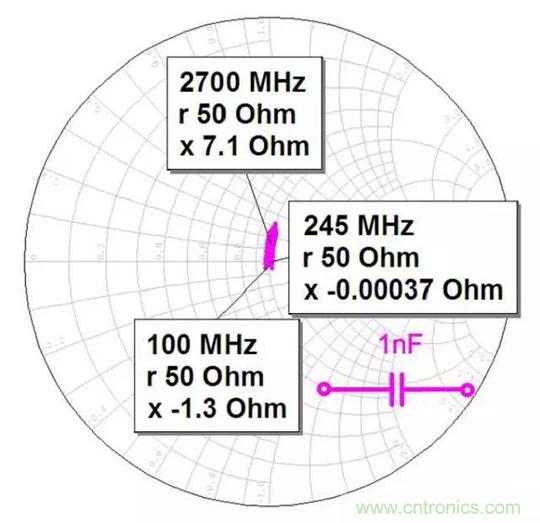

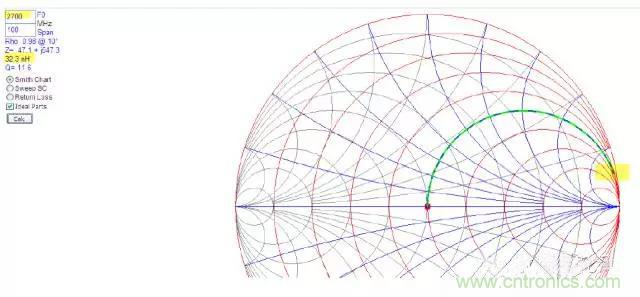

9. 但阻抗偏移程度就有差别了假设原始阻抗为50 奥姆如下图:

由上图可知1nF 的阻抗偏移程度比8pF 来得大,这就失去了DC Block『同时也不会影响RF 的阻抗』的作用。

换言之如果RF 走线阻抗控制得好走线够短够宽,原则上用8pF 当DC Block 其阻抗依旧为50 奥姆,不用再额外调匹配使其整体阻抗恢复到50 奥姆。但若用1nF 当DC Block 其阻抗会偏离50 奥姆,需要额外再调匹配使其整体阻抗恢复到50 奥姆。

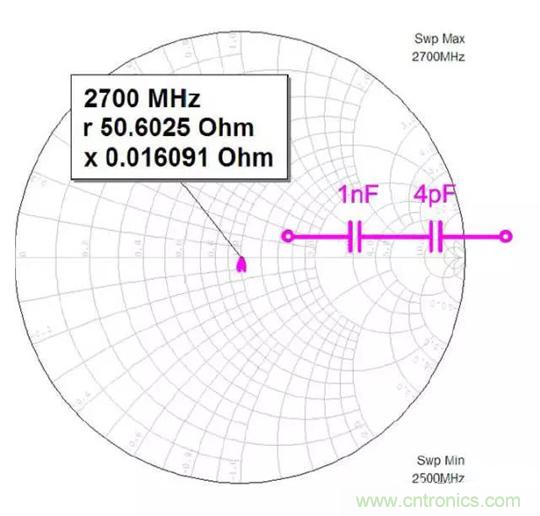

10. 因此若用1nF 当DC Block 还需再串联一个4pF 的电容

方可使整体阻抗恢复到50 奥姆

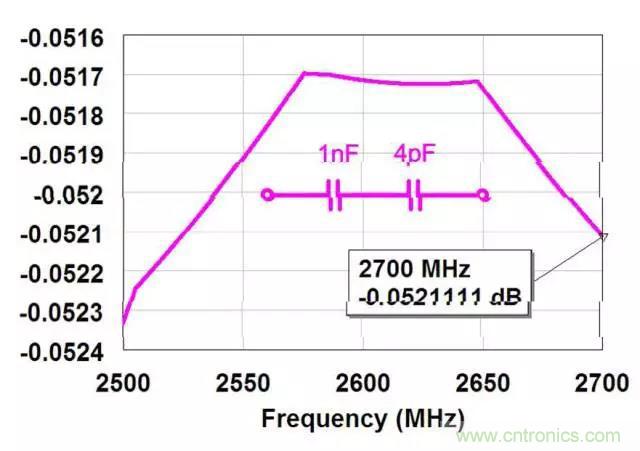

11. 再来看一下多串了4pF 电容后的IL

12. 因此整理如下:

这表示说你为了要节省那0.0025 dB 的IL,舍弃8pF 而采用1nF 的DC Block,结果需要额外再加4pF 的电容来恢复50 奥姆阻抗。

换言之,不但额外多出了调匹配的时间跟工作量同时也额外多出了0.0135 dB 的IL,这笔交易你觉得划算吗??

只要是串联无源组件不管是电感, 电容, 还是电阻,因为其内阻缘故就是会额外贡献IL。

因此除非必要否则串联组件能不加就不加,在此原则下相较于1nF,8pF 当然是较佳的DC Block 选择。

13. 根据第一点所述电容值越大会越接近0 奥姆其阻抗偏移程度应该更小

那理论上1nF 应该更接近0 奥姆为啥阻抗偏移程度还比8pF 大?

还有怎会是往右上跑? 那是串电感才会有的轨迹吧?

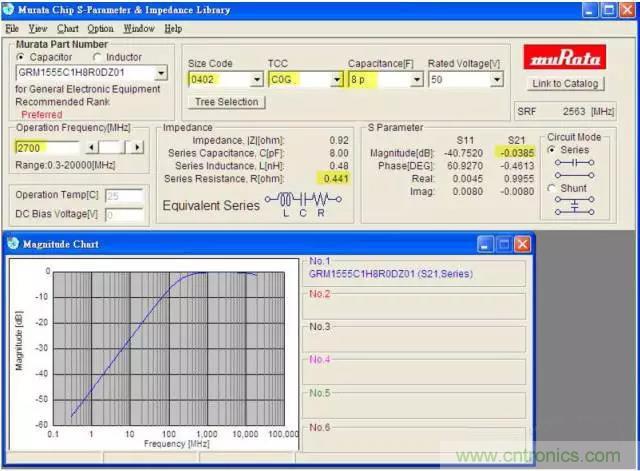

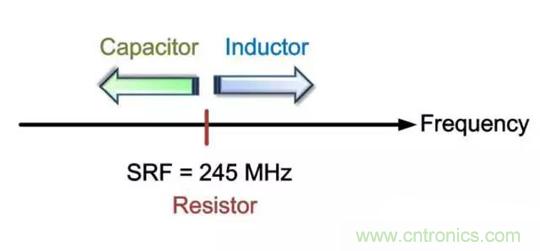

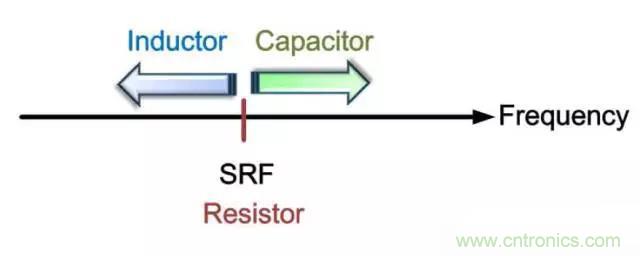

这就是重点所在了第一点讲的是理想组件的情况,但真实的电容会有SRF 其1nF 跟8pF 的SRF 如下图:

顺带一提串联的SRF 要看S11 并联的SRF 才是看S21,由上图可知8pF 的SRF 较接近RF 频率的2700 MHz 所以阻抗偏移程度较小。

反之因为1nF 的SRF 较远离RF 频率的2700 MHz 所以阻抗偏移程度较大,所以阻抗偏移程度。不是光看电容值而是要由RF 频率跟电容SRF 的差距程度来决定,因为pF 等级电容的SRF 会较接近RF 频段亦即差距程度较小。

14.所以在RF 路径上用pF 等级来当DC Block 其阻抗的偏移程度会较小

这才符合DC Block『同时也不会影响RF 阻抗』的作用,这便是为何RF 路径上其DC Block 多半为pF 等级之故,另外串1nF 电容之所以轨迹会如电感一般往右上跑原因也是SRF。

由上图可知1nF 的电容其SRF 为245 MHz 因此其行为模式如下图:

以SRF(245 MHz)为分水岭

若讯号频率座落在SRF 左边那就是电容模式其轨迹会往右下跑;

若讯号频率正好座落在SRF 那就是电阻模式其轨迹几乎不动(因为内阻很小不足以影响阻抗),若讯号频率座落在SRF 右边那就是电感模式其轨迹会往右上跑。

15. 如下图:

因此这便是为何串1nF 电容其轨迹会如电感一般往右上跑。

因为RF 频率(2700MHz)座落在SRF 右边此时是电感模式,所以仔细看串8pF 电容的轨迹其实也是微微往右上跑。

因为8pF 电容的SRF 为2563 MHz,其RF 频率会座落在其SRF 右边此时是电感模式。

同时也得知真实的电容不管值多大只有在讯号频率正好为SRF 时,才会完全等同于0 奥姆电阻,只要讯号频率不等于SRF 其行为模式就是电感模式跟电容模式两者之一。

16.因此再次验证为何RF 路径上其DC Block 多半为pF 等级

因为只有pF 等级的电容,才能使RF 频率座落在其SRF 左边这样才能呈现电容模式,而非电感模式因为这样是等同于把电容当电感用。

此时就变成了DC Blocking inductor,倒也不是说这样一定会有啥危害只是若能避免就尽量避免。

17. 为啥电感都是nH 级别的?

一般而言电感在RF 路径上的串联都是作匹配用根据感抗公式如下式:

电感值越大其感抗就越大IL 越大,因此串联电感值能小的话当然尽可能是越小越好以减少IL。

除此之外串联电感值越大其阻抗就偏移越多如下图:

换言之若会需要串联大电感来作匹配,那表示PCB 走线的原始阻抗离50 奥姆非常非常远。但基本上若有做好阻抗控制其PCB走线的原始阻抗不至于会离50 奥姆太远,如此一来在RF 路径上就更无串联大电感的需求了。何需去增大IL 呢?

18. 除此之外电感同电容一般一样有SRF 其行为模式如下:

一样以SRF 为分水岭

若讯号频率座落在SRF 左边那就是电感模式其轨迹会往右上跑;

若讯号频率正好座落在SRF 那就是电阻模式其轨迹几乎不动(因为内阻很小不足以影响阻抗);

若讯号频率座落在SRF 右边那就是电容模式其轨迹会往右下跑,所以再次验证为何RF 路径上其串联电感多半为nH 等级。

因为只有nH 等级的电感,才能使RF 频率座落在其SRF 左边这样才能呈现电感模式。

此时阻抗轨迹才好预测这样作匹配才会顺利一些,否则由于PCB 走线跟迭构的寄生效应使得在作匹配时,其阻抗轨迹已经跟仿真的预测有所误差了。

倘若组件本身的阻抗轨迹又难以预测串电感却往右下跑,这会使得网分量到的阻抗轨迹跟仿真的预测有更大误差,那倒不如盲调算了。

19. 同时又再次验证为何RF 路径上其电容多半为pF 等级

因为只有pF 等级的电容,才能使RF 频率座落在其SRF 左边呈现电容模式,这样在作匹配时其阻抗轨迹才好预测。