CMOS触发器的结构与工作原理

品慧电子讯触发器,学名双稳态多谐振荡器(Bistable Multivibrator),是一种应用在数字电路上具有记忆功能的循序逻辑组件,可记录二进位制数字信号“1”和“0”。触发器是构成时序逻辑电路以及各种复杂数字系统的基本逻辑单元。

触发器,学名双稳态多谐振荡器(Bistable Multivibrator),是一种应用在数字电路上具有记忆功能的循序逻辑组件,可记录二进位制数字信号“1”和“0”。触发器是构成时序逻辑电路以及各种复杂数字系统的基本逻辑单元。触发器的线路图由逻辑门组合而成,其结构均由SR锁存器派生而来(广义的触发器包括锁存器)。触发器可以处理输入、输出信号和时钟频率之间的相互影响。CMOS D触发器是主- 从结构形式的一种边沿触发器, CMOS T 型触发器、JK 触发器、计数单元、移位单元和各种时序电路都由其组成。TTL主从JK触发器抗干扰能力较差,而CMOS主从JK触发器抗干扰能力较好。

数字电路按照功能的不同可以分为两类:组合逻辑电路和时序逻辑电路。组合逻辑电路的特点是不具有记忆功能,它由门电路组成;时序电路的特点是具有记忆功能,触发器是它的记忆元件。按功能,触发器可以分为RS触发器、JK触发器、D触发器和T触发器。按触发方式可分为电位触发方式、主从触发方式及边沿触发方式。

触发器是一种具有记忆功能的逻辑单元电路,它能储存一位二进制码。它具有以下特点:①有两个稳定状态“0”态和“1”态;②能根据输入信号将触发器置成“0”或“1”态;③输入信号消失后,被置成的“0”或“1”态能保存下来,即具有记忆功能。

CMOS触发器的结构与工作原理

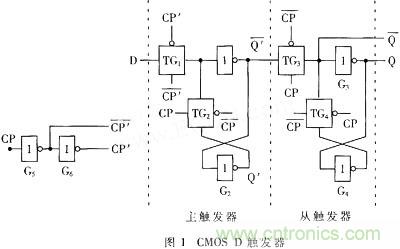

CMOS D触发器足主-从结构形式的一种边沿触发器,CMOS T型触发器、JK触发器、计数单元、移位单元和各种时序电路都由其组成,因此仪以CMOS D触发器为例进行说明。

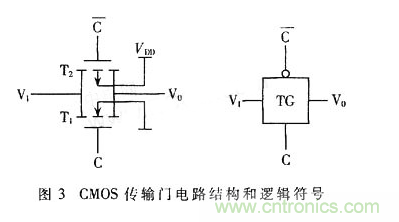

图1是用CMOS传输门和反相器构成的D触发器,反相器G1、G2和传输门TG1、TG2组成了主触发器,反相器G3、G4和传输门TG3、TG4组成了从触发器。TG1和TG3分别为主触发器和从触发器的输入控制门。反相器G5、G6对时钟输入信号CP进行反相及缓冲,其输出CP和CP′作为传输门的控制信号。根据CMOS传输门的工作原理和图中控制信号的极性标注可知,当传输门TG1、TG4导通时,TG2、TG3截止;反之,当TG1、TG4截止时,TG2、TG3导通。

当CP′=0,CP′=1时,TG1导通,TG2截止,D端输入信号送人主触发器中,使Q′=D,Q′=D,但这时主触发器尚未形成反馈连接,不能自行保持。Q′、Q′跟随D端的状态变化;同时,由于TG3截止,TG4导通,所以从触发器形成反馈连接,维持原状态不变,而且它与主触发器的联系被TG3切断。

当CP′的上升沿到达(即CP′跳变为1,CP′下降为0)时,TG1截止,TG2导通,切断了D信号的输入,由于G1的输入电容存储效应,G1输入端电压不会立即消失,于是Q′、Q′在TG1截止前的状态被保存下来;同时由于TG3导通、TG4截止,主触发器的状态通过TG3和G3送到了输出端,使Q=Q′=D(CP上升沿到达时D的状态),而Q=Q′=D。

在CP′=1,CP′=0期间,Q=Q′=D,Q=Q′=D的状态一直不会改变,直到CP′下降沿到达时(即CP′跳变为0,CP′跳变为1),TG2、TG3又截止,TG1、TG4又导通,主触发器又开始接收D端新数据,从触发器维持已转换后的状态。

可见,这种触发器的动作特点是输出端的状态转换发生在CP′的上升沿,而且触发器所保持的状态仅仅取决于CP′上升沿到达时的输入状态。正因为触发器输出端状态的转换发生在CP′的上升沿(即CP的上升沿),所以这是一个CP上升沿触发的边沿触发器,CP上升沿为有效触发沿,或称CP上升沿为有效沿(下降沿为无效沿)。若将四个传输门的控制信号CP′和CP′极性都换成相反的状态,则CP下降沿为有效沿,而上升沿为无效沿。下面以CP上升沿为有效触发沿进行分析。

推荐阅读:

硬件工程师需知的:射频模块类产品,ESD抗扰度应当如何考虑?

2020慕尼黑上海电子展:融与智——融合创新,智引未来

反防接电路设计的几种常用电路

声音传感器的原理与应用

零欧电阻的八大妙用