如何保护芯片免受静电的损害

品慧电子讯对于今天的电子产品,我们应该通过在集成电路中设计坚固的ESD结构来覆盖所有ESD基板,但大多数情况下,工程师都默认器件是安全合规的,很少考虑ESD保护。

对于今天的电子产品,我们应该通过在集成电路中设计坚固的ESD结构来覆盖所有ESD基板,但大多数情况下,工程师都默认器件是安全合规的,很少考虑ESD保护。

ESD(Electro-Static discharge)的意思是“静电释放”。ESD是20世纪中期以来形成的以研究静电的产生、危害及静电防护等的学科。因此,国际上习惯将用于静电防护的器材统称为ESD,中文名称为静电阻抗器。

静电放电或ESD的定义是在不同静电电位下的静电电荷在物体或表面之间的转移。放电会在短时间内释放超高压,在1至100纳秒(ns)的千伏(kV)范围内。可以想象,对于这些类型的电压和时间单位,ESD事件具有快速边沿。当发生这样的事件时,静电荷快速转移会造成可见或不可见的火花。

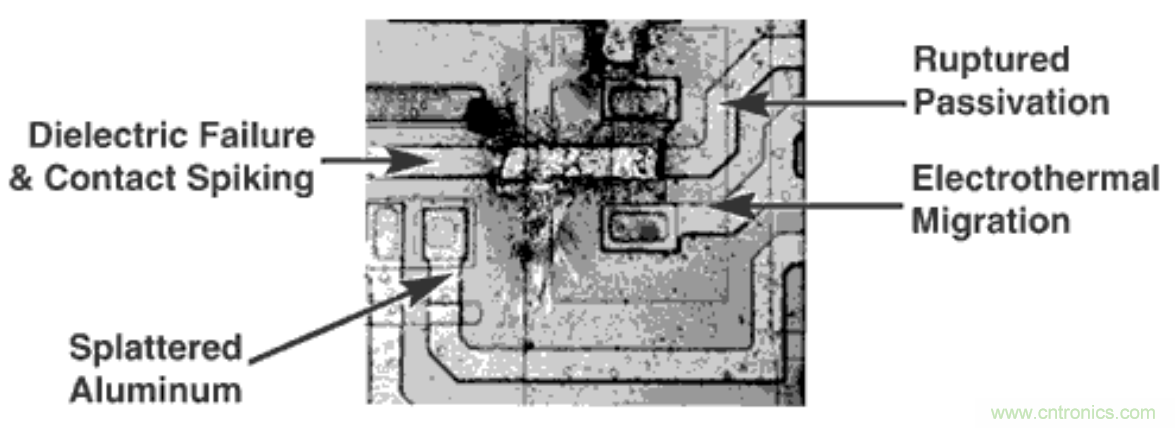

ESD通常只有敏感的电子设备才能检测到,通过触摸没有ESD保护的设备,个人很可能在不知不觉中对器件造成破坏性的损坏。在高度充电的ESD环境中,其封装内的ESD保护硅芯片将被破坏(如图1)。

图1.芯片ESD损坏的放大示例,显示金属迹线消失,钝化破裂和一种热迁移。 (:Maxim Integrated,应用笔记639)

在图1中,芯片发生ESD事件,所造成的损害是灾难性的,具有蒸发的金属痕迹,受损的钝化区域以及可能的电热迁移软错误。从技术上讲,如果电路仍然可以工作,软错误(例如规格降级)可能会在以后出现。

这种类型的损坏最容易在封装过程中或在芯片组装到PCB之前发生。IC的内部ESD保护电路在预装配处理和装配操作期间为芯片提供了一些保护。在这种环境中,低阻抗接地路径用作放电路径。在封测环境中,低阻抗接地路径的实现包括腕带,接地地板,接地桌面和ESD电离器。一旦IC安装在PCB中并与其他组件互连,这种受保护的环境就会大大降低。需要通过适当的ESD控制和预防,减少ESD损坏。

人们经常在与周围环境相互作用时产生静电火花,这些静电会破坏芯片原本的特性,此类事故每年都会造成数十亿美元的损失。在选择最终产品之前,请务必遵循实验室中的良好ESD预防措施,并查看产品数据表中的ESD保护规范。

推荐阅读:

大佬带你快速了解气体传感器

深层解析射频电路的原理及应用

MEMS传声器和驻极体电容(ECM)传声器对比

无源RC滤波器,看文了解一下

电源的回馈控制回路有什么作用?(二)