经典案例-5分钟掌握时钟EMI重点

品慧电子讯电子产品多功能化、高速化、小型化的发展,意味着对内部时钟频率的要求将越来越高。因为时钟信号是周期信号,所以在频域上的能量是集中在某个频率上的,这也就造成了时钟EMI测试超标的问题。

在此,讲述一个时钟EMI超标的重要原因:时钟信号的回流路径设计不合理。对于时钟而言,回路面积越小,辐射就越小!

1经典实验

让我们先看一个经典的实验:

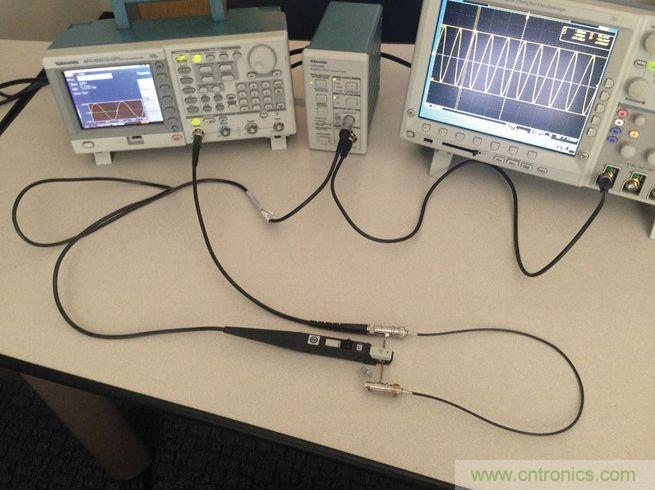

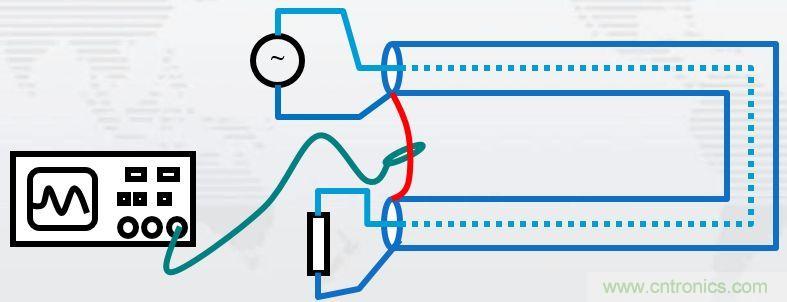

实验装置:同轴电缆的一端接信号发生器,频率可变;另一端接50Ω电阻负载。同轴电缆的两端外皮(金属编织层)用一根短粗的铜线连接起来,铜线的电阻和电感都很小。在铜线上套一个电流卡钳,用示波器监视铜线中电流的大小。

实验过程:将信号源的频率从低往高调,观察铜线中电流的变化。

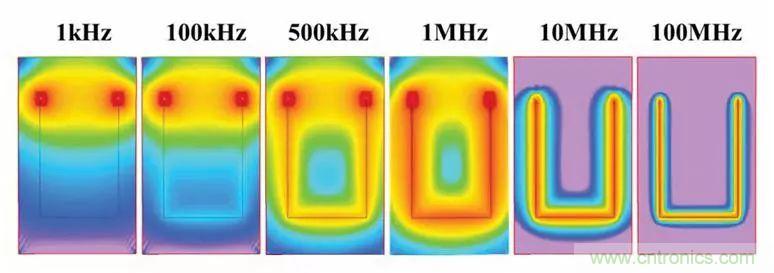

实验结果:当频率低于1kHz时,电流几乎全部走铜线,当频率高于10MHz时,电流几乎全部同轴电缆的外屏蔽层,1kHz 和10MHz 之间,两个路径都有。

实验结论:高频电流总是走电感最小的路径,也就是回路面积最小的路径。因为回路电感L = F/ I (F是磁通量,I是回路电流),而磁通量跟回路面积成正比,所以回路面积小,回路电感也就小。

2经典整改案例

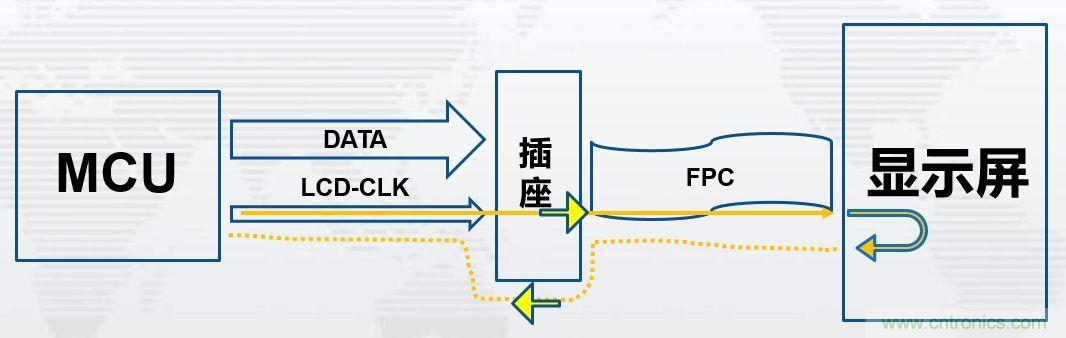

这是一个仪表盘的案例,两层板,其架构如下图,仪表盘屏时钟从MCU出来,经过PCB走线到FPC插座,然后经过FPC到屏。

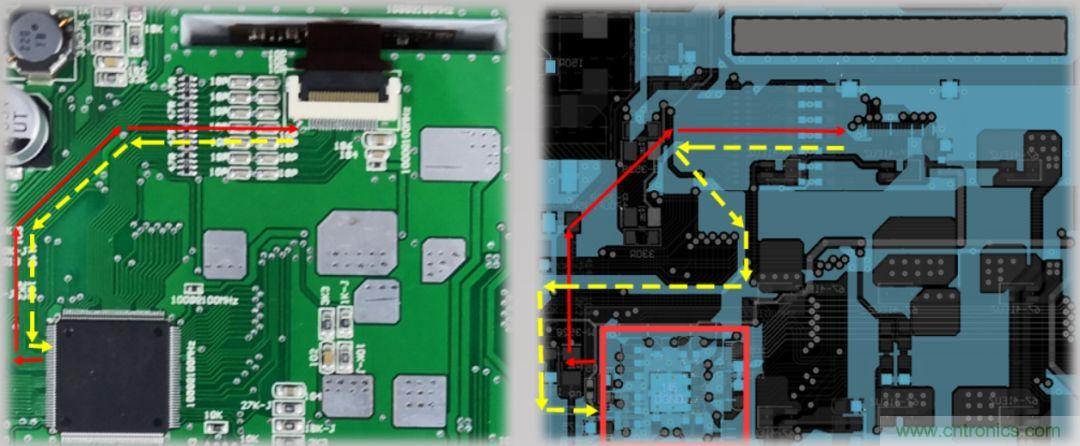

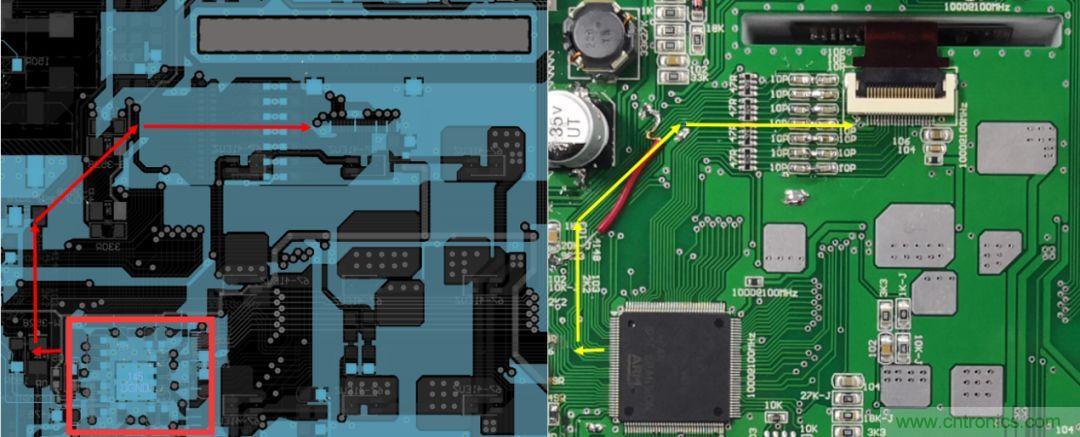

下图左边红色为屏时钟走线,理论上PCB中的时钟回流是紧贴着红色时钟走线,也就是按照黄色虚线回流,但实际上,从右边PCB图中我们可以看到,高亮部分是地,而红色时钟线附近的地并不完整,中间有一段是分割的,所以会导致时钟回流的时候寻找其他路径返回源端(黄色虚线),增大了时钟的回路面积,加强了辐射。

整改对策:用导线将分割的地连接起来,使屏时钟回流地完整。

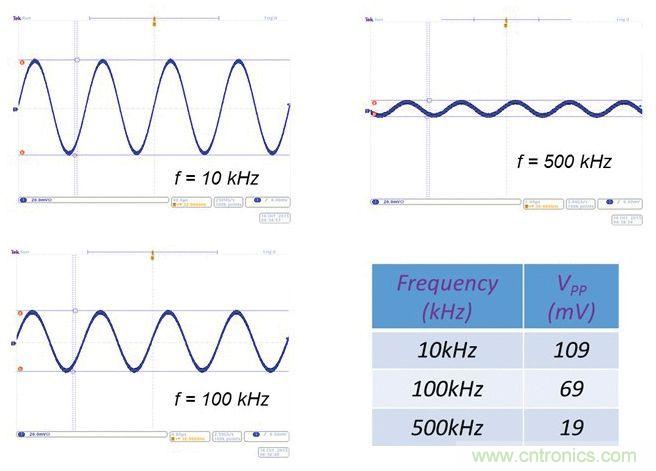

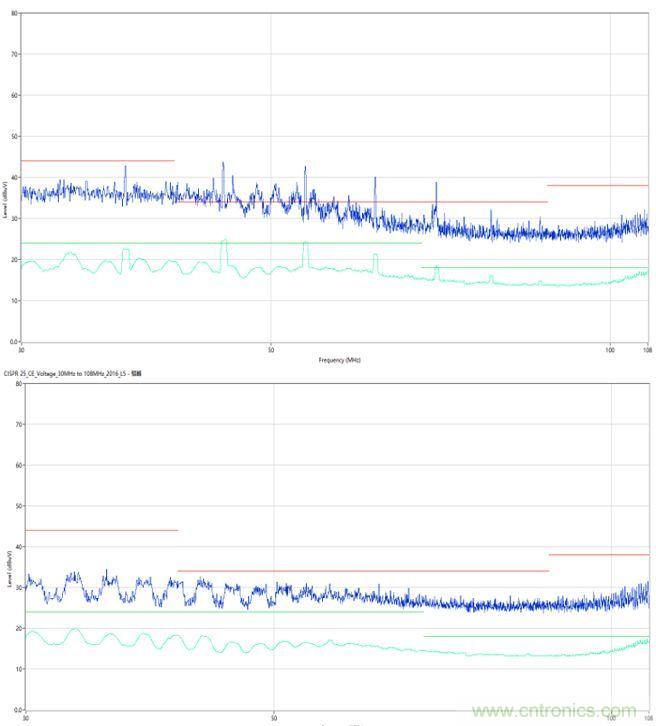

整改前后测试对比:

从测试结果可以看出来,整改只是加了一根普通的导线,但是EMI下降却非常明显,这体现了时钟回路面积的重要性。

所以,设计PCB时,一定要注意减小高频信号的回路面积!

推荐阅读:

工控自动化常用的几款保护电路盘点

一款面向24位ADC的抗混叠滤波器

CMOS多余输入端悬空造成逻辑混乱,该如何处理?

电压转换的级联和混合分不清?看几个示例就明白了

从直流到宽带,模拟信号链设计不可忽略的“共模”