MLCC解决指南:灵活使用PI模拟的技术支持

在本指南中,将介绍通过活用PI(电源完整性)模拟将2端子MLCC(积层陶瓷贴片电容)改为低ESL产品,以降低电源线路阻抗和减少去耦电容数量的技术支持。

近年来,随着各类电子系统的高功能和高性能化,IC的消耗电流量越来越大。 另一方面,IC的高功能化推动了内部结构的精细化,因此IC的耐电压下降,电源电压值下降。 看近年来的趋势,需要减少电压波动,而另一方面,IC 消耗电流变化又在增加。 因此,需要进一步降低另一个因素——阻抗。

不断提高的降低阻抗及削减去耦电容数量的要求

随着电源电压值的下降,降低电源线路的阻抗显得越来越重要。

为了抑制电压波动,需要降低阻抗。此处将介绍为了在基板尺寸以及贴装区域等受到严格限制的情况下实现所需要的阻抗特性,TDK所提出的通过替换为低ESL产品来减少去耦电容数量的方案。

低电压/大电流电源线的去耦电容

近年来,随着电子设备系统的高功能化和高速动作化,系统内部数字IC用电源线路的特性(PI:电源完整性)显得越来越重要。

提高PI的关键在于降低电源线路的阻抗,因此,在电源线路中使用了大量的MLCC作为去耦电容。

但是,随着安装小型化,对基板尺寸和贴装区域的限制越发严格,已很难为了得到期望的阻抗特性而大量贴装必要的MLCC。

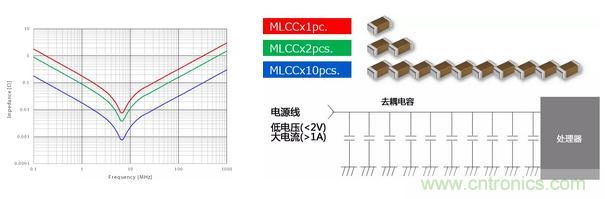

图1:不同并联贴装数量的MLCC阻抗频率特性图

通过并联多个电容可实现低阻抗

在低电压且大电流的电源回路中,

为了抑制电压波动,会使用多个去耦用MLCC

课题:数量较多 贴装面积无空余 成本增加(贴装费)

采用少量的低ESL产品,实现低阻抗

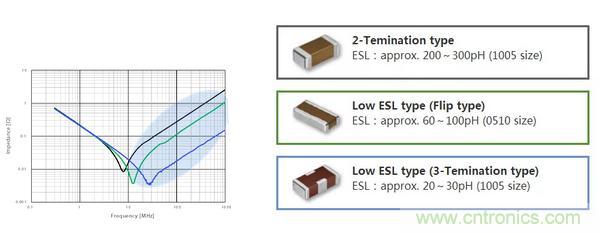

因此,TDK建议采用低ESL型电容来降低去耦电容的数量和减少贴装面积。低ESL型电容是低电感成分(ESL)的产品,在从低频到高频的宽频带实现了低阻抗。因此,大量使用通常型电容才能实现的阻抗特性,低ESL型电容只需很少的数量即可实现。

图2:典型低ESL产品的阻抗频率特性

采用少量的低ESL产品,实现低阻抗

课题:数量较多 贴装面积无空余 成本增加(贴装费)

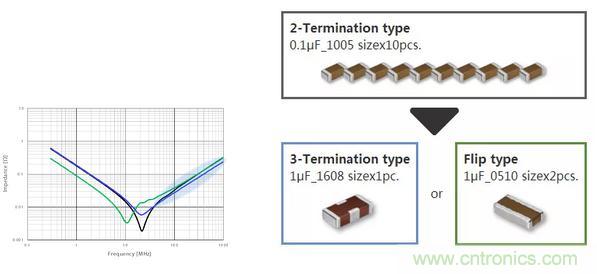

图3:通常2端子产品 10 个 vs 低ESL产品 1~2 个的阻抗频率特性

采用少量的低ESL产品,实现低阻抗

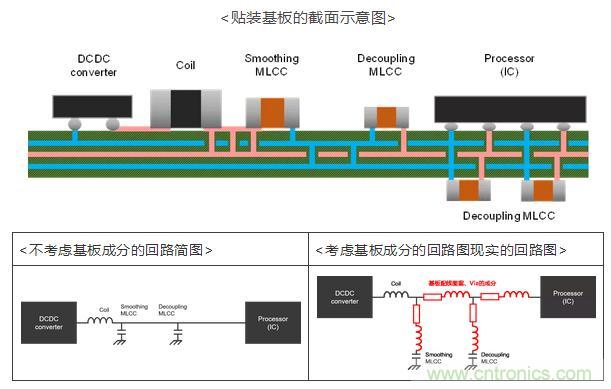

基板配线图案也是电路的一部分

除了去耦电容的最佳选定和最佳结构化之外,贴装基板的图案设计对电源线路的低阻抗化也有重要作用。贴装基板的线路用导体图案和通孔中存在电阻成分、寄生电感和杂散电容,在电源线路的阻抗设计中,基板本身的电气成分也需要作为阻抗成分的一部分在基板图案设计中加以考虑。

图4:通常DCDC转换器和IC(Processor)之间的回路示意图

TDK可实现包括基板信息在内的电源线阻抗模拟工作。

运用PI模拟的电源设计支持

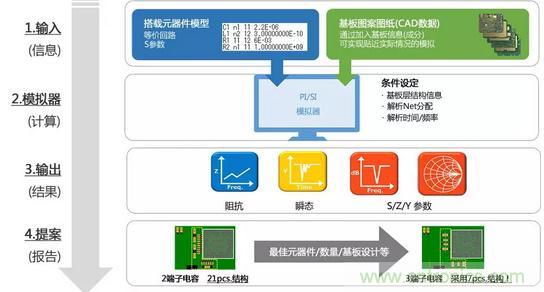

TDK通过导入贴装基板信息进行PI模拟验证,为最佳的电源线路设计提供技术支持。

根据基板类型/贴装面/IC Pin Layout/周边元器件布局等贴装基板结构,为选定最佳的电容类型、数量结构、基板线路式样、元器件排版等提供方案。

图5:执行PI模拟

课题:数量较多 贴装面积无空余 成本增加(贴装费)

一般来说,随着基板设计的深入而会出现各种制约。因此,为了给客户开发提供充分的支持,有效活用的最佳时机在基板图案设计前的初期验证阶段。

例如,在基板图案设计正式开始之前,我们也可对需要的MLCC去耦电容数量、无法将MLCC配置在IC附近时的容许距离等进行验证和提案。因此,如果您有电源线路设计方面的困扰,请尽可能在开发的前期阶段联系我们。