高精度ADC信号链中固定频率杂散问题分析及解决办法

品慧电子讯针对高分辨率、精密ADC应用中的杂散问题,本文将介绍几种判断其根本原因的方法,并提出相应的解决方案。这些技术和方法将有助于提高终端系统的EMC能力和可靠性。

简介

虽然目前的高分辨率SAR ADC和Σ-Δ ADC可提供高分辨率和低噪声,但系统设计师们可能难以实现数据手册上的额定SNR性能。而要达到最佳SFDR,也就是在系统信号链中实现无杂散的干净噪底,可能就更加困难了。杂散信号可能源于ADC周围的不合理电路,也有可能是因恶劣工作环境下出现的外部干扰而导致。

针对高分辨率、精密ADC应用中的杂散问题,本文将介绍几种判断其根本原因的方法,并提出相应的解决方案。这些技术和方法将有助于提高终端系统的EMC能力和可靠性。

本文将针对五种不同的应用情况阐述用于降低杂散的特定设计解决方案:

1.由控制器板上的DC-DC电源辐射而导致的杂散问题。

2.由AC-DC适配器噪声通过外部基准源而导致的杂散问题。

3.由模拟输入电缆而导致的杂散问题。

4.由模拟输入电缆上的耦合干扰而导致的杂散问题。

5.由室内照明设备导致的杂散问题。

杂散与SFDR

众所周知,无杂散动态范围(SFDR)表示可从大干扰信号分辨出的最小功率信号。对于目前的高分辨率、精密ADC,SFDR一般主要由基波频率与目标基波频率的第二或第三谐波之间的动态范围构成。然而,由于系统其他方面的因素,可能会导致杂散产生并限制系统的性能。

这些杂散可分为输入频率相关杂散和固定频率杂散。输入频率相关杂散与谐波或非线性特性有关。本文将重点分析由电源、外部基准源、数字连接、外部干扰等造成的固定频率杂散。根据应用情况,可降低或完全避免这些类型的杂散,以助于实现最佳的信号链性能。 由ADC周围DC-DC电源而导致的杂散问题

由于DC-DC开关稳压器会产生较高的纹波噪声,通常建议将LDO作为在精密测量系统中为精密ADC生成低噪声电源轨的解决方案。固定频率或脉宽调制开关稳压器会产生开关纹波,该纹波一般位于几万至几兆赫兹固定频率处。固定频率噪声可能会通过ADC的PSRR机制馈入ADC转换代码中。

某些设计师可能会因电路板空间有限或预算问题而在精密ADC应用中采用DC-DC开关稳压器。为了实现理想的信号链性能,他们必须限制纹波噪声或使用高PSRR ADC,以确保这些纹波噪声低于ADC噪底。否则,在ADC输出频谱的开关频率处可能会出现杂散,这有可能会使信号链的动态范围降级。

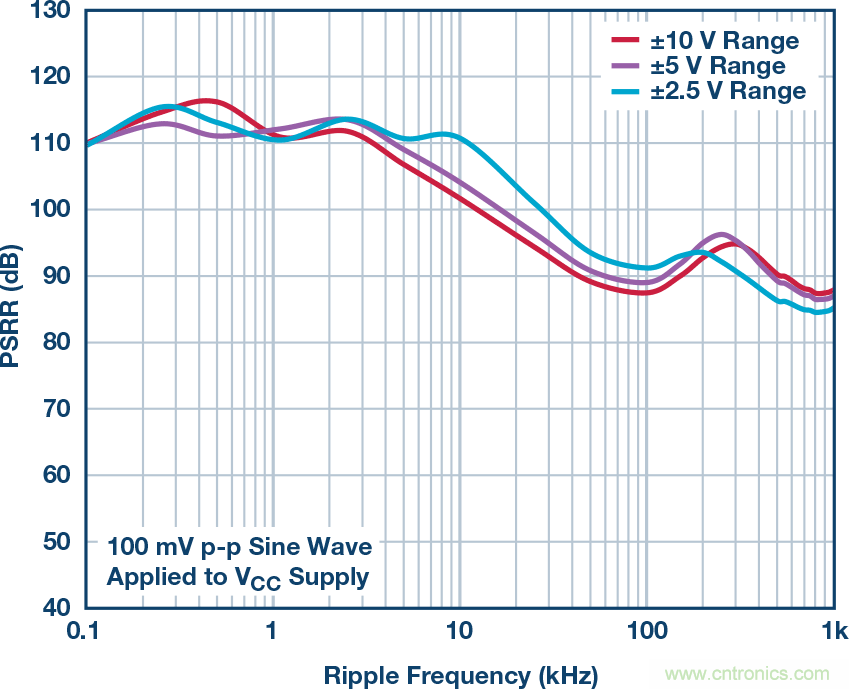

AD7616 是一款16位数据采集系统(DAS),支持在电力线监控中对16个通道进行双路同步采样。该器件具有很高的PSRR,将能有效地抑制/衰减开关纹波。例如,将一个在100 kHz处有100 mV峰峰值纹波噪声的DC-DC开关电源用于AD7616,VCC为5 V,±10 V输入范围。

则因纹波导致的数字码噪声为:

![]()

对于一个16位转换器而言,ADC输出端出现的这种纹波电平是非常低的。ADC的高PSRR性能使得设计师们也可以在精密测量系统中采用开关稳压器。

图1.AD7616 PSRR与纹波频率的关系。

因DC-DC电源辐射而导致的杂散问题

仅仅使用高PSRR ADC并不能保证开关稳压器在精密测量系统中不会造成任何问题。开关稳压器产生的纹波噪声可能会通过其他方式馈入ADC的数字码中。

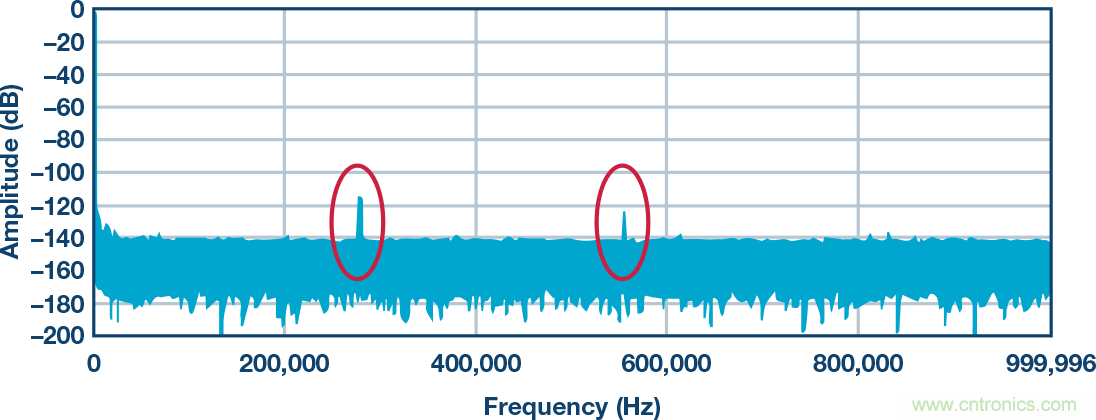

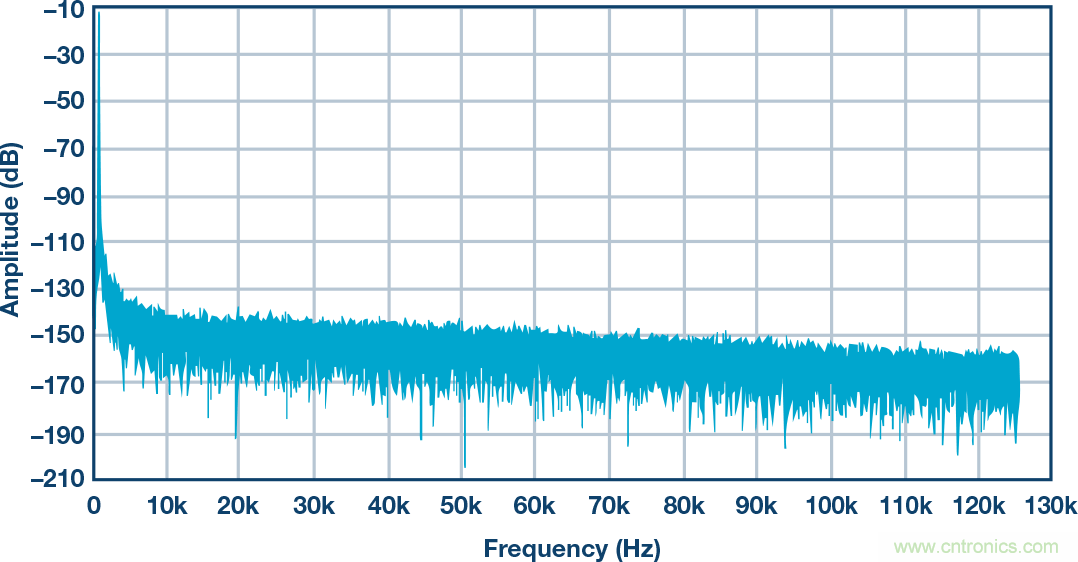

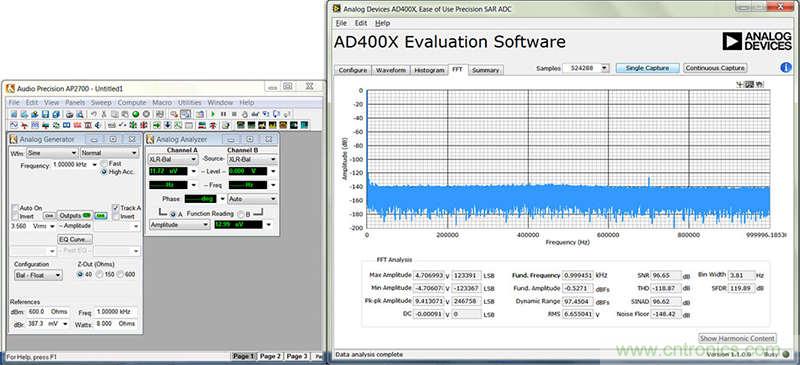

AD4003 是一款低噪声、低功耗、高速、18位、2 MSPS精密逐次逼近型寄存器(SAR) ADC。在EVAL-AD4003FMCZ评估板交流性能测试过程中,在277.5 kHz附近出现约–115 dBFS的杂散电平;该杂散及其第二谐波如图2所示。

图2.EVAL-AD4003FMCZ评估板上观察到的杂散问题。

其次,进行测试,判断杂散是否来自模拟输入端。测试结果如下:

移除差分模拟输入调理电路后,杂散降低。

在AD4003的缓冲放大器ADA4807-1前端插入一个窄带RC滤波器(如1 kΩ,10 nF)后,杂散降低。

这些结果表明,杂散导致的噪声可能会通过调理电路进入AD4003的模拟输入端。然后,断开传感器输出,移除调理电路,仅留下VREF/2 CM电压输入(在ADA4807-1的同相输入端)。但仍然存在杂散,并且具有近似的电平。

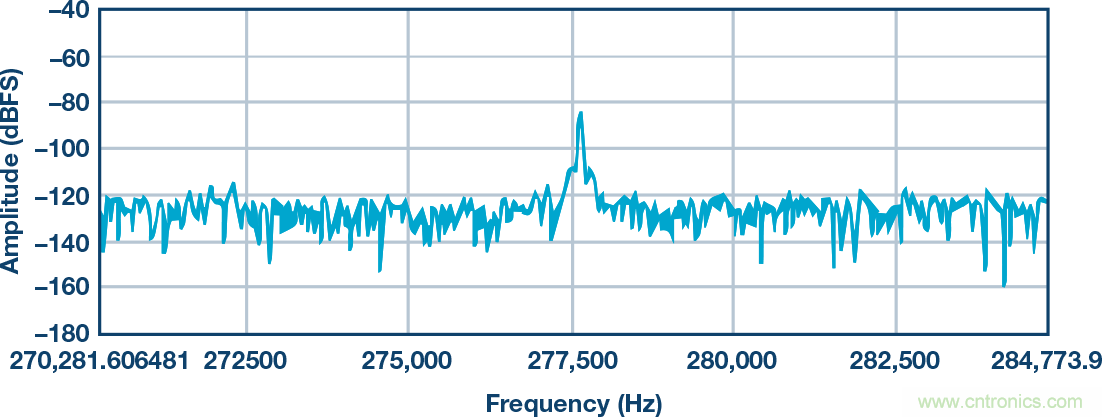

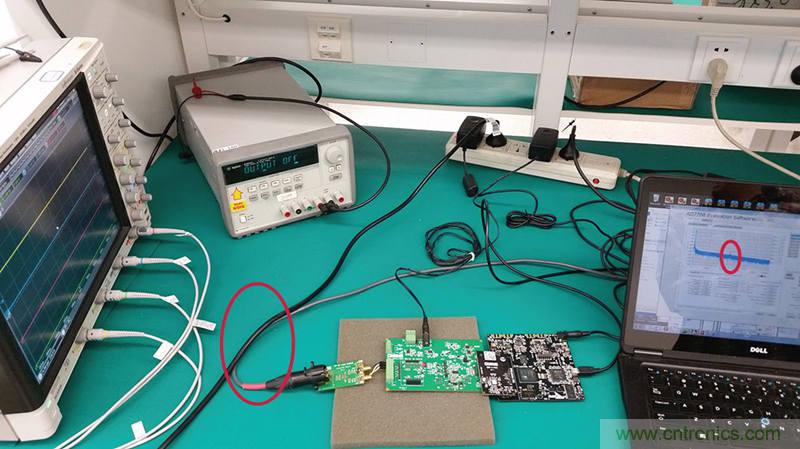

那么,怀疑干扰源有可能位于EVAL-AD4003FMCZ信号链周围。为了证明此点,在EVAL-AD4003FMCZ评估板和SDP-H1控制器板上多处放置铜箔屏蔽罩。其结果是,当铜箔屏蔽罩覆盖SDP-H1板上的DC-DC电源时,如图3所示,杂散就会消失。277.5 kHz杂散频率刚好与ADP2323 稳压器的编程开关频率相符。图4显示了EVAL-AD7616SDZ GUI FFT捕获的3.3 V VADJ_FMC开关频率功率。

图3.VADJFMC电感L5被铜箔屏蔽罩覆盖。

图4.EVAL-AD7616SDZ GUI FFT捕获的VADJFMC 3.3 V开关纹波。

得出的结论是,DC-DC开关频率干扰是由8.2 µH电感L5发出的。该干扰从缓冲放大器ADA4807-1的输入端注入信号链,然后进入AD4003 ADC的模拟输入端。

针对这种DC-DC电源转换器导致的杂散问题,可行的解决方案有:

1.在AD4003 ADC前端使用一个低通滤波器,以在应用带宽允许的情况下,将耦合的DC-DC开关频率干扰衰减到符合设计目标的程度(即杂散位于噪底以下)。

2.使用L5为屏蔽电感的新型SDP-H1板(BOM版本1.4)。辐射干扰功率降低,因此AD4003 ADC频谱中捕获的杂散功率也低得多。

3.VADJ_FMC的电压电平可通过EVAL-AD4003FMCZ评估板上的EEPROM进行编程。试验证明,使用较低的电压电平(如VADJ_FMC为2.5 V)也会使杂散消失。

由AC-DC适配器噪声耦合通过外部基准源而导致的杂散问题

ADC参考其直流基准电压电平将模拟信号量化成一个数字码。因此,直流基准电压输入上的噪声将直接馈入ADC输出的数字码。

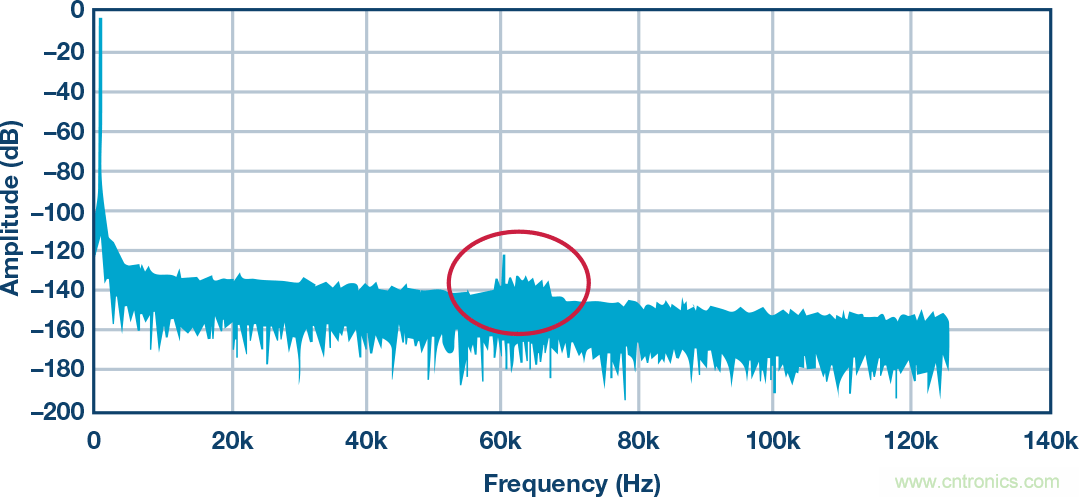

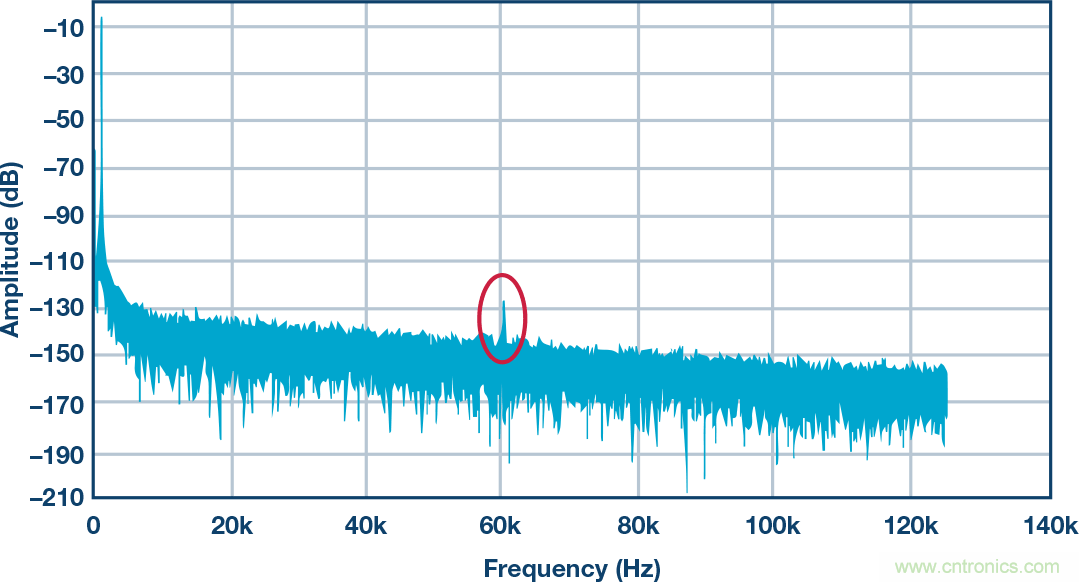

AD7175-2是一款低噪声、快速建立、多路复用、2/4通道(全差分/伪差分)Σ-Δ型ADC,可用于低带宽输入。在EVAL-AD7175SDZ评估板的信号链测试中,在60 kHz附近捕获到一簇杂散信号,如图5所示。

图5.EVAL-AD7175-2SDZ评估板上观察到的杂散问题。

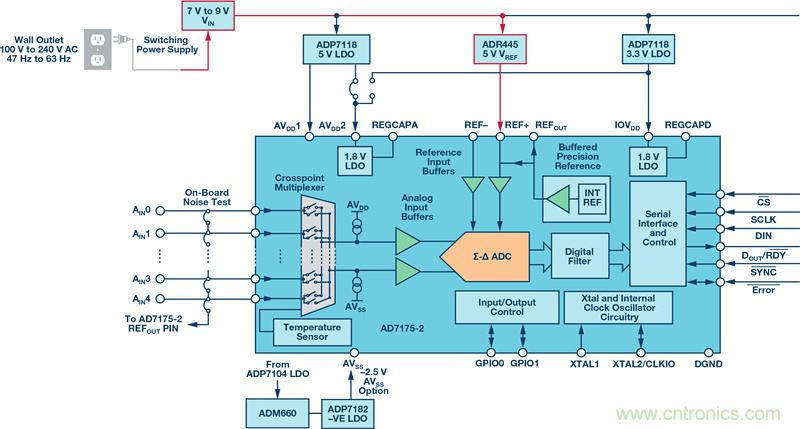

经过评估发现,AD7175-2 ADC的电源和模拟调理电路都处于良好状态。但是,如图6中所示,AD7175-2的5 V基准电压输入由ADR445基准源生成,该基准源的9 V直流电源来自评估板外部的AC-DC适配器。接下来,使用一个工作台9 V直流电源模块替换该适配器。结果杂散簇消失,仅在60 kHz处留下一个窄带杂散。

图6.EVAL-AD7175-2SDZ评估板上观察到杂散问题。

图7.EVAL-AD7175-2SDZ评估板上已消除杂散簇。

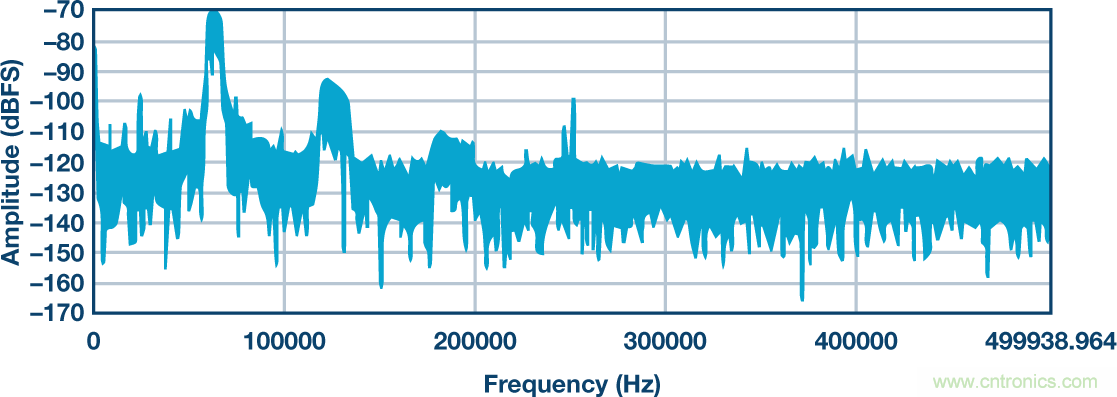

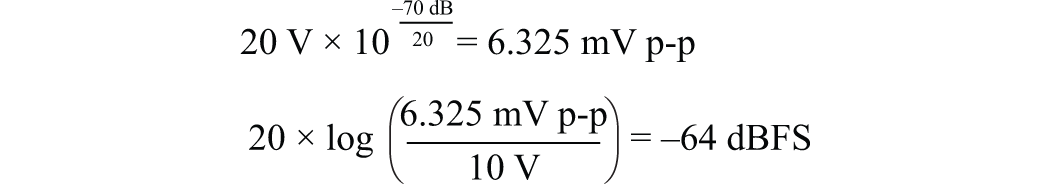

以320 mA输出电流对EVAL-AD7175-2SDZ板供电时,通过EVAL-AD7616SDZ GUI FFT对9V输出AC-DC适配器进行测试。使用AD7616 ±10 V输入范围时,ADR445 基准源电源引脚上的开关频率功率约为 –70 dBFS,这意味着使用AD7175-2 ±5 V输入范围时,产生的噪声具有6.325 mV峰峰值或为–64 dBFS。

图8.EVAL-AD7616SDZ GUI FFT捕获的3.3 V VADJFMC开关纹波。

此电源开关纹波噪声会馈入AD7175-2 ADC,并以数字码呈现,存在一定程度的衰减,如下所述:

ADR445基准源的数据手册规定60 kHz处的PSRR为49 dB。

2.ADR445基准源在60 kHz处的输出阻抗约为4.2 Ω。结合4.8 µF存储电容,可进一步造成18 dB衰减。

3.此外,当ODR为256 ksps时,AD7175-2 ADC的数字滤波器sinc5 + sinc1在60 kHz处会增加约–3 dB衰减。

![]()

计算所得的电平为–134 dBFS,十分接近图5中所捕获的–130 dBFS杂散簇电平(不包括最高的窄带杂散)。这可证实,该杂散簇是由AC-DC适配器的开关纹波馈入外部基准源ADR445造成的。剩下的窄带杂散将在下一章节中予以分析。

由注入信号链的干扰而导致的杂散问题

在硬件系统中,从输入传感器到精密转换器输入端之间往往具有很长一段信号链。该信号链包括连接电缆、连接器、路由导线、调整和调理电路、ADC驱动器等等。因此,外部干扰很有可能会注入模拟输入信号链并产生ADC杂散。 由电源电缆干扰注入信号链而导致的杂散问题

在研究EVAL-AD7175-2SDZ评估板输出频谱中剩下的窄带杂散时,注意到测试台上有一台正在工作的数字示波器。如图9所示,该示波器的220 V交流电源电缆(黑色)与EVAL-AD7175-2SDZ评估板的模拟输入电缆(灰色)有一部分重叠。将示波器关掉或将其电源电缆从模拟输入电缆上移开后,60 kHz处的窄带杂散消失,如图10所示。

在系统机柜中,对传感器至DAQ板之间的线路进行布线时应格外注意。将敏感的低电平模拟信号与大电流电力线隔离开来是一个良好的操作习惯。

图9.示波器电源电缆导致的杂散

图10.EVAL-AD7175-2SDZ评估板上已消除所有杂散。

由灯具辐射导致的杂散问题

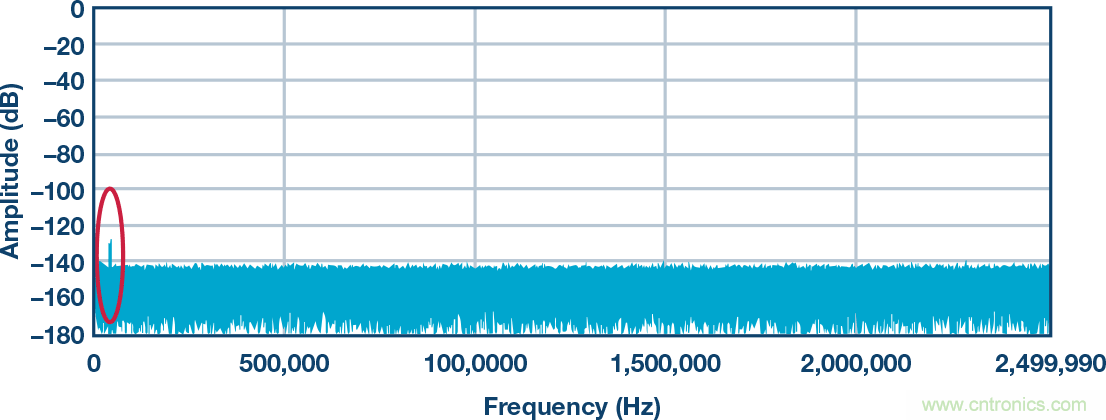

在测试EVAL-AD7960FMCZ评估板时,FFT频谱上出现一个杂散。如图11所示,该杂散的电平约–130 dB,位于40 kHz处。

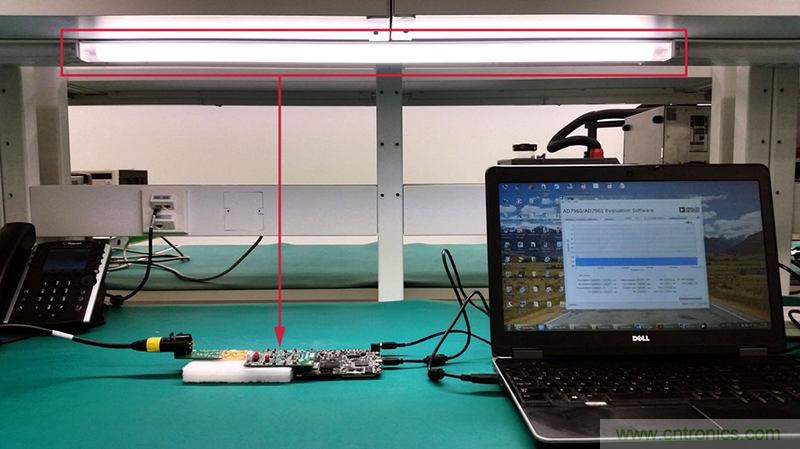

40 kHz似乎与EVAL-AD7960FMCZ评估板及其控制器板SDP-H1上的任何信号频率都不相关。找出杂散源的另一种方法是清理测试台,也许是测试台上的某些物体产生了外部干扰。当关掉台架上的日光灯后,杂散消失。此外还发现,EVAL-AD7960FMCZ评估板离日光灯越近,40 kHz处的杂散就会越高。在缓冲放大器ADA4899-1前方插入一个额外的RC滤波器(如1 kΩ,10 nF)后,杂散降低约10 dB。这意味着,日光灯辐射干扰从缓冲放大器的同相输入端前方进入到信号链路中。 对于工作在照明环境下的系统,在前端电路上安装一个屏蔽罩有助于防止辐射干扰和优化信号链性能。

对于工作在照明环境下的系统,在前端电路上安装一个屏蔽罩有助于防止辐射干扰和优化信号链性能。

图11.日光灯辐射在EVAL-AD7960FMCZ上造成的杂散

图12.靠近EVAL-AD7960FMCZ评估板的日光灯。

由较长模拟输入电缆导致的杂散问题

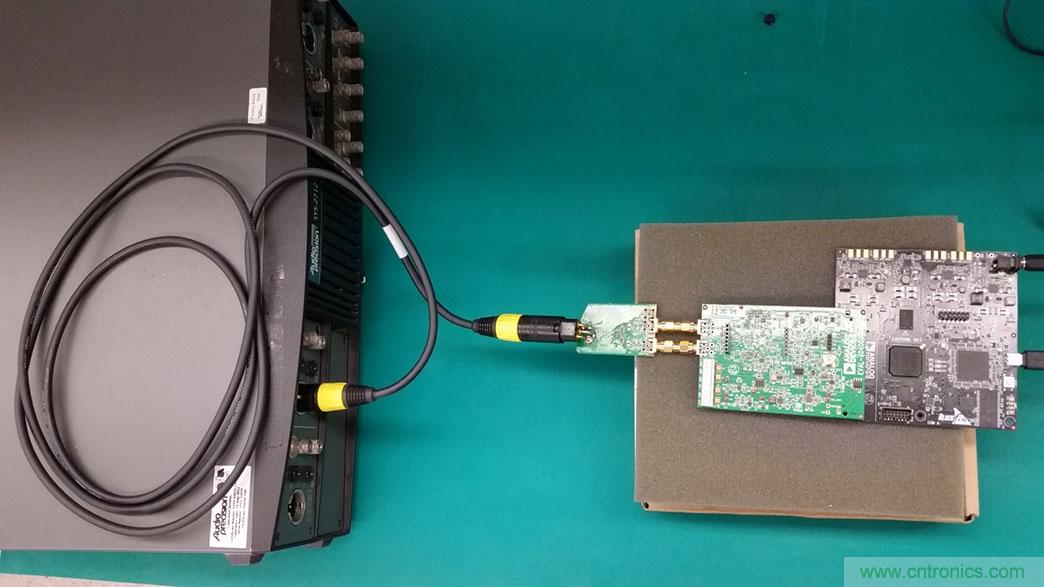

在EVAL-AD4003FMCZ评估板的工作过程中,使用的AP SY2712信号发生器通过一条XLR麦克风电缆(约2米长)驱动低噪声、低THD正弦波信号进入模拟输入端。在这种设置下,700 kHz处出现一个约–125 dB的杂散,如图13所示。

在研究该杂散的过程中,发现有三种方法可解决此问题:

不用两米长的XLR麦克风电缆,而直接将AP平衡输出的XLR插针与转接板的XLR插口短接。

将信号源SY2712的输出阻抗设置从Z-Out = 40 Ω改为Z-Out = 600 Ω。

在AD4003的缓冲放大器ADA4807-1前端向信号链中插入一个窄带RC滤波器(如1 kΩ,10 nF)后,杂散降低。

最终结论是,在700 kHz处出现的高频杂散是由于信号源输出阻抗不匹配并且XLR电缆较长所导致。

图13.XLR电缆在EVAL-AD4003FMCZ上造成的杂散

图14.AP通过较长的XLR电缆驱动EVAL-AD4003FMCZ。

结论

针对系统应用中高分辨率、精密ADC的杂散问题,本文探讨了判断其根本原因的方法。文中介绍了在五种不同应用情况下消除或降低杂散的特定设计解决方案。本文还探讨了相关的杂散计算方法,有助于评估杂散的功率水平(作为特定应用的设计目标)。

推荐阅读:

运放电路超高精度电阻使用:匹配和稳定的重要性

Massive MIMO和波束赋形:5G流行词背后的信号处理

MEMS振动监控:从加速度到速度

对电阻使用的经验法则说不

5G给RF前端产业生态带来了什么改变?