用模拟减法消除PWM DAC纹波

品慧电子讯每个PWM DAC设计都需要模拟滤波,以便将需要的直流分量(与 PWM占空比成正比)与不需要的交流纹波分开。选择足够大的RC乘积可以实现任何期望的纹波衰减,但是稳定时间会受到影响。对许多应用而言,需在电路复杂度与PWM DAC性能之间进行合理折衷。

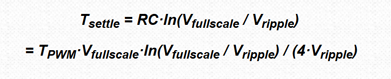

每个PWM DAC设计都需要模拟滤波,以将需要的直流分量(与PWM占空比成比例)与不需要的交流纹波分开。最简单的方法是采用基本的RC低通滤波器,它给出峰峰值纹波幅度(这是针对50%PWM占空比的最坏情况,其中TPWM=PWM周期时间,并假设RC>TPWM):

![]()

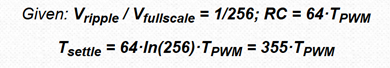

显而易见的设计取舍是:虽然选择足够大的RC乘积可以实现任何期望的纹波衰减度,但是稳定时间将相应地受到影响。例如,如果我们(相当逻辑地)选择稳定带等于纹波幅度这样一种定义,则:

这种关系的结果可以用8位的例子来说明:

这里,即使有相当快的32kHz(31µs TPWM),稳定时间仍然是相当冗长的11ms。

显然,如果稳定时间是个关键的设计参数,我们就需要做得更好,并找到一个不会过于简单的滤波方案。我以前写的一篇设计实例“快速稳定的同步PWM-DAC滤波器几乎没有纹波”说明了沿这个思路的极大可能性。

但并不是每个应用都不能容忍冗长的355TPWM稳定时间或可证明确实需要这样一种复杂的滤波方案。本设计实例解决了这些常见的应用问题。如图1所示,它通过一个反相器、R2和C2对基本的R1/C1低通滤波器进行了增强;反相器、R2和C2一道从所需的直流信号中抵冲并减去(大部分)不需要的交流分量,从而得到一个相对干净的模拟信号输出,其稳定时间比简单的RC滤波器短得多。

图1:PWM DAC纹波消除器的波形和原理图。

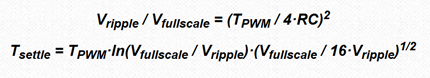

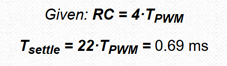

但是,“相对干净”是多干净?“快得多”又是多快?设置R2=R1和C2=C1,则新电路的纹波和稳定时间值为:

再次参考8位的例子(见图1):

采用32kHz的周期,速度提高了16倍,纹波-幅度比成倍提高!

对许多应用而言,这是在电路复杂性的适度增加和PWM DAC性能的显着提高之间非常有价值的折衷。

本文转载自电子技术设计。