关于esd保护二极管的比较

随着更新的集成电路(IC)技术采用更小的几何尺寸和更低的工作电压,不断更新换代的便携产品对静电放电(ESD)电压损害越来越敏感。有鉴于此,手机、MP3播放器和数码相机等便携产品的设计人员必须评估各种可供选择的ESD保护解决方案,确保他们所选择的解决方案能满足当今IC不断变化的需求。怎么样选择有效的ESD保护解决方案呢?

什么是ESD保护?

ESD是Electro-StaTIc discharge的缩写,即“静电释放”。本文介绍以下内容:ESD的产生的三种形式;什么是静电;静电的产生原因;什么是ESD(静电放电);ESD对电子设备的影响……

ESD是代表英文ElectroStaTIc Discharge即‘静电放电’的意思。ESD是本世纪中期以来形成的以研究静电的产生与衰减、静电放电模型、静电放电效应如电流热(火花)效应(如静电引起的着火与爆炸)及和电磁效应(如电磁干扰)等的学科。近年来随着科学技术的飞速发展、微电子技术的广泛应用及电磁环境越来越复杂,对静电放电的电磁场效应如电磁干扰(EMI)及电磁兼容性(EMC)问题越来越重视。

从近期的设计趋势的ESD所需考虑因素

ESD 保护器件的目的是把数千伏电压的ESD输入电压降低到所保护的IC所能承受的安全电压,并能把电流从IC旁路。虽然所需ESD波形的输入电压和电流在过去 的几年没有出现变化,但要求保护IC的安全电压电平却降低了。过去,IC设计对于(防范)ESD而言更具强固性,而且能够承受更高电压,因此,在选择能符 合IEC61000-4-2第4级的要求的保护二极管时有充分的选择余地。而对于如今ESD更敏感的IC,设计工程师就必须不仅要确保保护器件能够符合 IEC61000-4-2第4级标准,而且还要确保该器件能够将ESD脉冲钳制到足够低的电平,从而确保IC不受损坏。在为给定的应用选择最佳保护器件的 时候,设计工程师必须要考虑到ESD保护器件能够把ESD电压控制到多么低的电平。

如何选择最有效的保护方案

保护二极管的关键直流(DC)规范是击穿电压、漏电压和电容。大部分数据表也会说明IEC61000-4-2的最大额定电压,该电压指的是二极管在该电压上 不会被ESD冲击损坏。所存在的问题是,大部分数据表中没有任何针对象ESD这样的高频率、高瞬态电流的钳位电压方面的信息。可是要详细说明,要在 IEC61000-4-2规范中硬性规定钳位电压不是一件简单的事情,这是因为该规范的初衷是用来检验系统是否合格,并且频率是如此高。要把这种规范来检 验保护器件,关键的是不仅要检查保护二极管是否合格/不合格,还要检查它能把ESD电压钳位到多么低的电平。

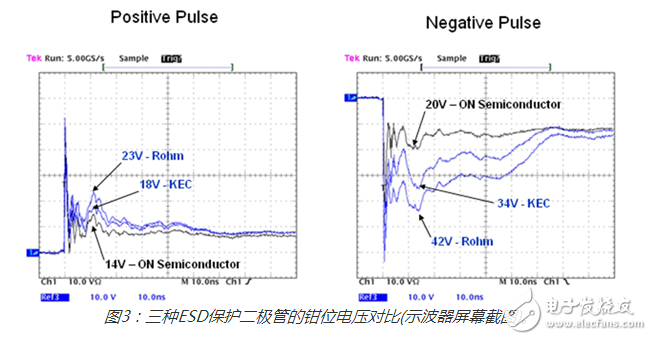

比较保护二极管钳位电压的最好途径是采用一台示波器截取保护二极管两端在ESD产生期间内的实际电压波形。

几种保护二极管的比较

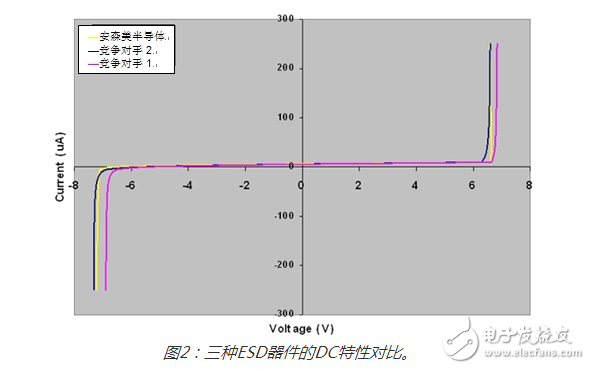

为了进行公平的比较,所选元器件应当有相似的封装尺寸和参数指标。用来比较的是三 只ESD保护二极管,当对它们的电特性进行比较时,认为这些器件可以彼此互换。这些器件都是双向的ESD保护器件,具有同样的击穿电压(6.8 V)、电容(15 pf)和封装外形(1.0 &TImes; 0.6 &TImes; 0.4 mm)。这里所选择的产品分别是竞争对手1的RSB6.8CS、竞争对手2的PG05DBTFC和安森美半导体的ESD9B5.0ST5G。

当 对以上器件的DC性能进行比较的时候,结果看起来似乎是相同的(参见图2所示曲线)。此外,它们都声称符合IEC61000-4-2第4级标准,这就意味 着它们将都经受住高达8 kV接触电压的ESD冲击。确保保护敏感IC的ESD保护器件至关重要的性能不是DC性能; 尽管器件符合IEC61000-4-2的第4级标准是重要,但更重要的是保护IC。为确保在ESD事件期间IC没有被损坏,保护二极管必须把ESD电压钳 位至足够低的值,使IC不会损坏。

为了比较每个器件的钳位性能,利用示波器来截取ESD发生期间的电压波形。利用完全相同的测试条件,对上述器件进行并排测试。图3中显示出每个二极管对正/负ESD脉冲的响应曲线。所用的输入脉冲为IEC61000-4-2第4级的标准接触电压(8 kV)。

从 图3所示的屏幕图上可见,显然,与两个竞争对手的器件(蓝色波形)相比较,安森美半导体保护解决方案(黑色波形)提供更低的ESD脉冲钳位电压。与竞争对 手2的18 V和竞争对手1的23 V相比较,安森美半导体的器件将正脉冲钳位在14 V。而在负脉冲期间,这三个器件之间钳位电压的差异更加明显。安森美半导体、竞争对手2和竞争对手1的器件对负脉冲的钳位电压分别是20 V、34 V和42 V。在负ESD脉冲期间这三种器件之间有明显的区别,竞争对手2的器件的钳位电压比安森美半导体的器件高70%,而竞争对手1的器件的钳位电压则是安森美 半导体器件的两倍之多。通过竞争对手的保护器件后的剩余负脉冲电压对那些更容易受到ESD破坏的新IC设计有潜在的危险。然而,安森美半导体的器件却能在 负脉冲和正脉冲两个方向上保持低的钳位电压,从而将遭受正/负ESD脉冲的破坏风险都保持在最低水平。

好的保护器件需要对 正/负ESD脉冲都能进行很好的钳位,以保证终端产品在实际条件下具有最高的可靠性。在正/负两个方向上的低钳位电压确保保护器件能保护极敏感的IC,这 使得设计工程师能利用可以实现更多功能和更高速度的最新IC技术。由于认识到在选择ESD保护器件时钳位电压的重要性日益提高,很多提供保护器件的公司在 他们最新ESD保护器件的数据表中提供了类似图3中的ESD钳位屏幕截图。

ESD静电保护元件分析

任何保护元件在正常工作期间必须作为高阻抗电路出现在受保护的输入端。它所施加的电容负载必须尽可能的小,使得对正常的输入信号几乎没有影响。然而, 在过压的瞬间,同一器件必须成为能量的主要通路,把能量从被保护器件的输入端转移出去。此外,保护器件的安全(standing-off)电压必须高于受保护端所允许的最大信号电压。同样,其箝位电压必须低到足以防止所保护的器件遭受损坏,这是由于在瞬态发生期间,输入端上的电压将是保护器件的箝位电压。

我们常常会看到介绍ESD静电保护器、ESD静电阻抗器、ESD静电释放器、贴片压敏电阻等产品,但其实保护器件最关键的参考系数应该是下面三项:

1. 快速响应时间

2. 低箝位电压

3. 高电流浪涌承受能力

无论产品被介绍得多么优异,在选择ESD静电保护元件时,仍应该细致地做好实际的对比,以及运用IEC61000-4-2测试来做验证。目前行业惯例是根据8us上升时间和20us持续时间的脉冲公布箝位电压的,而真正的ESD脉冲应该是1ns上升时间和60ns的持续时间。