数字控制实现带有源缓冲的高可靠性DC-DC功率转换

品慧电子讯一般而言,在高输出电流隔离式DC-DC电源应用中,使用同步整流器(尤其是MOSFET)是主流趋势。高输出电流还会在整流器上引入较高的di/dt。为了实现高效率,MOSFET 的选择主要取决于导通电阻和栅极电荷。然而,人们很少注意寄生体二极管反向恢复电荷(Qrr)和输出电容(COSS)。这些关键参数可能会增大MOSFET漏极上的电压尖峰和振铃。一般而言,随着MOSFET击穿电压额定值的增大,导通电阻也会增大。

本文提出一种数控有源钳位吸收器。该吸收器既可消除同步整流器上的电压尖峰和振铃,还能发挥设计指南作用;在隔离式DC-DC转换器(如半桥和全桥拓扑结 构)中拥有多种其他优势,同时还能提高可靠性,降低故 障率。

简介

人们总是希望使用平均故障间隔时间(MTBF)较高的高可靠性电源。要打造稳健的设计,可以使用额定击穿电压较高的开关。但这样做会丧失一定的效率。因此,高效率和高可靠性在实际应用中往往不可兼得。作为新一代电源解决方案的一部分,工业界一直对高效率隔离式DC-DC转换器保持着稳定的需求。这就要求在副边使用同步整流器。整流器的额定值一般是器件电 压尖峰的1.2至1.5倍。电压尖峰由漏感、寄生走线电感和整流 器输出电容(COSS)形成的谐振所导致,谐振峰值可能高达整流器 稳态反向电压的两倍。一种解决方案是用无源吸收器充当RC1或 RCD2。虽然这些器件非常流行,但有损耗,会导致效率略微下 降。用于制造无损吸收器的部分技术采用的是再生吸收器(如 LCD3),但吸收器仅用于原边开关,或者只在电源开关关闭而 非开启期间使用RC吸收器。其他技术4,5运用泄漏电能来驱动小 型高效率转换器,馈入输出电压终端。但这要求使用更多的元 件。其他技术6则将有源钳位吸收器用于全桥相移拓扑结构,以 便消除在ZVS软开关应用中由原边谐振电感导致的谐振,但仅限于低占空比应用。

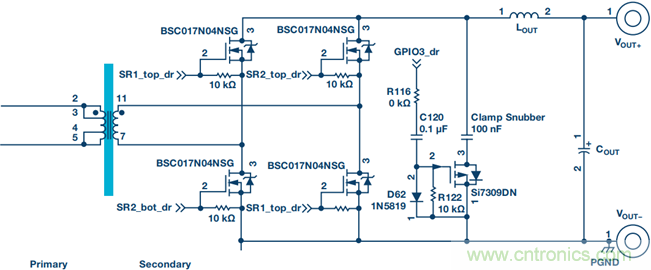

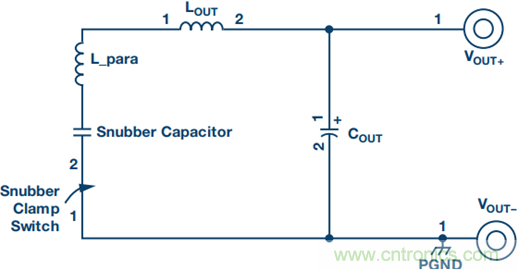

本文将深入探讨有源钳位吸收器电路及其数字实现方式,该吸收器电路可以避免电压偏移,特别是能消除MOSFET中寄生二极管的反向恢复损耗,还具有多种其他优势。转换器(仅副边)功率级示意图如图1所示。

图1. 功率转换器副边(图中所示为有源钳位)

图1展示的是一款隔离式DC-DC转换器的副边。副边由同步整流 构成,同步整流表现为连接变压器的H-桥。另外还有输出滤波 器电感(LOUT)和输出滤波器电容(COUT)。有源钳位开关是一个P沟道 MOSFET,用于转换栅极信号电平的栅极驱动由一个电容和一个二极管构成。

高频等效电路

在高频视图中,大电感和大电容分别处于开路和短路状态,电路分析中只使用寄生和谐振电感及电容。利用这种方法可以简化电路,以便分析交流电流。该方法特别适用于谐振拓扑结构和使用吸收器的场合,因为在缓冲周期中,高频电流会选择阻抗最低的路径。

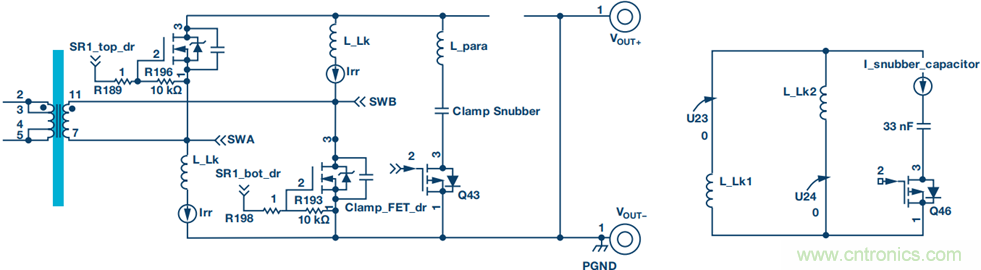

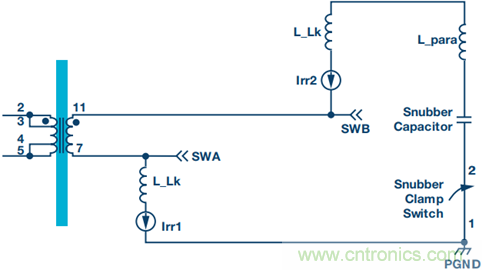

电路的交流视图如图2所示。输出滤波电感和电容分别处于开路和短路状态。在电路中,MOSFET的输出电容和漏电电感保持原样。重点是转换器的副边,因为原边电压源已短路并且对分析无用。

图2. (左)功率转换器副边AC视图(图中所示为有源钳位)(右)简化的AC视图。

同步FET有源钳位电路的工作原理

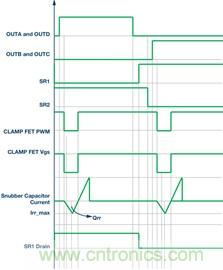

在分析中,我们假设,吸收器电容足够大,能维持电压恒定不变。在续流间隙(在图3中,SR1和SR2均开启),四个副边开 关(MOSFET)全部开启。受有限上升和下降时间以及栅极驱动信 号传播延迟变化的影响,同步整流器信号之间始终存在较短的 死区时间。在该死区时间期间,MOSFET的寄生二极管会导通以续流。其后是下一半开关周期,此时,原边MOSFET的另一个引脚启动。这会导致变压器绕组上的极性发生变化,同时关闭同 步整流器体二极管。然而,只要反向恢复电荷(Qrr)未耗尽,同步MOSFET的寄生二极管就不会关闭。方向如图2所示。该Qrr被视为作为前沿尖峰从变压器反映到原边的多余电流。这还会增大同步MOSFET漏极上的电压尖峰。反向恢复电荷的大小由下式 计算得到:

![]()

图3

图4a. trr间隔捕获反向恢复能量期间的工作情况

图4b. 负载中释放的能量

漏电电感和走线电感(极性如图2所示)导致的电压尖峰由有 源钳位吸收器吸收。有源吸收器开关可以在寄生二极管开启后 在ZVS时打开。然而,当有源钳位吸收器开启时,吸收器电容会吸收反向恢复电流并把捕获的能量重新注入副桥和负载中。由于通过吸收器电容的净电流为零,所以只要转换器工作于稳态下,吸收器就会维持电荷平衡。

设计指南

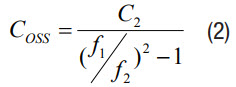

1. 估算漏电电感

让转换器在无吸收器的条件下工作,测量同步MOSFET漏极上振 铃电压尖峰的谐振频率和周期(f1)。另外,测量原边电流波形上的前沿尖峰(应等于trr)。要估算漏电电感,要使电容的已知值(C2)至少比MOSFET漏极/源极电容大一个数量级。用下式测量 振铃频率(f2),计算电容(COSS)和漏电(LLK)电感:

![]()

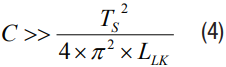

2. 选择有源钳位吸收器电容

选择一个输出电容至少为同步MOSFET输出电容10至100倍的吸收器电容。这是因为有源吸收器开关会有一条低阻抗路径。然而,吸收器电容的选择必须做到:

其中,Ts为开关周期。

在下列最小延迟条件下打开有源钳位吸收器:

![]()

这两项为驱动器的传播延迟和原边MOSFET的驱动信号上升时间。这个时序非常重要,因为必须捕获MOSFET体二极管的全部反向恢复能量。该时间取决于同步MOSFET体二极管的反向恢复特性(Qrr、trr、Irr),可能随器件上的温度、负载电流和反向电压等因素而变化。延迟时间和吸收器导通时间可以用本文所述方法精确设置以针对不同的开关特性进行优化。

确定钳位电容值的另一种方法是使用以下公式。该公式基于谐振周期,在此期间,将漏电电能释放到钳位电容中。

![]()

该值的范围为:

![]()

为了避免在第1点上观察到过多的振铃,导通时间应不超过一个或两个谐振周期,否则,会出现过多的连续振铃。或者,吸收器的导通时间可以取上面第1点中观察到的前沿尖峰的导通时间的近似值(如trr)。过多的导通时间只是会导致能量再谐振几个周期,可以在原边电流波形中看到这一点(图8和图9)。

3. 选择吸收器开关

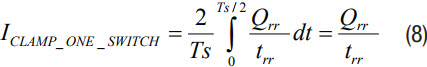

(1)的一个简化版本是使用MOSFET数据手册中的最差条件限值。以下公式更加详细地展现了电容中电流的情况:

使用因子2是因为考虑的只是半个开关周期,对于全桥或半桥拓扑结构,该过程发生两次。另外,在图1中,由于两个开关关闭,所以反向恢复电荷会增加一倍。因此,总电流为:

![]()

其中,在全桥配置下,C为2;在中心抽头配置下,C为1;N为 并联的MOSFET数目。这是通过有源吸收器开关的平均电流。

数字实现

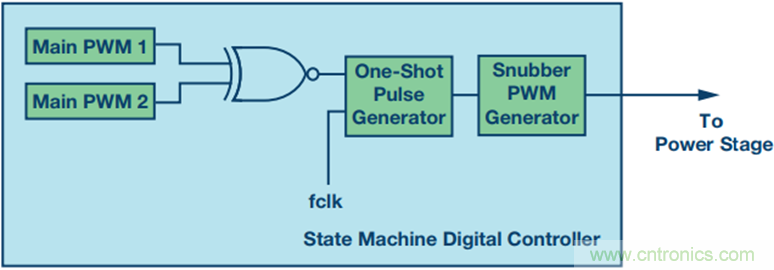

有源钳位吸收器的数字实现有两个控制:控制1是吸收器延迟(自触发器边沿的吸收器PWM边沿中的可调延迟)。控制2为吸收器PWM导通时间。触发点为H桥对边引脚原边PWM上升沿的逻辑OR(如OUTC和OUTD)。吸收器PWM并不要求像主控 PWM分辨率一样高的分辨率(如125 ps)。结果,触发所需时 钟能支持较慢的速率(5 ns分辨率),这样还能节能(40倍系 数)。这一概念也可以运用到副边上有中心抽头的功率转换拓 扑结构。另外,该概念也可以用于单个开关,在这些开关中,每个功率晶体管上会放置一个分立式有源钳位开关吸收器单元。在这种情况下,有源钳位FET的驱动信号取自同步整流器的下降沿。

图5. 吸收器PWM的数字实现

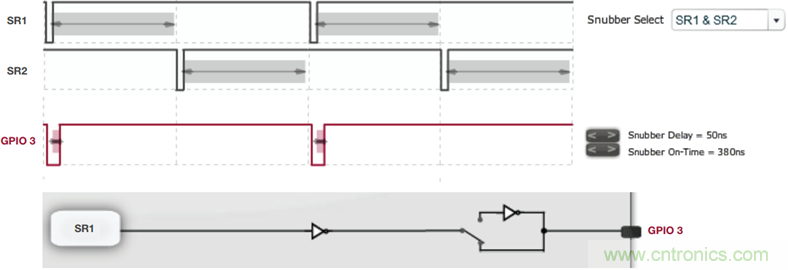

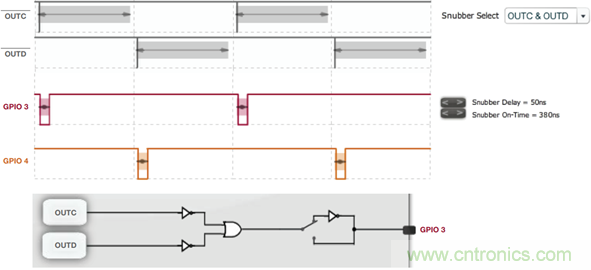

ADP1055数字控制器提供了实现这一目标的必要工具。借助直观简单的图形用户界面,只需几分钟就能完成有源钳位吸收器的优化。ADP1055提供了两个选项来设置吸收器PWM,即通过SR1 和SR2的逻辑组合或通过OUTC和OUTD信号的逻辑组合。在两种情况下,可以用两个选项配置吸收器PWM,如图6和图7所示。在上述所有情景下,都可以用吸收器延迟(设置死区时间)和吸收器导通时间微调优化参数。借助两个信号的逻辑组合和极性选择功能,用户完全可以自由地选择适当的吸收器组合。

图6. 使用选项1(SR1和SR2)的吸收器时序

图7. 使用选项2(OUTC和OUTD)的吸收器时序

全桥拓扑结构的实验结果

为了进行实验验证,选择的隔离式DC-DC转换器,其额定输入为48 V,额定输出为12 V、20 A,开关频率为125 kHz。拓扑结构为全桥,带一个副边,如图1所示。

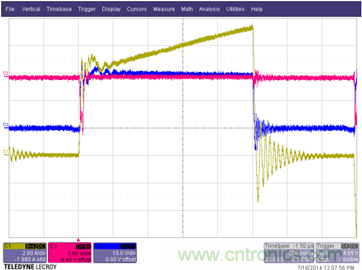

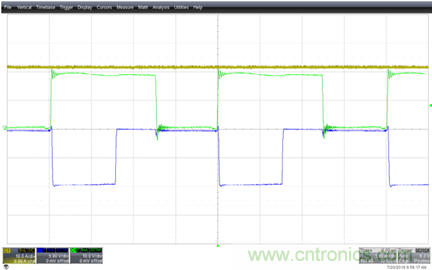

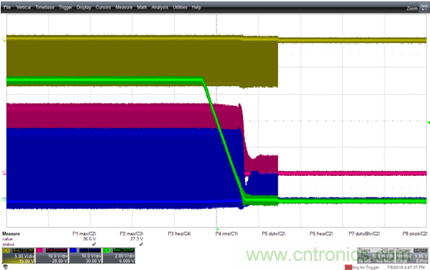

图8展示了使用不正确的吸收器导通时间会导致多余振铃,同时 还展示了同步MOSFET的振荡漏极电压,后者也反映在原边电流中。前沿尖峰也很严重,会导致不必要的EMI。

图8. 过多的吸收器导通时间

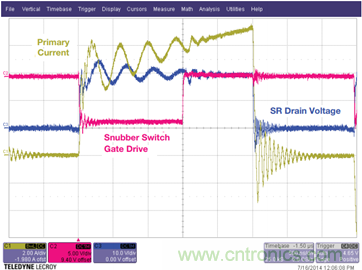

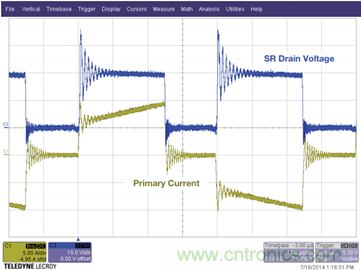

图9所示为优化的吸收器导通时间,其中,在同步MOSFET的漏极电压上无振铃。同时,前沿尖峰也几乎消除了。

图9. 优化的吸收器时序

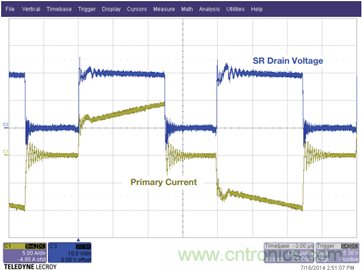

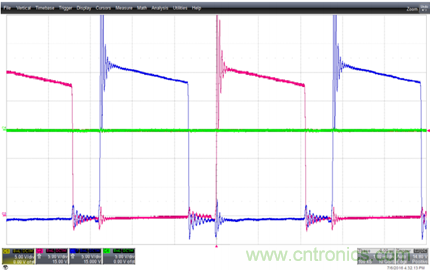

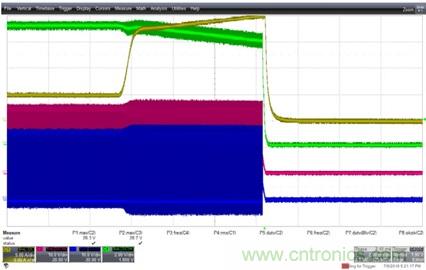

图10所示为同步MOSFET在有源钳位吸收器不存在条件下的漏极电压。电压偏移可能非常严重,达稳态电压的1.5倍,并且MOSFET有可能进入雪崩条件。

图10. 不存在有源钳位吸收器

图11所示为有源钳位吸收器的有效性。前沿尖峰被完全消除, MOSFET漏极上无振铃。

图11. 存在有源钳位吸收器

图12. 0 A负载条件下的吸收器有效性

- 绿线:SR漏极,10 V/div

- 蓝线:钳位FET栅极-源极电压,5 V/div

- 黄线:负载电流,10 A/div

图13. 20 A负载条件下的吸收器有效性

- 绿线:SR漏极,10 V/div

- 蓝线:钳位FET栅极-源极电压,5 V/div

- 黄线:负载电流,10 A/div

半桥拓扑结构的实验结果

对半桥拓扑结构进行了额外的实验验证,额定输入为48 V,额定输出为9 V、200 W,开关频率为180 kHz。

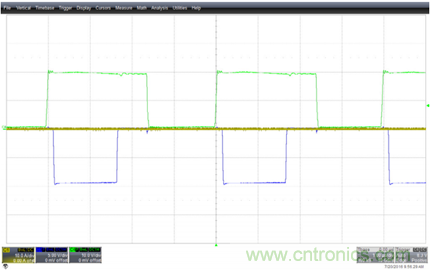

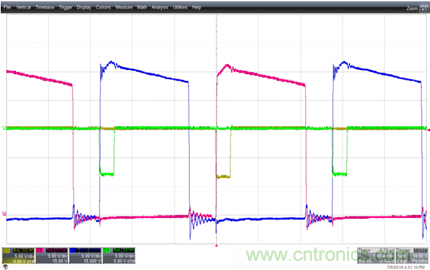

图14. 有源钳位吸收器禁用

- 红线:SR1漏极,5 V/div

- 蓝线:SR2漏极;5 V/div

- 绿线:吸收器PWM,5 V/div

图15. 有源钳位吸收器使能

- 红线:SR1漏极,5 V/div

- 蓝线:SR2漏极;5 V/div

- 绿线:吸收器PWM,5 V/div

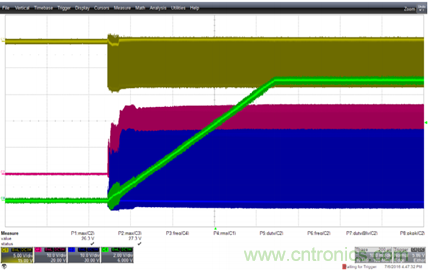

图16. 有源钳位吸收器条件下软启动期间的SR漏极波形

- 黄线:吸收器FET栅极-源极电压,5 V/div

- 红线:SR1漏极,10 V/div

- 蓝线:SR2漏极,10 V/div

- 绿线:输出电压,2 V/div

图17. 有源钳位吸收器条件下软启动期间的SR漏极波形

- 黄线:吸收器FET栅极-源极电压,5 V/div

- 红线:SR1漏极,10 V/div

- 蓝线:SR2漏极,10 V/div

- 绿线:输出电压,2 V/div

图18. 短路测试过程中的SR漏极电压

- 黄线:负载电流,5 A/div

- 红线:SR1漏极,10 V/div

- 蓝线:SR2漏极,10 V/div

- 绿线:输出电压,2 V/div

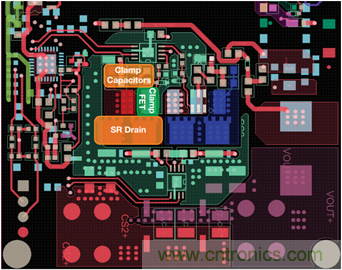

布局考虑

图8所示为上述半桥拓扑结构的布局。关键点是通过缩短环路或将其限制在较窄区域,减小钳位环路的寄生电感。否则会降低钳位的有效性,并在钳位周期内导致高频振铃。

图19. 有源钳位吸收器布局

结论

本文展示了有源钳位吸收器电路在隔离式DC-DC转换器高输出电流应用中的数字实现方式。提出的有源-钳位方案具有多种优势,比如更低的钳位电压,可以降低MOSFET 额定击穿电压,从而提高效率。同时还消除了振铃,结果可以减少电磁干扰(EMI)。这是一种低成本的简单电路,驱动方案也很简单。另外,与需要额外电感的其他有源吸收器相比,还可以节省PCB板空间。整体而言,电源的可靠性得到了大幅提升。此外,消除了前沿尖峰,结果降低了对原边开关的压力。另外,更高的效率可以降低发热量,这对散热困难的受限区域中的模块非常有用。

ADP1055数字控制器提供了实现上述任务的必要工具,无需编写复杂的程序或代码。ADP1055还支持多种其他功能,比如黑盒、软停、命令掩码、非线性增益等。

参考电路

1 K. Harada, T. Ninmomiya, and M. Kohno.“Optimum Design of RC Snubbers for Switching Regulators.”(优化开关调节器RC吸收器的设计)IEEE Transactions on Aerospace and Electronic Systems, Vol. AES–15, pp. 209–218, 1979.

2 C.G.Steyn.“Optimum Size of Dissipative Nonlinear Turn-Off Snubber.”(耗散式非线性关机吸收器的最佳尺寸)IEE Proceedings, Vol. 135, Pt. B, No. 4, 1988.

3 C.K.Huang, C.T.Chen, H.H.Nien, S.K.Changchien, and H.W.Shieh.“Optimal Design of Lossless Passive Snubber for DC/DC Converters.”(面向DC/DC转换器的无损无源吸收器的优化设计)First International Conference on Innovative Computing, Information and Control, Vol. 1, pp. 559–602, 2006.

4 M. Cacciato and A. Consoli.“New Regenerative Active Snubber Circuit for ZVS Phase Shift Full-Bridge Converter.”(面向ZVS相移全桥转换器的新型再生有源吸收器电路)Applied Power Electronics Conference and Exposition, pp. 1507–1511, 2011.

5 T. F. Wu, Y. C. Chen, J. G. Yang, and C. L. Kuo, (2010).“Isolated Bidirectional Full-Bridge DC–DC Converter with a Flyback Snubber.”(带反激式吸收器的隔离式双向全桥DC–DC转换器)IEEE Transactions on Power Electronics, Vol. 27, No. 7, pp. 1915–1922.

6 J.A.Sabate, V. Vlatkovic, R.B.Ridley, and F.C.Lee.“High Voltage High Power, ZVS Full-Bridge PWM Converter Employing an Active Snubber.”(采用有源吸收器的高电压高功率、ZVS全桥PWM转换器)IEEE APEC 1991, ~158–16.

本文转载自亚德诺半导体。