深入分析“时间交错技术”

品慧电子讯时间交错技术可使用多个相同的 ADC(文中虽然仅讨论了 ADC,但所有原理同样适用于 DAC 的时间交错特性),并以比每一个单独数据转换器工作采样速率更高的速率来处理常规采样数据序列。简单说来,时间交错(IL)由时间多路复用 M 个相同的 ADC 并联阵列组成。

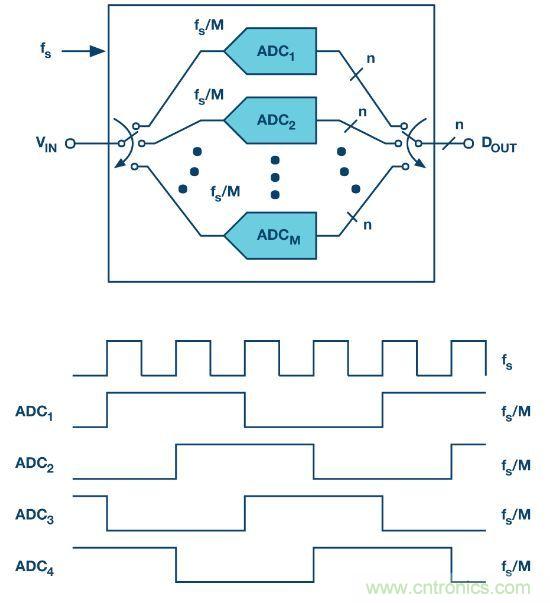

如图 1 所示。这样可以得到更高的净采样速率 fs(采样周期 Ts = 1/fs),哪怕阵列中的每一个 ADC 实际上以较低的速率进行采样(和转换),即 fs/M。因此,举例而言,通过交错四个 10 位/100 MSPS ADC,理论上可以实现 10 位/400 MSPS ADC。

图1. M次交错的n位ADC阵列每一个ADC的采样速率为fs/M,得到的时间交错ADC采样速率为fs。M = 4的时钟方案示例在该图下半部分显示。

为了更好地理解 IL 原理,图 1 中一个模拟输入 VIN (t) 以 M 个 ADC 进行采样,其结果为组合数字输出数据序列 DOUT。ADC1 最先采样 VIN (t0) 并开始将其转换为n位数字信号。Ts 秒后,ADC2 将采样 VIN (t0+Ts) 并开始将其转换为n位数字信号。接着,Ts 秒后,ADC3 将采样 VIN (t0 +2Ts),以此类推。ADCM 完成 VIN (t0 +(M-1)×Ts) 采样后,开始下一个采样周期,并从 ADC1 采样 VIN (t0 +M×Ts) 开始,依次进行下去。

由于ADC顺序输出n位数据且输出顺序与刚才描述的采样操作顺序一致,这些数字n位字由同一张图右侧的解复用器所采集。这里获取的是重新组合的数据输出序列 DOUT (t0 + L),DOUT (t0 +L + Ts),DOUT (t0 + L + 2Ts),... 。L 表示每一个单独ADC的固定转换时间,而该重新组合的数据序列是一个 n 位数据序列,采样速率为 fs。因此,虽然各个ADC(通常称为“通道”)为 n 位 ADC 且采样速率为 fs/M,但整体等于采样速率为 fs的单个 n 位 ADC,而我们将其称为时间交错 ADC(与通道相区别)。输入本质上是分隔开的,并由阵列中的 ADC 单独处理,然后在输出端连续重组,以便构成输入 VIN 的高数据速率表示 DOUT。

这种强大的技术在实际使用时存在一些难题。一个重要的问题是来自通道的M数据流经过数字组装后重构原始输入信号 VIN。如果我们看一下频谱 DOUT;除了看到 VIN 的数字信号以及模数转换引入的失真,我们还将看到额外的和大量的杂散成分,称为“交错杂散”(或简称为 IL 杂散);IL 杂散既没有多项式类型失真的签名——比如较高次信号谐波(2次,3次,等等)——也没有量化或 DNL 误差签名。IL 伪像可视为时域固定码噪声的一种形式,由通道中的模拟损害引起,因为在交错过程中采用分隔转换信号进行调制并出现在最终的数字化输出 DOUT。

让我们分析一个简单的示例,了解可能会发生什么情况。考虑频率 fIN 下正弦输入 VIN 的双路交错 ADC 情况。假定 ADC1 具有增益 G1,ADC2 具有差分增益 G2。在这种双路 IL ADC中,ADC1 和 ADC2 将交替采样 VIN。因此,如果 ADC1 转换偶数样本,而 ADC2 转换奇数样本,则所有 DOUT 偶数数据的幅度都将由 G1设置,而所有 DOUT 奇数数据的幅度都将由G2设置。然后,DOUT 不仅包含 VIN,还包括一些多项式失真,但它受到 G1 和G2 的交替放大,就好像我们采用频率为 fs/2 的方波对 VIN 进行幅度调制。这样做会引入更多杂散成分。特别地,DOUT 在 fs/2 – fIN 频率处会包含“增益杂散”;并且不幸的是,该杂散的频率会跟踪输入fIN,且位于交错 ADC 的第一奈奎斯特频段内(即在 fs/2 内),而在所有其它奈奎斯特频段内也会存在混叠。该交错杂散的功率/幅度取决于两个增益 G1和G2 之间的净差。换言之,它取决于增益误差失配。而最终,它取决于输入 VIN 自身的幅度。

如果输入并非简单正弦波,而是真实应用中的全频带限幅信号,那么“增益杂散”就不只是干扰音了,而是频带限幅输入信号自身的完整调节镜像,出现在奈奎斯特频段内。这在一定程度上抵消了交错带来的带宽增加的优势。

虽然上例中我们仅考虑了通道间的增益误差失配,其它损害也会引起交错杂散。失调失配(通道失调之间的差)引起固定频率的信号音(“失调杂散”),功率与失调失配成正比。当某些通道比预定顺序更早或更晚采样某位时,便发生采样时间偏斜。它会引入“时间杂散”,其频率与增益杂散全一致(并叠加同样的幅度),但功率会随着 fIN 的增加以及输入幅度的增加而不断加强。各通道之间的带宽失配会引入更多的杂散成分,频率取决于 fIN,并且正如时间杂散,杂散功率不仅随着输入幅度,而且还会随着fIN自身而逐步增加。再次强调,无论何种情况,输出频谱下降的程度并不取决于通道损害的绝对值(失调、增益、时序、频段),而是取决于通道之间的相对失配或通道之差。

虽然时间交错的基本技术存在已有几十年,但IL可在何种程度上保持最小化则将其过去的适用性限制于低分辨率转换器。然而,最近在通道失配校准方面以及抑制残留IL杂散成分方面的进步已经可以实现全集成、极高速、12/14/16 位 IL ADC。

这种情况下,我们需要对交错进行分类。我们一般将两个交错通道称为“乒乓”工作。然后,当我们描述较少通道数的情况(比如 3 通道至4通道),以及大量通道的情况时(比如超过 4 个通道,通常达到 8 个或更多),我们还区分了“轻度交错”和“重度交错”。

乒乓(双路)交错

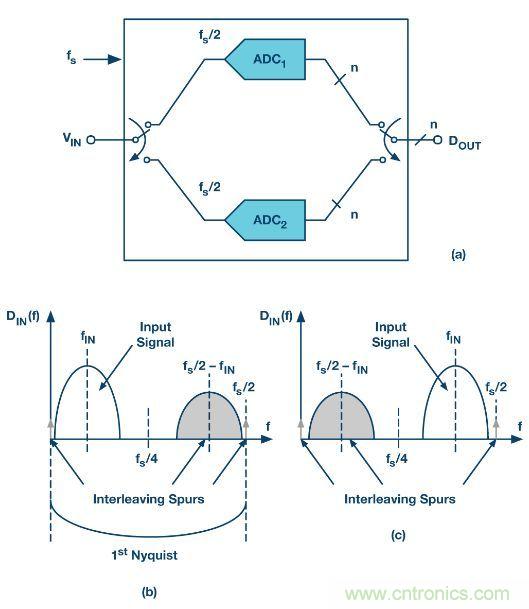

当我们只是交错两个通道以便使采样速率翻倍时,我们将其称为“乒乓”,如图 2 (a) 中的框图所示。这是一种最简单的情况,它有一些有趣和有用的特性。这种情况下,在交错ADC的第一奈奎斯特频段内,交错杂散位于直流、fs/2 和 fs/2 – fIN 处。因此,如果输入信号VIN是一个对中至fIN的窄带信号——如图 2 (b) 中的第一奈奎斯特输出频谱所示——交错杂散包含直流处的失调杂散、fs/2 处的另一个失调失配杂散以及对中至 fs/2 – fIN 的增益和时序杂散镜像,看上去就像输入自身的一个放大复制版本。

图2.

(a)乒乓方案

(b)窄带输入信号位于fs/4以下时的输出频谱

(c)此时输入信号位于fs/4和奈奎斯特频率fs/2之间

如果输入信号 VIN(f) 完全位于 0 和 fs/4 之间——如图 2 (b) 所示——那么交错杂散不与数字化输入频率重叠。此时,坏消息是我们只能数字化半个奈奎斯特频段,就好比只有一个时钟为 fs/2 的单通道,虽然我们依旧消耗至少两倍于该单个通道的功耗。奈奎斯特频段上限的交错杂散镜像可在数字化之后通过数字滤波手段抑制,无需进行模拟损害校正。

但好消息是由于乒乓ADC时钟为 fs,数字化输出得益于动态范围内的 3 dB 处理增益。此外,与使用时钟为 fs/2 的单个 ADC 相比,乒乓 ADC 放宽了抗混叠滤波器设计要求。

如果窄带信号位于第一奈奎斯特频段的上半部,则所有考虑因素都适用,如图 2 (c) 所示,因为交错镜像杂散移至奈奎斯特频段的下半部分。再次强调,增益和时序杂散可在滤波数字化之后通过数字手段抑制。

最后,输入信号和交错杂散的频率将会重叠,并且一旦输入信号频率位置跨过 fs/4 线,交错镜像就会破坏输入频谱。这种情况下,恢复所需输入信号将是不可能的,而乒乓方案不可用。当然,除非通道间匹配足够紧密,使得交错杂散成分对于应用来说达到可以接受的低程度,或者引入校准来降低导致IL镜像的原因。

总之,频率规划和某些数字滤波可以恢复乒乓方案中的窄带数字化输入,哪怕存在通道失配。虽然转换器功耗相比使用单个时钟为 fs/2 的 ADC 时基本翻了个倍,但乒乓方案提供了 3 dB 处理增益,同时放宽了抗混叠要求。

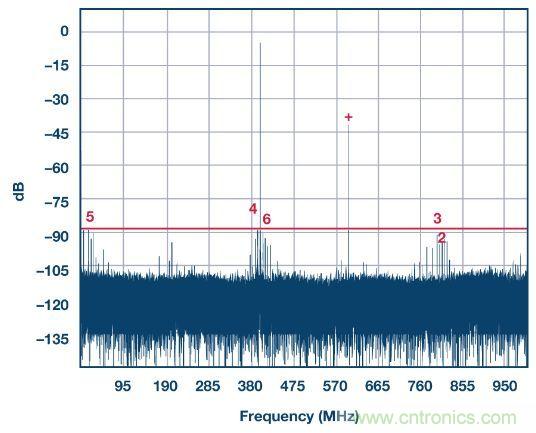

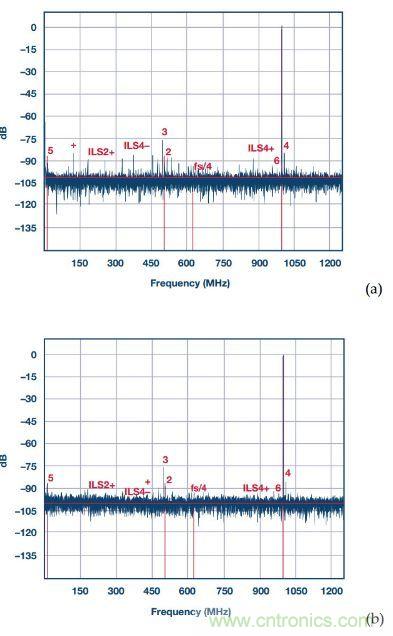

采用乒乓方案并且无任何通道失配校正的一个示例,以及其产生的交错杂散见图 3。在该例中,两个双通道 14位/1 GSPS ADC AD9680 以交替乘以正弦波的速率进行采样,从而返回单个组合输出数据流,速率为 2 GSPS。当我们查看该乒乓方案输出频谱的第一奈奎斯特频段时(位于直流和 1 GHz 之间),可以看到输入音,它是 fIN = 400 MHz 时位于左侧的强音;我们还能看到在 fs/2 – fIN = 2G/2 – 400 M = 600 MHz 处有较强的增益/时序失配杂散。由于通道本身的失真以及其它损害,我们还能看到一系列其它信号音,但都低于–90 dB 线。

图3. 乒乓方案的2 GSPS输出数据组合频谱,采用两个AD9680在1 GSPS时钟下获取,采样相移为180°。

更高次交错

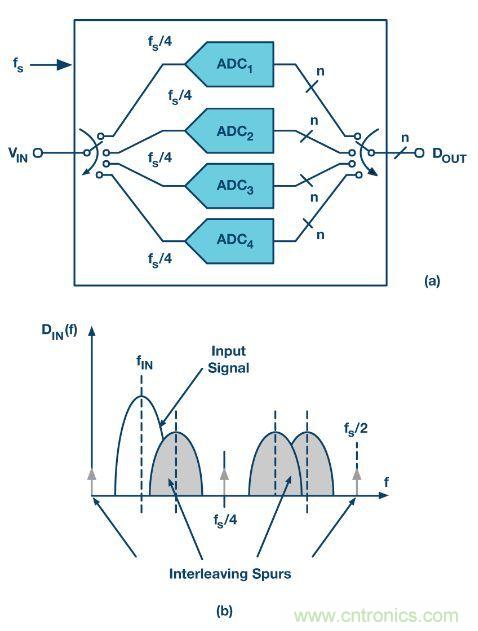

当具有两个以上通道时,上文所说的频率规划就不那么实用了。我们无法将交错杂散的位置限定在奈奎斯特频段的某一小部分。比如考虑四路交错 ADC 的情况,如图 4(a) 所示。此时,失调失配会提高直流、fs/4 和 fs/2 时的信号音,而增益和时序交错镜像位于fs/4 – fIN、fs/4 + fIN和fs/2 – fIN。交错 ADC 输出频谱的一个示例请参见图 4 (b)。很明显,除非输入位于fs/8以内的带宽之内,否则无论 fIN 的位置如何,输入都会与部分交错杂散重叠,并且如果输入是一个极端窄带信号,那么我们不应当尝试使用宽带交错 ADC将其数字化。

在这种情况下,我们需要最大程度降低 IL 杂散功率,以便获得完整的奈奎斯特频谱和更干净的频谱。为了达到这个目的,我们使用校准技术来补偿通道间失配。校正失配的影响后,最终的 IL 杂散功率会下降。SFDR 和 SNR 都会得益于该杂散功率的下降。

补偿方法受限于失配可测量并最终校正的精度。除了校准所能达到的水平外,为了进一步抑制残留杂散,还可间歇性随机打乱通道输入采样的顺序。这样做之后,前面讨论的由于未校准失配而产生的转换输入信号调制效果将从固定码噪声转换为伪随机噪声。因此,IL音和干扰周期码转换为伪随机噪声类成分,并叠加至转换器量化噪底而消失,或者至少将干扰杂散镜像和信号音加以扩散。此时,与 IL 杂散成分有关的功率叠加至噪底功率。因此,虽然改善了失真,但 SNR 可能下降,下降量为 IL 杂散功率加上噪声。SNDR (SINAD) 基本上没有变化,因为它由失真、噪声和随机化组成;它只是将IL贡献因素从一个成分(失真)转移到另一个成分(噪声)。

图4. (a)四路交错ADC(b)对应显示交错杂散的第一奈奎斯特输出频谱

交错 ADC 的示例

AD9625 是一个12位/2.5GSPS 三路交错 ADC。对三个通道之间的失配进行校准,以便最大程度减少交错杂散。图 5(a) 所示是一个输入接近 1 GHz的输出频谱示例。在该频谱中,除了约为 1 GHz的输入音外,还可以看到通道在 500 MHz 附近存在 2 次和 3 次谐波失真,并在基频处存在 4 次谐波失真。交错失配校准可大幅降低交错杂散的功耗,并且在整个频谱中可以看到大量的额外残留的较小杂散音。

为了进一步减少这些残留杂散成分,引入了通道随机化。加入了第四个校准通道,然后将四个通道变为三路交错,并通过间歇性将交错通道与第四个更换,实现随机改变顺序。这就好比人们可以像耍杂技那样将三根柱子投向空中,然后每一次都更换第四根。这样做之后,可使残留交错杂散功率随机化,然后扩散到噪底。如图 5(b) 所示,经过通道随机化之后,交错杂散几乎消失了,而噪声功率却只略为增加,因而 SNR 降低 2dB。当然,需要注意的是,虽然图 5(b) 中的第二个频谱比失真音远为干净,但随机无法影响 2 次、3 次 和4 次谐波,因为这些谐波不是交错杂散。

图5. AD9625的输出频谱,时钟为2.5 GSPS,输入音接近1 GHz。

(a)顺序三路交错;SNR = 60 dBFS,SFDR = 72 dBc,受限于3次谐波,接近500 MHz;然而,整个频谱中可见大量交错杂散。

(b)三路交错,随机通道置乱;SNR = 58 dBFS,而SFDR = 72 dBc依然由3次谐波决定,通过将功率扩散到噪底而消除了所有交错杂散。

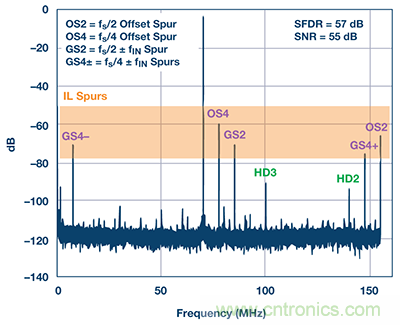

使用通道随机化的另一个交错 ADC 示例如图 6 中的频谱所示。此时采用四路交错 16位/310 MSPS ADC AD9652。图 6 示例中,四个通道以固定顺序交错,并且不进行任何减少通道失配的校准。频谱清楚表明交错杂散位于预计频率位置,且它们的大功率远高于 2 次和 3 次谐波,并将无杂散动态范围限制为仅有 57 dBc。

图6. AD9652的输出频谱,时钟为 fs=310 MHz,采用fIN ~70 MHz的正弦输入。此时,未施加通道校准和随机化。2次(HD2)和混叠3次(HD3)谐波分别在大约140 MHz和100 MHz处可见。交错(IL)杂散同样可见。这些是直流、fs/2(图中的OS2)以及fs/4(图中的OS4)处的失调音。另外,增益(时序)杂散可见于fs /2-fIN(图中的GS2)、fs /4+fIN(图中的GS4+)以及fs /4- fIN(图中的GS4-)。此图中的SNR查询人为变差了,因为部分杂散成分和噪声功率混在了一起。

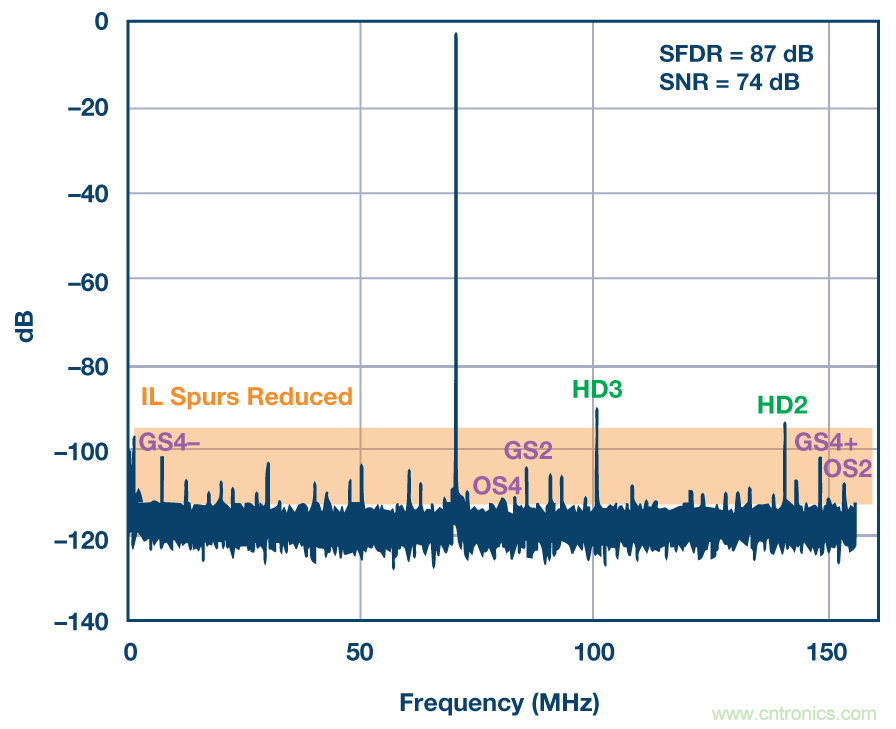

然而,如果同样的 ADC 经过前景校准以便减少通道失配,那么交错杂散功率将会大幅下降,如图7所示。与上例中的情况类似,通道谐波失真不受影响,但通过通道失配校准大幅降低了交错杂散功率。

图7. 同一个AD9652的输出频谱,采用同样的输入,但经过校准后四个通道减少了失配。与图6相比,虽然2次和3次谐波未受影响,但交错杂散的功率大幅下降,并且SFDR改善了30 dB,即从57 dBc到87 dBc。

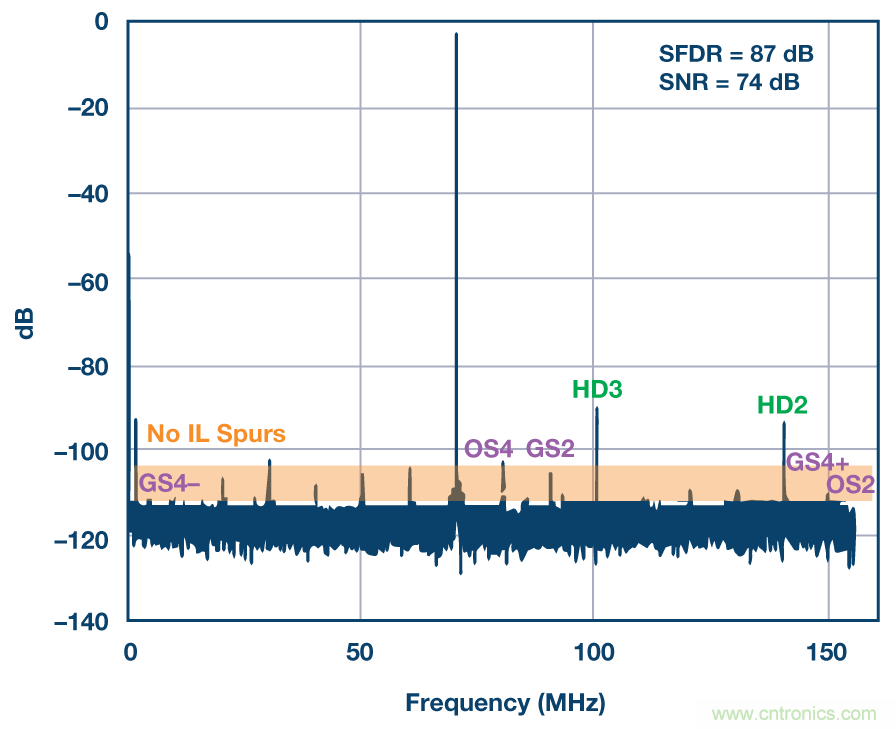

最后,图7中的频谱纯度可得到进一步改善,方法是使通道顺序随机化,如图8所示。此时,随机化使用专利技术,对四个通道的顺序进行间歇性加扰无需通过另一个(第五个)通道来达成,从而省下了与此相关的功耗。如图8所示,经过随机化之后,结果频谱中仅有常规谐波失真。

图8. 上例开启交错顺序随机化之后的输出频谱。随机化残留交错杂散可将它们的功率扩散到噪底中,相应的尖峰便消失了。可以看到的仅有常规谐波失真。SNR几乎未受影响,因为来自交错音并扩散的杂散功率经过失配校准后可以忽略。

结论

时间交错是增加数据转换器带宽的强大技术,在失配校准方面,以及通过随机化技术消除残留杂散成分方面的发展已经能够实现完全集成、极高速 12/14/16 位交错 ADC。

在输入信号受频带限制的情况下(比如很多通信应用),乒乓(双路)交错方法可通过频率规划将干扰交错杂散分配到远离目标输入频段的位置。然后便可以数字手段过滤杂散成分。虽然这种方法相比工作在 IL 采样速率一半的非交错式 ADC 获得同样的无杂散输入带宽所需的功耗要高出几乎一倍,但它不仅可以通过处理增益提高动态范围 3 dB,而且还能降低抗混叠的滚降,并修平 ADC 前的滤波器——因为 IL 采样速率高。

若需要用到 IL 转换器的全部输入频带才能捕捉宽带输入信号,那么可以采用更高次的交错转换器。这种情况下,校准和随机置乱可实现交错失真和杂散成分的补偿和消除。