LVDS分离器简化高速信号分配

与ECL、PECL和CML等高速信号分配相关的标准相比,ANSI EIA/TIA-644的低电压差分信号(LVDS)标准具有低功耗、低噪声辐射等优势。本应用笔记对比了这些通信标准的特性,并讨论了LVDS标准的优势。

引言

随着微处理器、DSP和数字ASIC时钟频率的提高,背板信号的通信速率也在不断提高。较快的时钟速率使得基于TTL的单端信号的弱点越来越突出,主要表现在:功耗增大、抖动(导致误码)、高电平辐射、传输线效应(如阻抗失配和串扰)、电源去耦难度增大以及其它一些问题。尽管一般认为利用该技术速率能够保持在50MHz以上,但是,上述问题迫使设计人员寻求更为有效的解决方案。

提高所有总线和/或背板带宽的一个方法是增加总线宽度,但采用这种方法会增大PCB布局难度,而且需要引脚数非常多的连接器,导致系统成本提高、而且非常笨重。当距离超出几个厘米时,采用串行通信方式是解决上述问题的一个有效方案。高速数据通信系统,如3G基站、路由器、加载/卸载复用器及其它设备,采用串行通信方式能够获得很大收益。

采用低压差分信号(LVDS)替代TTL信号,能够降低背板通信的误码率、串扰和辐射。

LVDS、ECL、PECL和CML的特征

LVDS在需要信号完整性、低抖动(抖动定义为信号的输出跳变时间与理想值的偏差)及较高共模特性的高速系统中得到了越来越广泛的应用。LVDS是目前用于高速串行接口的有效方案之一。

其它标准包括(由低速到高速排列):ECL (射极耦合逻辑)、PECL (正ECL)、CML (电流模式逻辑),这些标准均采用差分信号。

ECL是传统的高速逻辑标准,它基于双极型晶体差分对管,采用负偏置电源。PECL由ECL发展而来,采用正电源。新一代的ECL器件具有200ps左右的延迟时间,可应用于频率大于3GHz的系统。

在现有的接口标准中,CML的工作速率最高,可用于千兆位数据速率的系统。与其它标准相比,CML还具有一个额外的优势:集成了一个50Ω匹配电阻,大大简化了实现良好匹配的设计。但是当链路每个端点工作在不同的电源电压时,需外接耦合元件。

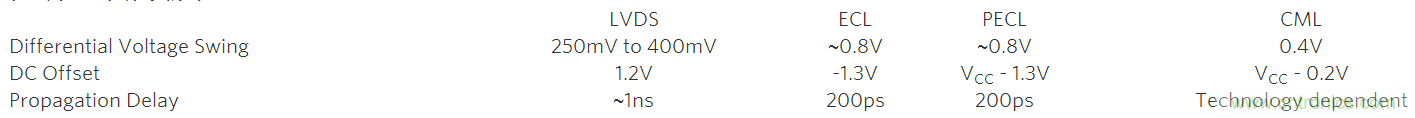

本文主要讨论LVDS的特性及其可能的应用,表1列出了LVDS的一些特性参数以及与ECL、PECL和CML系统的对比结果。按照EIA/TIA-644 LVDS和IEEE® 1596.3标准规定,LVDS采用差分信号,信号幅度范围为250mV至400mV、直流偏置1.2V。

表1. 高速通信系统的对比*

*ECL和PECL发送器输出信号的摆幅高于LVDS发送器的信号摆幅,较高的输出摆幅和较短的传输延时使得ECL和PECL器件具有更高的功耗。

LVDS的优势

LVDS的差分特性为其带来了许多优点:抑制共模噪声、理论上自身不产生噪声(假设差分信号完全对称,即正、负输出之间没有畸变)。LVDS能够用CMOS工艺实现,便于同其它电路一起集成。

由于LVDS采用差分信号,因此吸取电源电流的峰值较低,只需加适当的去耦电容即可解决电源去耦问题。通常LVDS消耗的功率低于ECL和CML,当然,在某种程度上这取决于所采用的匹配方案。

LVDS的应用

LVDS大多用于时钟分配和多个单点至单点的信号分配。时钟分配对于不同子系统需要同一参考时钟的数字系统非常重要,例如:多数情况下基站的DSP需要与射频信号处理电路同步,利用锁相环(PLL)产生所需要的本振频率,ADC被锁存到中心参考时钟。当与无线接收机一起工作时,还必须以尽可能低的辐射分配时钟(和信号),以避免对小信号通路的干扰。

把高速信号分配给不同单元时可以采用不同的策略,其中有两种极端情况:一种是将一路信号源/驱动器的信号分配给所有单元(称为多点分配器);另一种是对每一个单元采用一个独立的驱动器(称为多个单点至单点分配器)。图1说明了这两种分配架构的区别。对于多点分配器,驱动器要保证足以驱动所有的接收器和传输媒介(电缆、连接器、背板),总线通常需要在末级接收器加匹配阻抗。所有分支与总线的距离必须尽可能短,以避免引起信号完整性问题,在高密度PCB普遍应用的今天,较好地控制分支长度并非易事。

图1. 多点信号分配允许一个发送器与多个接收器之间的通信;多个单点至单点信号分配不需要中间接头,也消除了接头产生的干扰。

多个单点至单点分配结构中需要多路驱动器,可定义为点到点的操作,每路驱动器与一路本地终端接收机之间通信。这种结构减少了信号完整性问题,能够保证传输媒介的阻抗尽可能一致,消除了多条支路产生的干扰。

本文来源于Maxim。