基于FPGA的高速采样显示电路的实现

通过对被测信号的实时采样,利用等效采样原理,可以将采样率为1MHz等效为200MHz,提高了被测信号的最高频率,具有成本低,性能可靠,便易升级的特点。

项目背景及可行性分析

1.项目名称、项目的主要内容及目前的进展情况

主要内容:通过对被测信号的实时采样,利用等效采样原理,可以将采样率为1MHz等效为200MHz,提高了被测信号的最高频率,具有成本低,性能可靠,便易升级的特点。

2.项目关键技术及创新点的论述

(1)200MHz脉冲产生电路

直接产生的方波信号,电路复杂,易受外界干扰,性能指标较差,制作难度较大。我们利用晶振产生20MHz方波信号,利用FPGA内部锁相环电路将其倍频到200MHz,电路简单,可靠性高,性能指标好。

(2) 多周期测量技术

利用传统的测周期方法,测量计数误差为±1。我们利用增加被测信号周期整倍数来减少测量误差,测量误差为原来的1/10n 。

(3) 等效采样算法

首先对输入的模拟信号进行整形,在过零点处产生脉冲,利用相邻两个过零点脉冲对周期为5ns的周期序列进行计数(计数值为N),由此可产生对被测信号周期的测量,测量误差不大于5ns。利用等效采样原理,(T采样=mT信号+△t), △t=1/200MHZ=5ns, 由于最高实时采样率为信号最高频率的十分之一,应取m>=10,故等效采样周期=10*N△t+△t从而完成200mSaPS的等效速率。

3.显示技术

根据液晶显示原理,液晶屏上的每一个点对应着显示缓冲存储器的一个bit,通过一定的算法,将显示缓存的某一bit 置1,就可将被测信号显示出来。

4.控制模式选择

控制电路可采用中大规模的集成电路来构成,但结构复杂,移置性差,在此我们选择VHDL语言,通过编程,完成整个电路的控制。

项目实施方案

1.方案基本功能框图及描述

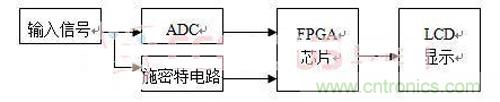

方案基本功能框图如图1所示。

图1.方案基本功能框图

将输入的模拟信号分成2路,一路经ADC输入FPGA 芯片 ,另一路经斯密特电路输入给FPGA 。FPGA外接20MHz的晶振,通过FPGA 内部的锁相环倍频至200MHz,即周期为5ns的方波信号。用此方波信号作为时间基准,对经斯密特电路输入信号的周期进行测量,得到被测信号周期=N*5ns,则等效采样的时间间隔=m*(N*5ns)+5ns。根据等效采样原理,此时的采样率相当于1/5ns=200MHz,利用LCD显示技术,可以看到此效果。

2.需要的开发平台

接口:信号输入的同轴电缆接口。

输出:FPGA开发芯片的输入输出引脚(至少10根引线)。

所需要的目标FPGA开发平台:ISE 9.0

3.方案实施过程中需要开发的模块

在本方案中需要研制模数转换模块和LCD显示接口模块。若选用初级板Spartan-3E,则无须制作模数转换模块。否则,自行开发这些模块。

4.系统最终要达到的性能指标

等效采样速率要达到200MHz。利用等效采样原理,(T采样=mT信号+△t), △t=1/200MHz=5ns, 若被测信号的最高频率为10MHz,应取m>=10,故等效采样周期=10*N△t+△t,从而完成200MSaPS的等效速率。

需要的其它资源

1.设计输入输出功能子板

(1)ADC板。将模拟信号通过8位或12位模数转换器转换成数字信号,输入信号幅度1V,最好截止频率10MHz ,采样频率为1MHz,输出数字信号高电平为3.3V。自行研发。

(2)LCD

规格: 320x240。购买成品。

稳压电源,液晶显示屏。

方针、开发工具

ISE9.0综合开发环境。