实例分析:上拉电阻取值过高或过低会发生的情况

在电路设计过程中关于上拉电阻的取值的问题要倍加注意。上拉电阻取值不准确就会导致结果也不准确。本文就上拉电阻的取值问题,以实例分析的方式为大家解析上拉电阻取值偏差可能造成的影响。

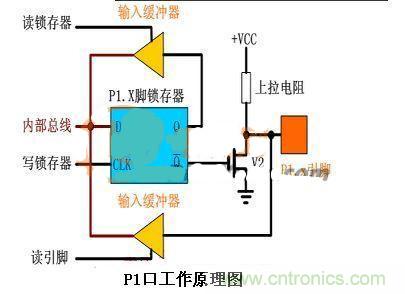

图1P1口工作原理图

如果上拉电阻值过小,Vcc灌入端口的电流(Ic)将较大,这样会导致MOS管V2(三极管)不完全导通(Ib*β,有饱和状态变成放大状态,这样端口输出的低电平值增大(i2c协议规定,端口输出低电平的最高允许值为0.4v)。

如果上拉电阻过大,加上线上的总线电容,由于RC影响,会带来上升时间的增大(下降延是芯片内的晶体管,是有源驱动,速度较快;上升延是无源的外接电阻,速度慢),而且上拉电阻过大,即引起输出阻抗的增大,当输出阻抗和负载的阻抗可以比拟的时,则输出的高电平会分压而减少。

I2C的上拉电阻可以是1.5K、2.2K、4.7K,电阻的大小对时序有一定影响,对信号的上升时间和下降时间也有影响,一般接1.5K或2.2K。

实验

接入200K上拉电阻,结果观察到信号上升时间增大,方波变成三角波。I2C上拉电阻确定有一个计算公式:

Rmin={Vdd(min)-o.4V}/3mA

Rmax=(T/0.874)*c,T=1us100KHz,T=0.3us400KHz

C是BuscapacitanceRp最大值由总线最大容限(Cbmax)决定,Rp最小值由Vio与上拉驱动电流(最大取3mA)决定;于是Rpmin=5V/3mA≈1.7K(Vio=5V)或者2.8V/3mA≈1K(Vio=2.8V)。

Rpmax的取值:100Kbps总线的负载最大容限lt;=400pF;快速模式,400Kbps总线的负载最大容限lt;=200pF,根据具体使用情况、目前的器件制造工艺、PCB的走线距离等因素以及标准的向下兼容性,设计中以快速模式为基础,即总线负载电容lt;200pF,也就是传输速度可以上到400Kbps是不成问题的。于是Rpmax可以取的范围是1.8K~7K Vio=5V对应50pF~200pF根据Rpmin与Rpmax的限制范围,一般取5.1K Vio=5V,负载容限的环境要求也容易达到。在2.8V系统中,console设计选3.3K,portable/handset等低供耗的设计选4.7K牺牲速度换取电池使用时间。

总的来说:电源电压限制了上拉电阻的最小值;负载电容(总线电容)限制了上拉电阻的最大值。

在I2c总线可以串连300欧姆电阻RS可以用于防止SDA和SCL线的高电压毛刺:I2c从设备的数量受总线电容,lt;=400pF的限制。

本文以实例的角度出发,为大家讲解了上拉电阻取值在偏大或者偏小的情况下会出现的情况,并对每种情况进行了独到的分析,希望大家在阅读过本文之后能够有所收获。