差分对PCB良好设计的关键,你需要了解的东西

一个良好设计差分对是成功进行高速数据传输的关键因素。根据应用的不同,差分对可以是一对印刷电路板 (PCB) 走线,一对双绞线或一对共用绝缘和屏蔽的并行线。在这一系列中,我将讨论差分对的特点,以及针对高速数据传输的设计问题和解决方案。

对于速度的渴求始终在增长,传输速率每隔几年就会加倍。这一趋势在诸如计算、SAS和SATA存储方面的PCIe以及云计算中的千兆以太网等很多现代通信系统中很普遍。信息革命对通过传输介质传送数据提出了巨大挑战。目前的传输介质仍然依赖于铜线,数据链路中的信号速率可以达到大于25Gbps,并且端口吞吐量可以大于100Gbps。这些串行数据传输设计使用差分信号的方式,通过被称为差分对的一对铜线来传送数据。A线路和B线路内的信号是等振幅、反相位高速脉冲。差分信号在很多电路上有使用,比如LVDS,CML和PECL等等。

传送一个理想的串行比特流

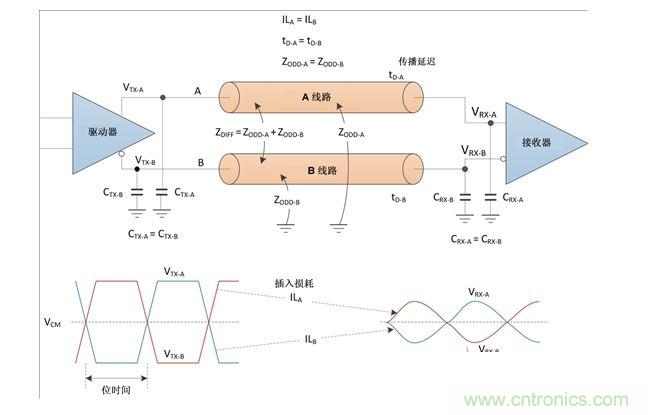

串行比特流是通过一个差分对传播的差分信号。如图1所示,差分信号的预计到达时间是一样的,这样的话,它们在接收端上保持差分信号的属性(等振幅、反相位)。一个接收器被用来恢复信号,然后正确地采样和恢复数据,从而实现无误差数据传输。

图1:理想差分对的电气属性

对于差分对的要求

一个良好设计差分对是成功进行高速数据传输的关键因素。根据应用的不同,差分对可以是一对印刷电路板 (PCB) 走线,一对双绞线或一对共用绝缘和屏蔽的并行线(通常称为Twin-axial电缆)。在这一系列中,我将讨论差分对的特点,以及针对高速数据传输的设计问题和解决方案。在这一系列的第一部分中,让我们研究一下差分对的主要要求:A线路和B线路都需要保持相当恒定和相等的特性阻抗,通常称为奇模阻抗,此时两条线路均差分激励。差分信号应该在到达目的端时保持差分信号的属性:几乎相等的振幅和相反的相位。每条线路的插入损耗应该大致相等。每条线路的传播延迟应该大致相等。总之,我们应该寻求相等并且相当恒定的奇模阻抗,从而最大限度地减少从源端到目的端整条差分对长度上的阻抗波动。我们也应当使A线路与B线路之间的延迟匹配和插入损耗匹配。此外,我们需要确保插入损耗不会太多,这样的话,接收器能够正确地恢复数据。为了满足上述要求,A线路和B线路应该在它们的物理布局布线中保持高对称。发射器和接收器也应该在它们的A和B线路电路中保持高对称,这样的话,它们在A线路和B线路上的电气负载相等。

设计差分对,以最大限度地减少失真

在理想情况下,差分对是完全对称的,此时具有无限带宽并且邻近信号之间完全隔离。在现实情况下,差分信号通过集成电路 (IC) 封装、外部器件、不同的PCB结构、连接器和电缆连接子系统进行传播。实现完全对称的差分对是件不太容易的事情。在以后的博文中,我将讨论差分对设计的方案,以及最大限度减少发射信号失真的技术。德州仪器 (TI) 拥有完整的高速信号调理IC产品线,诸如重定时器(Retimer)和驱动器(Redriver)。它们在解决所有类型实际差分对设计时碰到的不理想情况,和高插入损耗情况大有帮助,从而在现代系统中实现了可靠数据通信并延长了传输距离。