专家授课:新一代宽带宽功率放大器设计

本文介绍了两种不同的放大器平台,即全集成式MMIC和混合封装式放大器,两者均可在30 ~2700MHz范围内实现领先的性能。其实现方法是在MMIC上运用行波技术,在混合式设计中,则是运用桥接T拓扑结构使晶体管匹配至50Ω。两种技术各有优点,在性能和成本方面各有折衷。

功率放大器是构建新一代通信系统的核心组件,这类通信系统需要超宽的带宽以支持高数据速率。为了设计一款高效的功率放大器,晶体管必须工作于开关模式之下,并且/或者具有反射端接谐波。然而,为了能在一个以上倍频程带宽下正常工作,在较低频率下,谐波端应在带内。此外,Bode-Fano带宽理论认为,对于给定的复合负载,可实现带宽存在一个基本限值,该限值会降低目标负载阻抗,进一步偏离高效条件。在本文中,我们将比较和对比两种不同的宽带高效功率放大器设计技术。一种设计采用一种非均匀分布式放大器拓扑结构,完全集成于一个MMIC之中,其输入和输出匹配至50 Ω。另一种设计采用混合式设计技术,在封装中集成了桥接-T输入匹配MMIC。本文将首先简要描述电路制造工艺,然后逐一展示和讨论各种设计拓扑结构。

器件技术和工艺

这里使用的AlGaN/GaN HEMT器件基于TriQuint的0.25 μmGaN工艺TQGaN25,采用100mm SiC晶圆制成。这是一种TriQuint推出的大规模制造技术。在PAE匹配条件下,一个四指100μm栅极宽度晶体管(偏置电压:Vd=40V,Id=100 mA/mm)的典型功率密度为5.5W/mm,10GHz时的PAE为60%。

分布式放大器设计A.

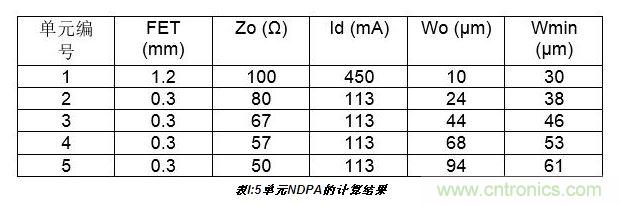

电路设计为了实现最高的功率和效率,我们选择了非均匀分布式功率放大器(NDPA)拓扑结构。NDPA不是以50Ω的阻抗端接漏极线路,而是采用了渐变传输线。为每条传输线路选择特定的宽度,以便为每个单元提供最佳负载。在某些情况下,各个单元的器件尺寸也采用渐变设计。由于目标工作频率为30MHz至2.7GHz,所以,我们选择了5-单元设计,器件总周长为2.4mm,以实现功率、增益、带宽和芯片尺寸的平衡。随后,我们计算出了各单元的器件尺寸和传输线路阻抗。结果如表1所示。第一个单元的尺寸为1.2mm,其目的是实现功率和效率的最大化。其余单元尺寸相等,均为0.3mm。请注意,在表1中,有一列为各个单元的漏电流(Id)。该电流表示器件的最大驱动电流,设定了输出走线的最小宽度。

图1:10W高效分布式放大器MMIC示意图。芯片的总尺寸2.4 mm×1.8mm。MMIC成品如图1所示。芯片的最终尺寸为2.4mm×1.8mm。为了支持最低30MHz的工作频率,我们选择了片外偏置选项。这种设计的一个特点是在第一单元输出端使用了线圈。请参考前面的表1,处理450mA电流所需的最小宽度为30μm。然而,在100μm厚的SiC基板上,宽30μm线路的典型阻抗只有76Ω,离最佳负载100Ω还有很大的差距。然而,线圈实际上会通过互耦合的方式增大线路的有效阻抗,仿真条件下,该线路的阻抗为105Ω。这样就可以实现高效运行。

B. MMIC测量值

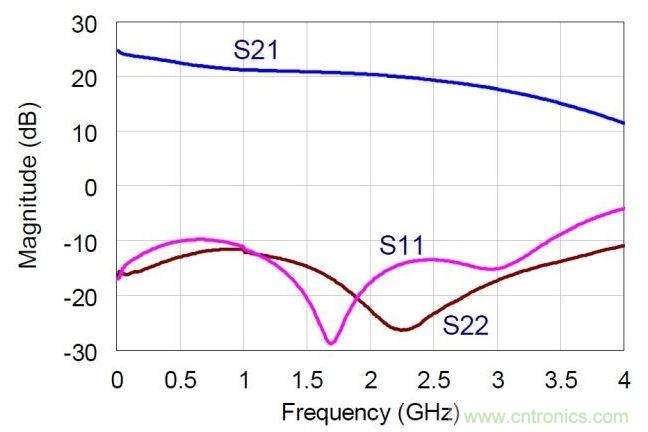

我们把MMIC成品焊接在一块厚40密耳的CuMo承板上,同时把RO4003板装在MMIC周围,以便进行评估。我们对电路板上的50?走线进行了去嵌入处理,使测量参考平面位于焊线的末端。如图2所示,在30MHz至2.7GHz范围内,典型增益为20dB,并且在相同频率范围内,输入和输出回波损耗为10dB或更低。

图2:NDPA的实测小信号S参数值。MMIC在偏置于30V,360mA。

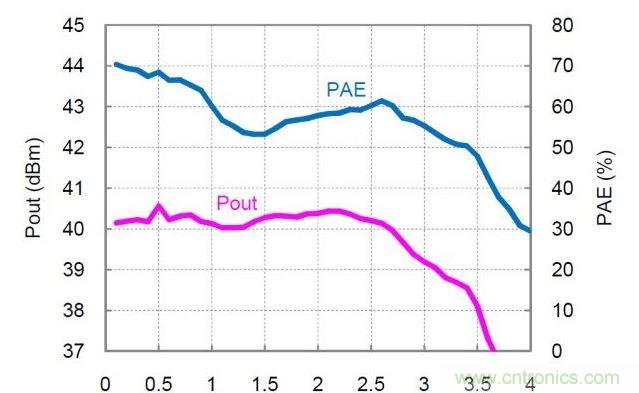

图3:分布式放大器的实测Pout和PAE值。放大器以27dBm的恒定输入功率驱动,偏置电压Vd=30V,偏置电流Idq=360mA。大信号测量值表明,结果良好。图3所示为MMIC在整个频率范围内,在27dBm的恒定输入功率(这相当于约5dB的压缩值)下的输出功率和PAE。当漏极电压为30V时,MMIC在不超过2.5GHz的整个频率范围内可产生大于10W的输出功率,在不超过2.7GHz的范围内,可产生8W或以上的输出功率(功率密度超过4 W/mm),并且在整个频段,PAE均优于52%。在500MHz以下,MMIC可实现近70%的PAE。如此高的PAE源于第一个单元加载了高阻抗。请注意,这里展示的功率和PAE测量值只是在基频输出功率条件下得到的结果,不得用于计算功耗。要计算功耗,我们必须使用总功率,包括谐波下的所有功率。

电路设计

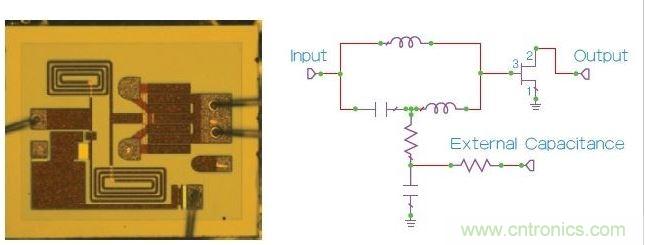

我们前面展示的分布式放大器技术对MMIC效果明显。然而,对于混合分立式设计来说,要实现多级是十分困难的。我们选择采用一种桥接T拓扑结构,将单个晶体管的输入端匹配至50Ω。我们选择了合适的晶体管的尺寸,以便输出端的50Ω端口与其目标负载线完好匹配,因此,放大器输出端可以不匹配。我们选择了一款周长为1.24mm的晶体管。另外,借助周长为2.48mm的晶体管也可实现不错的负载线,其一般具有更高的效率和更低的功率密度。要进一步优化性能,可以在电路板级进行更多匹配。MMIC成品如图4所示。芯片的最终尺寸为1.277mm ×1.06mm。用周长为2.48mm的晶体管(本文中未讨论)打造的另一款芯片的尺寸为1.277mm ×1.305mm(大23%)。

图4:用于混合分立式功率放大器解决方案的MMIC成品图(左)和原理图(右)。桥接T拓扑结构是Zobel网络的修改版,可以在输入端提供恒定阻抗。用于匹配晶体管输入端的拓扑结构如图4所示。该电路的匹配设计可在30MHz至2700MHz范围内提供良好的回波损耗性能。桥接T匹配的不足之处在于,网络损耗较大。然而,在这些低频下,晶体管拥有较大的增益,可以平衡掉这些损耗,从而使芯片在各种频率下均能无条件保持稳定。因此,对于该工作频率,桥接T是一种非常合适的选择,不会影响性能。桥接T网络的低频性能在很大程度上取决于并联网络中的阻抗。为了在低频下实现实部阻抗,需要使用一个较大的电容。为此,我们用一个焊盘连接一个片外电容(见图4中的外部电容)。由于MMIC的输入端已匹配至50 Ω,因此,输入网络不需要进行其他匹配。此外,器件在尺寸设计上已在输出端提供近50 Ω的负载线,因此,输出匹配网络只需要一个串联L并联C网络以保障高频性能,然后,在低频下提供50Ω的负载阻抗以保障宽带性能。输入和输出匹配网络都采用了宽带偏置网络,并部署在一块4”×3”的应用板上。

混合式放大器的测量值

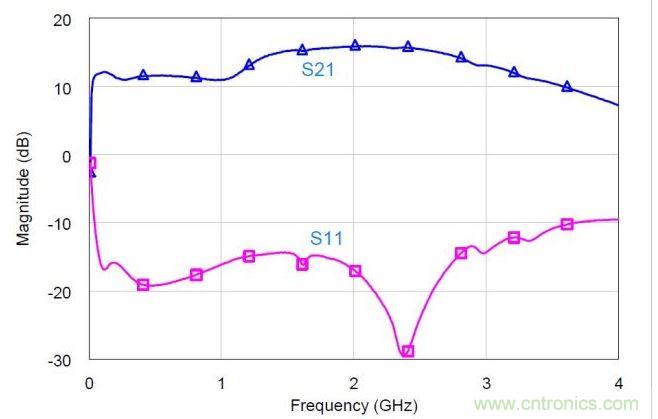

我们在一块用Rogers 4350B制成的电路板上对最终器件进行了测试。50Ω匹配输入表现良好,能在40MHz至2.7GHz的范围内实现10dB的回波损耗,在低至30MHz的频率范围内实现7dB的回波损耗(图5)。器件在低频下实现12dB的增益,在高频下实现17dB的增益。在32V和脉冲条件下,放大器实现了5W的典型输出功率(或者,4W/mm的功率密度),在1至2.7GHz范围内实现45%的功率附加效率(图6)。我们选择了脉冲而非CW工作模式,因为评估板限制了总功耗。另外,我们在1至2.7GHz范围内对数据进行了测量,因为我们无法在1GHz以下构建脉冲试验台。

讨论

结果表明,两款放大器均能在30~2700 MHz范围内工作,二者具有相似的输出功率密度。完全匹配的MMIC在器件尺寸以及输出功率的选择方面表现出较大的灵活性,但其代价也比较大。另一方面,我们展示的混合式解决方案具有较为独特,器件尺寸固定,因此对性能形成了限制;较小或大得多的晶体管都无法在整个带宽范围内取得良好效果。但是,由于芯片尺寸非常小(为MMIC的1/4,但功率仅少一半),因此其代价更能令人接受。另外,最多可以使用两倍周长的晶体管,可实现类似MMIC的性能,芯片尺寸增幅也不大(23%),并且混合式解决方案可使用外部元件进行调整,以在特定频段范围内实现更加优化的性能。然而,MMIC解决方案由于要处理的寄生电容较少,所以可以实现卓越的性能。归根结底,如果系统侧重于打造一种低成本的解决方案,并且可以牺牲一定的性能,则混合式解决方案是更合适的选择。然而,如果系统要求以较高的代价提供特定的性能,则MMIC解决方案是更好的选择。尽管如此,实践表明,两种设计技术都是宽带条件下的有效选择。

图5:混合MMIC分立式功率放大器的小信号S参数实测值。