功能安全要求:使用FPGA实现ADAS设计

ADAS是一项为确保道路安全而设计的创新技术。这项系统性能对未来的标准商用货架发起了挑战,而FPGA则可以助力ADAS的设计。本文主要解析的是使用FPGA实现ADAS设计的功能安全要求。

基于雷达和摄像机的应用现在也被用于安全驾驶领域。最初,自适应巡航控制和道路偏离报警等这些高级辅助驾驶系统(ADAS)只是一些非常便利的特性。而现在,它们在车辆控制上扮演了更积极主动的角色,支持实现道路辅助保持(LKA)等功能。以前的高性能CPU被认为是最适合这些应用的器件,但是综合考虑计算性能和低功耗之后,促使工程师转而采用FPGA器件。

ADAS需要满足特殊的功能安全要求。2011年,载重3.5吨以下客车的ISO26262标准发布,其目的是降低系统出现故障后造成危险状态的风险。这一标准要求采用严密的设计过程,在应用执行过程中探测随机硬件故障,以减少系统性故障。

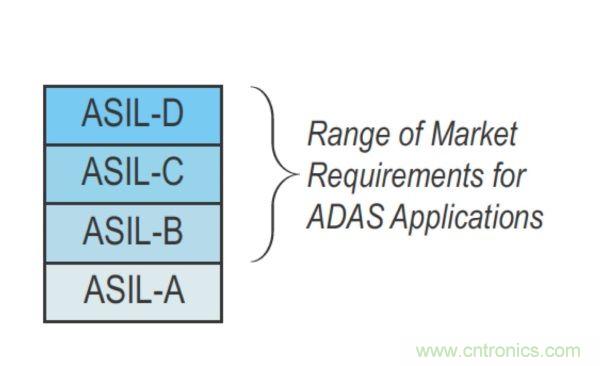

应用开发人员定义了专门的安全目标,针对每一目标分配了相应的汽车安全完整性等级(ASIL)。对于应用中最高级别的ASIL,通常定义了每一组件从开发直至工作到寿命终了时应满足的要求。图1显示了从客户需求角度看,ADAS应符合的ASIL目前的范围。

图1.ADAS ASIL市场需求(注:Range of Market Requirements for ADAS Applicatios:针对ADAS应用的市场要求范围)

ASIL-B是市场上的最低级别,而某些应用则要求采用ASIL-D以支持某些功能。越来越多的ASIL有更严格的要求。在某些具体实现中,组件的通用ASIL或者条目(系统)等级都会带来不必要的复杂度,影响了开发成本和进度。分析系统概念,得出安全概念和要求后,还可以把应用分成几种不同的步骤,这就具有不同的ASIL,更容易实现,而且实现的效率更高。

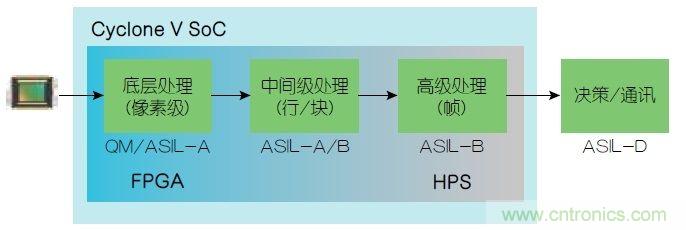

例如,前端摄像机应用使用了ADAS中常见的一个图像传感器。图2显示了系统的高级结构图。

图2.高级单前端摄像机ADAS

一个图像传感器连接至图像处理器,例如可以是Altera Cyclone V SoC。信号处理链和数据流被分成四个部分。首先,通过把图像变换成更实用的表现形式,在像素级上进行底层处理。然后,对行图像或者块图像进行中间级处理,使用相应的算法,提取出边沿等特征。下一步,进行高级处理,提取出每一帧的数据,探测目标并分类。然后,系统会跟踪目标,如果需要采取措施,则与刹车或者转向电子控制单元(ECU)进行通信。

在FPGA上,底层和中间级处理能被非常高效地实现,但是,用户也可以在Cyclone V SoC硬核处理器系统(HPS)的Cortex-A9处理器等CPU上实现某些中间级处理。高级处理主要是控制代码,可以映射到HPS中的一个或者两个Cortex-A9上。处理链的最后一步是目标跟踪和决策,可以在外部微控制器上完成这一步。

在整个处理过程中,每一步将输入数据进行简化得到更有意义的数据,数据减少意味着提高了安全临界。因此,底层实现可以分成质量管理(QM)或者底层ASIL (例如,ASIL-A)。原因是一个像素期间出现的故障对后续算法性能的影响很小,可以忽略。在这个例子中,假设中间级处理符合ASIL-A或者ASIL-B,识别目标并进行分类的高级处理功能应符合ASIL-B。对目标进行分类后,生成目标表,将之提供给微控制器,进行目标跟踪和决策。这是信号链最关键的部分,Altera认为它应该符合ASIL-D,这对汽车的行为有直接影响。

在这类应用中,最好对数据流进行更全面的分析,每一级的安全临界定义对整个系统的性能会产生直接影响。对前面计算级有太高的安全要求会导致难以满足系统性能目标,而且对系统整体安全的影响很小。但是,处理链底层也会出现故障,对系统安全功能产生较大的影响。例如,底层处理功能的永久故障会导致高层数据永久损害,但是,合理性检查很容易探测到这类故障,对系统性能的影响相对较小。

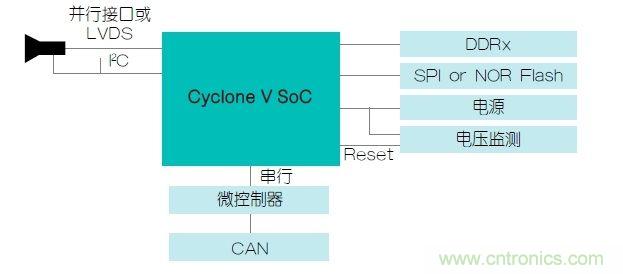

图3.单前端摄像机系统实例

图3显示了单前端摄像机系统实例的高级结构图。由一个外部电源管理电路为Cyclone V SoC提供电源。当供电电压不在额定工作范围内时,单独的电压监控功能会产生复位。外部非易失存储器连接至四路串行外设(quad SPI)模组,系统启动过程中装入应用程序,配置FPGA时会使用这些模组。执行应用程序代码,存储数据和图像帧时,Altera使用DDR存储器。通过SPI连接外部微控制器,进行目标探测和最终决策,通过CAN接口与汽车底盘的其他部分进行通信。

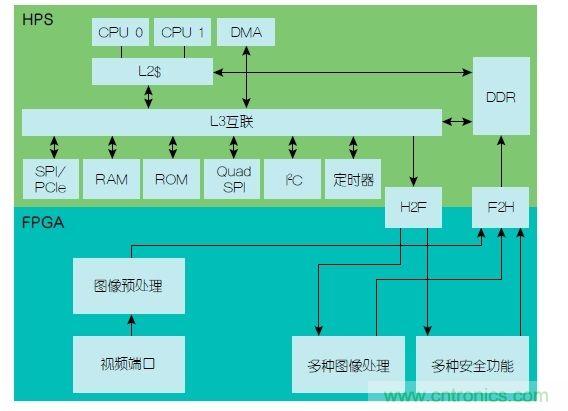

图4.Cyclone V SoC模组视图

应用中所使用的图像处理器模组如图4所示。视频端口接收来自图像传感器的数据,将其传送至图像预处理模块。这一模块展示了底层图像处理。在这个例子中,数据通过图像预处理模块后,通过FPGA至HPS (F2H)桥接被写入到DDR存储器中,也可以传送至下一级,实现的效率更高。第二级是中间级处理,由各种图像处理模块来完成。通过HPS至FPGA (H2F)桥接读出以前存储在DDR存储器中的数据,再次将其写入到DDR存储器中。在这个例子中,由HPS完成高级处理。

现在,让我们了解一下用于探测设计中不同区域是否有故障的诊断功能。文中所讨论的一些诊断功能能够探测到永久故障,而有的只能探测到瞬时故障,也有的能够探测各种故障。瞬时故障是一种出现后又消失的故障。对于这一分析,Altera应考虑实现某些功能时存储器中出现的故障,以及实现功能时逻辑中可能出现的故障。

在应用软件使用图像传感器之前,应对其进行配置,在应用程序执行过程中不断修改配置以适应不同的光照条件。图像传感器对于应用操作非常关键,因此,建议在容错时间间隔(FTTI)期间对其配置至少进行一次检查。这并不一定能够覆盖传感器的所有可能的故障,但是,可以管理好配置寄存器组。

汽车中使用的某些传感器支持用户在每一图像帧的辅助扫描线中传送某些配置寄存器数据。通过这一功能,用户可以检查每一帧的传感器设置,不需要通过I2C接口来读取寄存器。传送帧数据时就可以在FPGA中实现这种检查,而不需要在CPU上花费财力。

通过底层图像处理时,一个像素的变化不太可能对实际应用的行为产生很大的影响,因此,在很多情况下,可以忽略这类故障。但是,会导致帧丢失或者整个帧被损坏的故障是必须被检查到的。

大部分图像传感器含有传送定义好的测试帧的功能,不需要传送正常的图像数据。定义好输入数据后,也就定义了图像处理模块的输出数据。然后进行后续测试。例如,通过对输出数据进行循环冗余校验(CRC),找到系统中出现的任何永久故障。这种测试覆盖了整个数据通路中的永久故障。

另外,还应该探测到FPGA中一个模块向另一个模块传输数据时数据的变化。前面提到的测试码型或者测试帧方法涵盖了大部分永久故障,但是,探测不到瞬时故障。而各种传输或者信息冗余技术能够探测到这类故障。

中间层图像处理实现了边沿或者角探测算法,还可以应用特征提取算法。因此,只查看图像中关注的特征,减少了生成数据。数据减少后,由于故障会导致后续处理步骤中丢失目标,因此,丢失特征的风险增大了。

高级图像处理阶段包括目标探测和目标分类。从软件术语的角度来讲,这一级主要是控制代码,因此,非常适合在CPU上运行。HPS采用了几种硬件功能(例如,ECC、MMU、看门狗),在HPS中进行故障诊断。

功能安全重要的另一面是确保减少系统性故障。这通过使用可靠的开发过程和工具来实现。ISO26262标准详细规定了功能安全的管理要求,例如,对安全生命周期和支持过程中不同的行为进行一致性测量,类似配置和修改管理。如果所使用的工具有可能造成应用故障,那么就应该分析这些工具,进行测量以减小故障发生的概率。

ADAS是确保越来越拥挤的道路更加安全的下一波创新。这些系统的性能需求给现有以及未来的标准商用货架(COTS)产品带来了挑战,而可编程FPGA在这方面有很大的优势。实现专用诊断能够扩大系统的诊断覆盖。很多COTS产品在设计时并没有体现功能安全,而通过使用具有功能安全的平台和开发环境,与擅长功能安全的合作伙伴合作,这些都有利于系统的整体实现。