电路技术详解:SDRAM电路设计

什么是SDRAM,SDRAM电路的设计原理是什么?在了解SDRAM电路设计时应先从哪里开始入手呢?本文将从这几个方面详细深度的为大家讲解SDRAM电路设计。

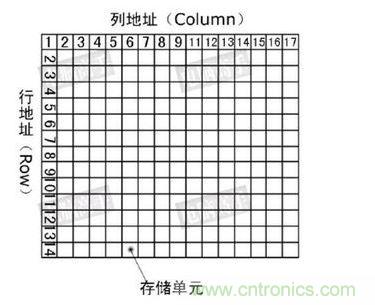

介绍SDRAM电路设计之前先了解下SDRAM的寻址原理。SDRAM内部是一个存储阵列,可以把它想象成一个表格,和表格的检索原理一样,先指定行,再指定列,就可以准确找到所需要的存储单元,这是内存芯片寻址的基本原理,这个表格称为逻辑Bank。由于技术、成本等原因,不可能只做一个全容量的Bank,而且由于SDRAM工作原理限制,单一的Bank会造成非常严重的寻址冲突,大幅降低内存效率,所以在SDRAM内部分割成多个Bank,目前的SDRAM基本都是4个Bank。存储阵列示意如图1所示:

图1 SDRAM存储阵列示意图

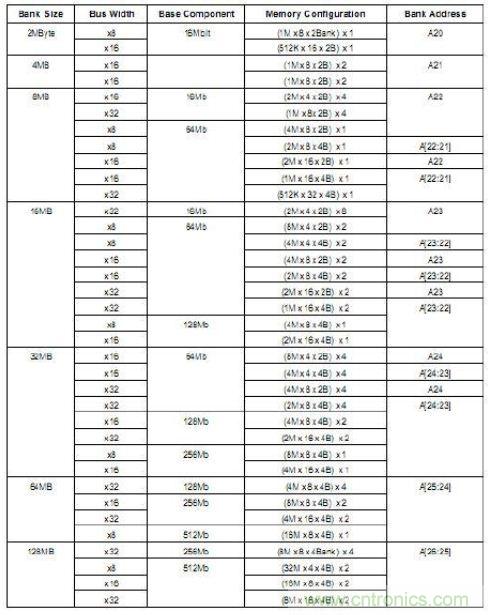

图2 SDRAM引脚配置方案图2是S3C2440A手册提供的SDRAM bank地址的配置方案,维护系统使用的SDRAM是HY57V561620FTP-H,它的规格是4*4M*16bit(使用两片是为了配置成32位的总线宽度),BANK大小是4M*16=64MB,总线宽度是32位,器件大小是4*BANK大小=256Mb,寄存器配置就是(4M*16*4B)*2,根据图2可知,SDRAM上的BANK地址引脚(BA[1:0])与S3C2440的A[25:24]相连。

图2 SDRAM引脚配置方案图2是S3C2440A手册提供的SDRAM bank地址的配置方案,维护系统使用的SDRAM是HY57V561620FTP-H,它的规格是4*4M*16bit(使用两片是为了配置成32位的总线宽度),BANK大小是4M*16=64MB,总线宽度是32位,器件大小是4*BANK大小=256Mb,寄存器配置就是(4M*16*4B)*2,根据图2可知,SDRAM上的BANK地址引脚(BA[1:0])与S3C2440的A[25:24]相连。

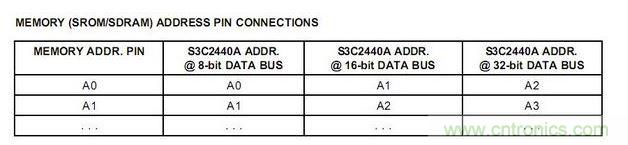

图3 S3C2440A控制地址总线连接图3是寄存器控制地址总线连接方式,我们使用2片SDRAM配置成32位的总线宽度,所以SDRAM上的A[12:0]接到S3C2440的A[14:2]引脚。具体的SDRAM电路连接如图4所示:

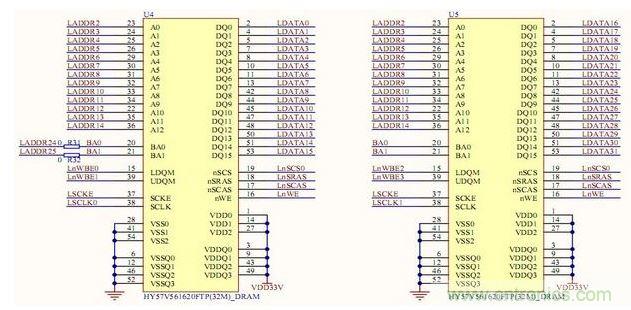

图4 SDRAM电路连接图SDRAM的地址引脚是复用的,在读写SDRAM存储单元时,操作过程是将读写地址分两次输入到芯片中,每一次由同一组地址线送入,两次送入到芯片上去的地址分别称为行地址和列地址,它们被锁存到芯片内部的行地址锁存器和列地址锁存器。下面是该芯片的部分信号说明:nSRAS:SDRAM行地址选通信号nSCAS:SDRAM列地址选通信号nSCS:SDRAM芯片选择信号(选用Bank6作为sdram空间,也可以选择Bank7)nWBE[3:0]:SDRAM数据屏蔽信号SCLK0[1]:SDRAM时钟信号SCKE:SDRAM时钟允许信号LDATA[0:31]:32位数据信号LADDR[2:14]:行列地址线LADDR[25:24]:bank选择线