MOS管如何发力,使反激电源达到90%效率

品慧电子讯:本文由资深电源发烧友总结的经验,主要目的为了帮助大家更加深入了解并学习反激电源的设计。要想攻破90%效率反激电源,必须掌握MOS管的相关知识,才能无往不利。

说是有关MOS管的相关知识,其实是将肖特基、变压器等知识围绕MOS展开,对反激电源的整体设计进行完善。

频率高低的第二个影响是整个电源板开关的次数,这个开关次数直接影响到:

1、mos,肖特基的开关损耗。

2、因变压器的寄生参数影响回路特性。

3、因开关次数增加,增加了产生谐波的次数,影响EMC。

针对以上三点,下面来进行较为详细的说明。

有关mos的损耗,开关损耗自是不必多说,下降上升导通时的各种损耗总和,驱动也就是环路电感,极性电容,驱动电阻,驱动峰值电流等相关问题,电流不大就不复杂,电流大了就要做保护,阶段性关断,管压降检测等就复杂了。

下面说说MOS环路当中的损耗问题。

在做电源的时候,变大Rg电阻,有时候效率反而提升,这就是一种mos开关的环路特性。引起这种环路开关特性的原因,主要是由变压器寄生电容和肖特基的寄生电容。导线之间有电压差,就会存在电容特性,对变压器做模型,寄生电容大类别是4种:

1、初级的匝间电容和层间电容

2、次级的匝间电容和层间电容

3、初级和次级之间的匝电容

4、线圈和磁芯的电容(这个一般忽略不计)

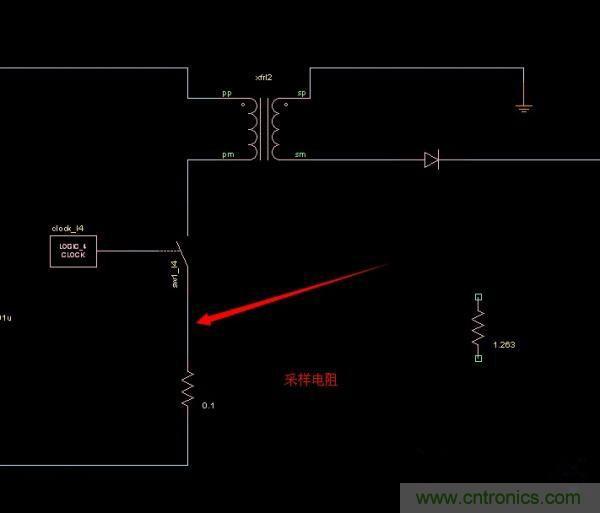

肖特基就是规格书上写的电容。而正是因为上面的寄生电容,引起了mos开关的回路特性,有时候加大RG电阻可以得到更高的效率,更好的温升。反激式在mos都有一个采样电阻到cs引脚,现在就从这里的波形来看关于寄生参数。

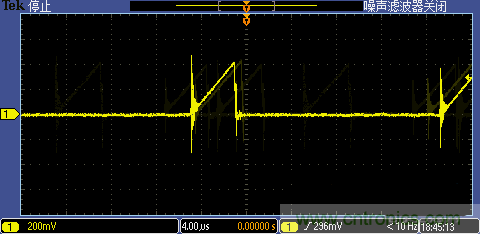

图1

图1

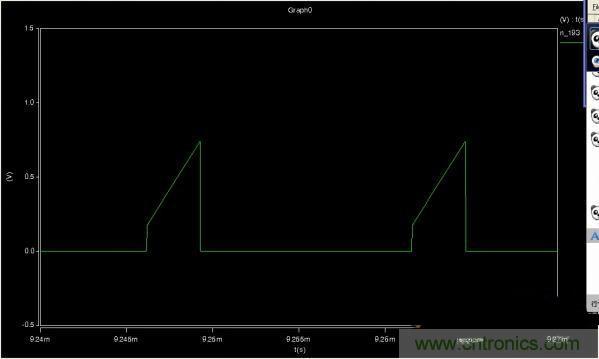

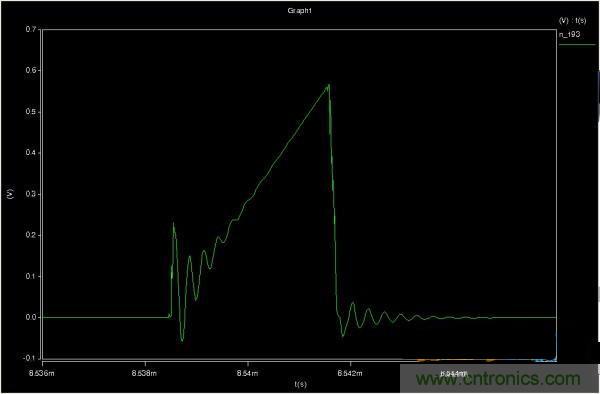

图2

图2

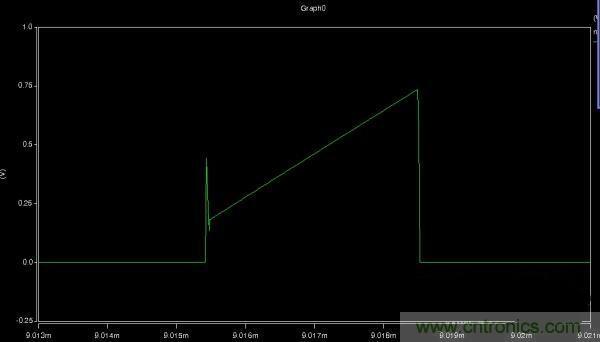

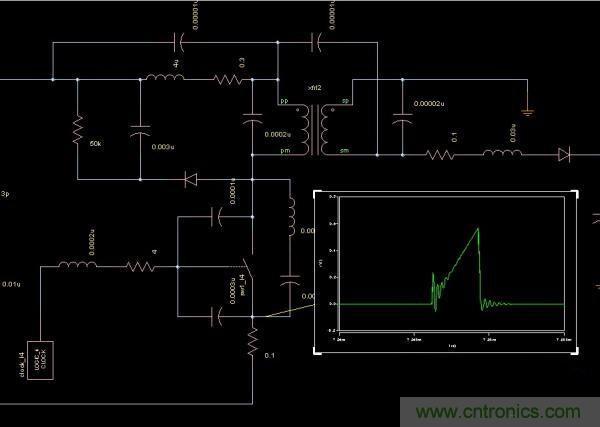

图3

图3然后加入变压器次级寄生电感,电路波形则变为:

图4<上一页1234下一页>

图4<上一页1234下一页> - 第一页:MOS管如何发力,使反激电源达到90%效率(1);

- 第二页:MOS管如何发力,使反激电源达到90%效率(2);

- 第三页:MOS管如何发力,使反激电源达到90%效率(3);

- 第四页:MOS管如何发力,使反激电源达到90%效率(4)

从这里可以看出:

次级的漏感会和肖特基二极管的寄生电容构成一个阻尼震荡,一个低漏感的变压器可以更好的克制这个阻尼震荡,提升电阻的谐波能力,这个震荡也会影响二极管两侧的尖峰电压。

下面是一个实际电源在采样电阻上的波形:

图5

图5仿真出来反激式电源的波形:

图6

图6仿真和实际有一些差距,但这个仿真已经能解决前面的问题,有时候加大RG电阻效率反而升高,也就是功率回路问题。

下面再来看仿真图:

图7<上一页1234下一页>

图7<上一页1234下一页> - 第一页:MOS管如何发力,使反激电源达到90%效率(1);

- 第二页:MOS管如何发力,使反激电源达到90%效率(2);

- 第三页:MOS管如何发力,使反激电源达到90%效率(3);

- 第四页:MOS管如何发力,使反激电源达到90%效率(4)

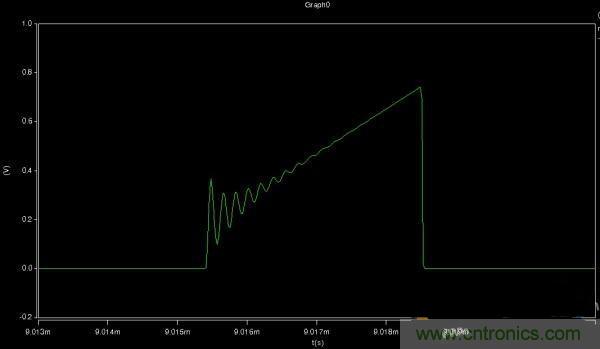

接下来调整MOS的开关速度来看对整个寄生参数的影响。上面仿真出来的用的是100ns的开关速度,现在修改为300ns,RG电阻改为12欧,在来看一下波形。

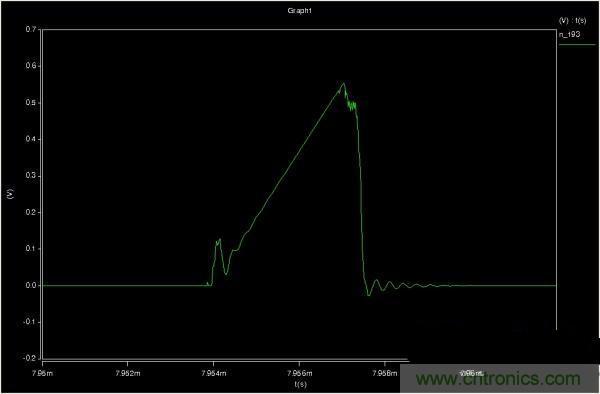

图8

图8从上面给出的图可以说明:

1、肖特基寄生电容和变压器次级寄生电容会和次级漏感形成一个阻尼震荡;

2、变压器初级漏感会和初级寄生电容形成一个阻尼震荡;

3、变压器初级漏感会和mos的DS极间电容形成一个震荡;

以上是主要部分,忽略线路板和元器件引脚的寄生电感。

这样一来,变压器次级的寄生电容也可以折射到初级,在一定电容情况下,mos开关的上升沿和下降沿越陡峭,则经过寄生电容的尖峰电流越大,就越大的冲击电流承受到mos上,引起一种功率损耗。

当mos开关速度越快,电路形成的谐波震荡就越严重,然后引起EMC问题。所以,mos开关的速度在实际电路中不是越快越好,个人认为,当变压器器件工艺已经符合要求的情况下,调整MOS管的RG电阻,找出改变这个电阻最高效率点,确定mos的RG电阻阻值。

本篇文章主要围绕MOS,对反激电源当中的变压器肖特基等知识进行了较为全面的讲解。希望大家在阅读过这些文章之后能够对90%效率的反激电源制作有进一步的了解和认识,小编将为大家带来更多精品的文章,欢迎大家持续关注。