如果FPGA设计中出现时序违规,要怎么办?

前面小编为大家讲到《时序约束的一些经验》,这一节中将谈论添加约束后进行综合,如果出现时序违规,会是哪类情况以及该如何去解决。想学习这方面知识的童鞋可千万别错过,不然后悔别找我!!《时序约束的一些经验》http://www.cntronics.com/gptech-art/80025429

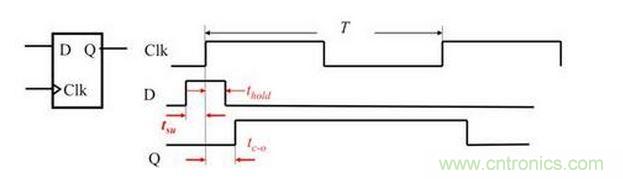

通常来讲,一项芯片或者FPGA项目工程走到综合这一步说是到了尾声,其实恰恰才是刚刚开始,后面还有很多很多的流程和路要走,所以解决时序违规问题十分重要,如果这个问题解决不好,后面的流程就没法往下走,整个项目可能停滞不前,甚至打回到最开始重新进行coding,如果在不幸运的话有可能整个项目就会fail,所以时序分析及解决违规问题则是必须攻克的一个难题。 其实所有的时序问题都可以归结为常见的两类问题:建立时间(setup time)和保持时间(hold time)的问题,关于他们的定义大家可以百度一下。1)一般呢,建立时间不满足往往是由于组合逻辑团太大的原因造成的;保持时间不满足往往是由于组合逻辑团太小的原因造成的;建立时间和保持时间都不满足的情况往往是出现在异步时钟域中。2)解决建立时间不满足的方法有如下:加强约束,重新进行综合,对违规的路劲进行进一步的优化,但是一般效果可能不是很明显;降低时钟的频率或者提高电路的电压,但是这个一般是在项目最初的时候决定的,这个时候很难再改变;拆分组合逻辑团插入寄存器,增加流水线,这个是常用的方法;尽量减小传输的延时;换用先进的工艺,但是这个一般也不太现实。所以流水线是常用的方法。3)解决保持时间不满足的方法有如下:增加逻辑团的延时,一般就是在后端的时候插入buffer;减小时钟的延时。相比建立时间,保持时间的问题一般比较好解决。4)异步时钟域的问题:这个一般要单独依靠异步时钟域(CDC)处理的方法来解决。所以整体而言,处理时钟问题其实就是在处理建立时间,保持时间,异步时钟等相关的问题,把这些解决好,后面才能顺利的进行。在后续中,会更为详细的,图文并茂的介绍如何处理建立时间和保持时间的方法,如何处理CDC的问题。希望大家耐心等待!

其实所有的时序问题都可以归结为常见的两类问题:建立时间(setup time)和保持时间(hold time)的问题,关于他们的定义大家可以百度一下。1)一般呢,建立时间不满足往往是由于组合逻辑团太大的原因造成的;保持时间不满足往往是由于组合逻辑团太小的原因造成的;建立时间和保持时间都不满足的情况往往是出现在异步时钟域中。2)解决建立时间不满足的方法有如下:加强约束,重新进行综合,对违规的路劲进行进一步的优化,但是一般效果可能不是很明显;降低时钟的频率或者提高电路的电压,但是这个一般是在项目最初的时候决定的,这个时候很难再改变;拆分组合逻辑团插入寄存器,增加流水线,这个是常用的方法;尽量减小传输的延时;换用先进的工艺,但是这个一般也不太现实。所以流水线是常用的方法。3)解决保持时间不满足的方法有如下:增加逻辑团的延时,一般就是在后端的时候插入buffer;减小时钟的延时。相比建立时间,保持时间的问题一般比较好解决。4)异步时钟域的问题:这个一般要单独依靠异步时钟域(CDC)处理的方法来解决。所以整体而言,处理时钟问题其实就是在处理建立时间,保持时间,异步时钟等相关的问题,把这些解决好,后面才能顺利的进行。在后续中,会更为详细的,图文并茂的介绍如何处理建立时间和保持时间的方法,如何处理CDC的问题。希望大家耐心等待!