【锦囊三】PCB设计中关于反射的那些事儿

品慧电子讯前面小编为大家带来了PCB设计中反射的两点:信号完整性及集总的世界,这里小编将继续为大家介绍PCB设计中关于反射的相关问题知识!这里主要带来的是PCB设计中反射中路的反射和场的反射的相关知识分析!【锦囊二】PCB设计中关于反射的那些事儿http://www.cntronics.com/rf-art/80025018【锦囊一】PCB设计中关于反射的那些事儿!http://www.cntronics.com/rf-art/80024959

接下来小编还会继续为大家奉献上该专家基于PCB设计中关于反射的其他相关知识,希望大家耐心等待!

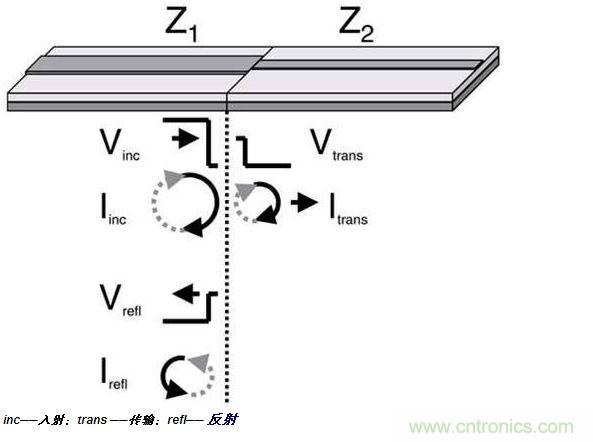

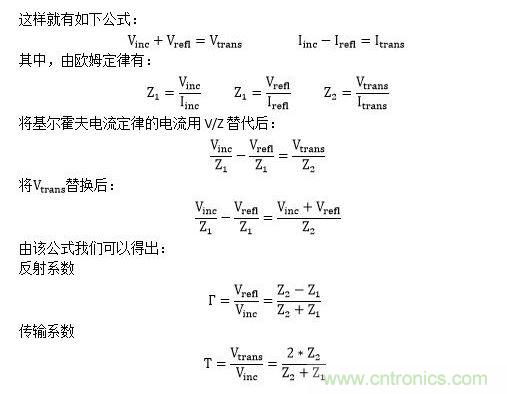

当信号穿越阻抗不连续的点时,会产生反射电压与电流,从而使得分界面两边的电压和电流相等(基尔霍夫定律)。

当信号穿越阻抗不连续的点时,会产生反射电压与电流,从而使得分界面两边的电压和电流相等(基尔霍夫定律)。 12345下一页>

12345下一页> - 第一页:PCB设计中关于反射的那些事儿

- 第二页:PCB设计学习中的笔记分享

- 第三页:PCB设计中关于场的反射

- 第四页:PCB设计中场的反射不同频率谐波分析(1)

- 第五页:PCB设计中场的反射不同频率谐波分析(2)

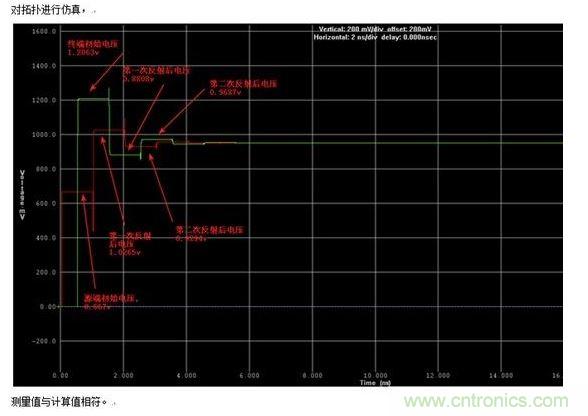

在这里给大家自爆一下高速先生小时候学习过程中做过的笔记:

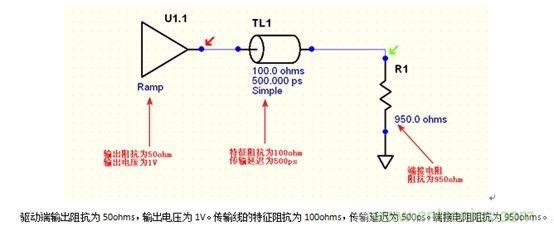

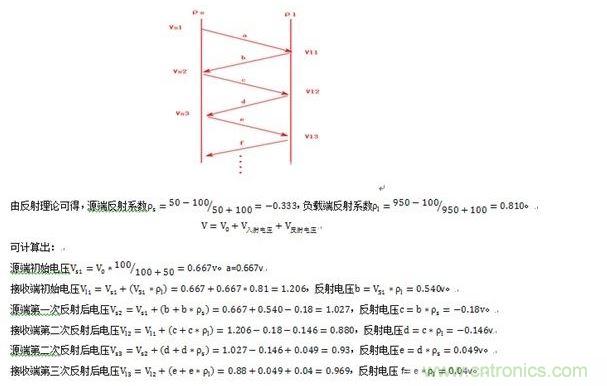

对于理工科来说,一些从数学上去理解问题的过程是必不可少,也是最直观的。高速先生也和大家一样,学习反射都是从手算反弹图开始的。同样的,小高速先生在画出反弹图之后曾经觉得自己懂反射了。<上一页12345下一页>

- 第一页:PCB设计中关于反射的那些事儿

- 第二页:PCB设计学习中的笔记分享

- 第三页:PCB设计中关于场的反射

- 第四页:PCB设计中场的反射不同频率谐波分析(1)

- 第五页:PCB设计中场的反射不同频率谐波分析(2)

可是转念一想,还是发现了很多无法理解的问题:为什么测试时在通道中间测试到的波形有回沟,而在终端测试到的波形又是好的?Breakout区域有一次阻抗不连续,但走出该区域之后,走线从细变宽,会增加一次反射,那是不是全程按照breakout区域走线会比较好?源端匹配电阻是不是也增加了一次反射?是的,其实这些用一句“传输线很短的时候反射掩盖在上升沿中了”就可以解释。但是到底是怎么掩盖在上升沿中的?我们发现在上方的反弹图中传输延时远远大于信号的上升时间,在计算反射时我们用的电压实际上是信号高电平的电压,并没有关注上升沿过程中其他电平的状态,但实际上的情况并不是这样,可是如果我们如果把上升沿的状态加入算式中,那这游戏可就没法玩了。所以,我们需要场的思维.场的反射来到了场的领域,我们要做的第一件事就是把我们的波形拆开,让我们先来看看之前说过的测试点的问题。(关注技术自媒体微信公众号:一博_看得懂的高速设计)为了将问题简化,我们假定一个这样的条件:

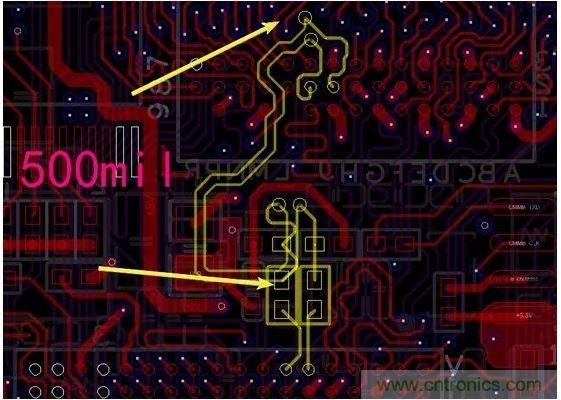

1.在拓扑上,源端完全匹配,末端全反射,理想的100Ω差分传输线。2.传输的为我们之前模拟的DDR3信号,由三次谐波构成。3.测试点位置离接收端距离为500mil。<上一页12345下一页>

1.在拓扑上,源端完全匹配,末端全反射,理想的100Ω差分传输线。2.传输的为我们之前模拟的DDR3信号,由三次谐波构成。3.测试点位置离接收端距离为500mil。<上一页12345下一页> - 第一页:PCB设计中关于反射的那些事儿

- 第二页:PCB设计学习中的笔记分享

- 第三页:PCB设计中关于场的反射

- 第四页:PCB设计中场的反射不同频率谐波分析(1)

- 第五页:PCB设计中场的反射不同频率谐波分析(2)

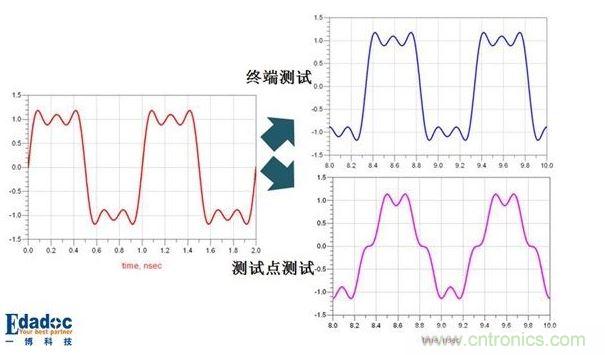

好的,现在开始让我们分析,首先,如同大家在之前文章中看到的,我们接收端信号与测试点信号的区别是这样的:

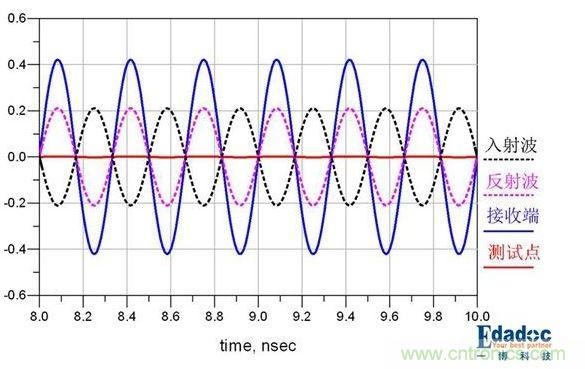

让我们看看1GHz谐波发生了什么:

让我们看看1GHz谐波发生了什么: 测试点测到的是两个信号叠加的波形,一个是入射信号,一个反射波。反射波与入射波幅值相等(末端全反射);走过的路程比入射波多1000mil(一来一回),也就是六分之一波长;两个信号的相位差也就是60°。这样,我们就看到了1GHz的谐波在接收端时蓝色的波形,在测试点处为红色的波形,幅值衰减,相位超前。再看看3GHz的谐波:

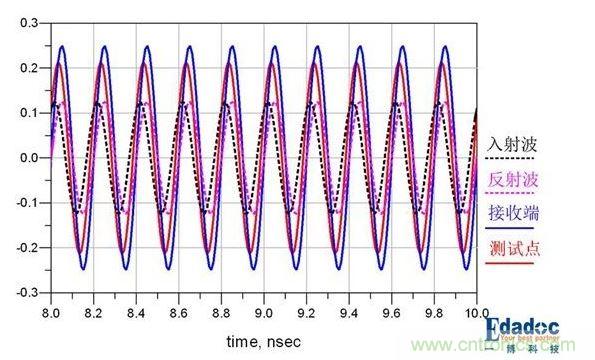

测试点测到的是两个信号叠加的波形,一个是入射信号,一个反射波。反射波与入射波幅值相等(末端全反射);走过的路程比入射波多1000mil(一来一回),也就是六分之一波长;两个信号的相位差也就是60°。这样,我们就看到了1GHz的谐波在接收端时蓝色的波形,在测试点处为红色的波形,幅值衰减,相位超前。再看看3GHz的谐波: 同样的1000mil,对于3GHz来说就是半波长,相位差180°,这样我们就发现在测试点处3GHz的频率分量基本上就衰减完了。<上一页12345下一页>

同样的1000mil,对于3GHz来说就是半波长,相位差180°,这样我们就发现在测试点处3GHz的频率分量基本上就衰减完了。<上一页12345下一页> - 第一页:PCB设计中关于反射的那些事儿

- 第二页:PCB设计学习中的笔记分享

- 第三页:PCB设计中关于场的反射

- 第四页:PCB设计中场的反射不同频率谐波分析(1)

- 第五页:PCB设计中场的反射不同频率谐波分析(2)

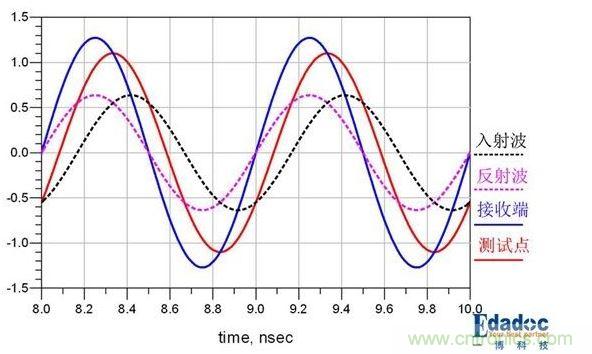

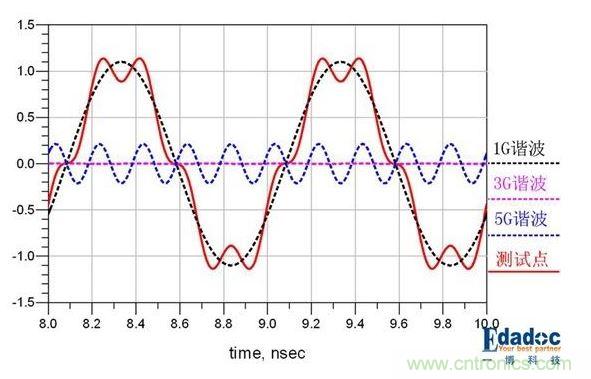

再来看看5GHz的谐波:

相位差300°,于是看到测试点的波形衰减,相位滞后。将在测试点的三个频率分量的叠加再叠加起来之后:

相位差300°,于是看到测试点的波形衰减,相位滞后。将在测试点的三个频率分量的叠加再叠加起来之后: 不知道大家对于这样的分析方法是感觉如何,是觉得把东西变复杂了还是变简单了呢?怎么想没有关系,下一篇中高速先生会将这样的方法再拓展,相信你会爱上这个方法的。<上一页12345

不知道大家对于这样的分析方法是感觉如何,是觉得把东西变复杂了还是变简单了呢?怎么想没有关系,下一篇中高速先生会将这样的方法再拓展,相信你会爱上这个方法的。<上一页12345 - 第一页:PCB设计中关于反射的那些事儿

- 第二页:PCB设计学习中的笔记分享

- 第三页:PCB设计中关于场的反射

- 第四页:PCB设计中场的反射不同频率谐波分析(1)

- 第五页:PCB设计中场的反射不同频率谐波分析(2)