【锦囊二】PCB设计中关于反射的那些事儿

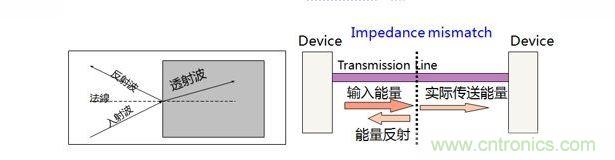

品慧电子讯关于PCB设计中一些反射的问题,前面小编已经抛砖引玉的给大家介绍了了一些《【锦囊一】PCB设计中关于反射的那些事儿》。这里小编将继续为大家放送专家最新更新的PCB设计中反射问题知识!这里将主要讲解PCB设计中反射问题的集总问题,详见下文分析!《【锦囊一】PCB设计中关于反射的那些事儿》新年礼物到了!接下来小编还会继续为大家奉献上该专家基于PCB设计中关于反射的其他相关知识,希望大家耐心等待!大家知道,信号是以电磁波的形式传递的。波从一个介质入射到另一个介质时,会产生反射。同样的,当我们信号传输遇见阻抗不连续时,信号会产生反射。

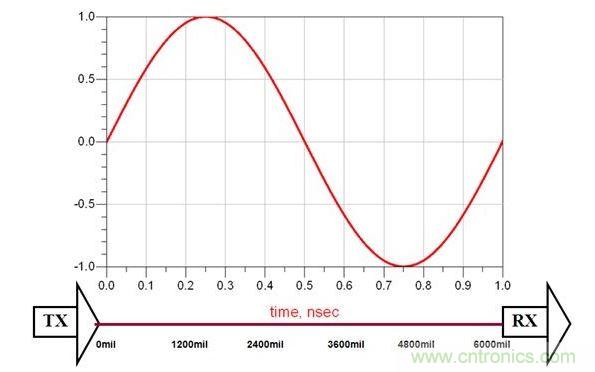

反射能量的强度跟阻抗比匹配的程度相关。在开路短路这种极端情况下,反射的幅值会和入射的幅值相等。由于反射的存在,即使我们的设计中通常不会出现前面例子中分叉之后再接到接收端的情况,还是会有大量相位不相等的谐波在我们传输线中传输。这些能量就会相互产生干扰,受干扰的程度跟反射的幅值和两个能量之间的相位差有关。从前面的例子中我们可以看到,当两个信号的相位差不到λ/20时,叠加后的影响是微乎其微的。大家通常将λ/20作为一个界限,当传输线长度小于λ/20时,我们用集总参数来考虑我们的电路。我们一直在说λ,那λ是什么?如果大家每次都想着λ=v*T=v/f的话,理解一些理论的时候肯定很绕,没法有个直观的反应。在这里大家需要再建立起一个概念,我们通常看到的波形是一个电压/时间的坐标轴,当我们把X轴的时间换成长度,在普通的FR4板材上,我们看到的大致是一个这样的图像:

反射能量的强度跟阻抗比匹配的程度相关。在开路短路这种极端情况下,反射的幅值会和入射的幅值相等。由于反射的存在,即使我们的设计中通常不会出现前面例子中分叉之后再接到接收端的情况,还是会有大量相位不相等的谐波在我们传输线中传输。这些能量就会相互产生干扰,受干扰的程度跟反射的幅值和两个能量之间的相位差有关。从前面的例子中我们可以看到,当两个信号的相位差不到λ/20时,叠加后的影响是微乎其微的。大家通常将λ/20作为一个界限,当传输线长度小于λ/20时,我们用集总参数来考虑我们的电路。我们一直在说λ,那λ是什么?如果大家每次都想着λ=v*T=v/f的话,理解一些理论的时候肯定很绕,没法有个直观的反应。在这里大家需要再建立起一个概念,我们通常看到的波形是一个电压/时间的坐标轴,当我们把X轴的时间换成长度,在普通的FR4板材上,我们看到的大致是一个这样的图像: 12345下一页>

12345下一页> - 第一页:PCB设计中关于反射的那些事儿(1)

- 第二页:PCB设计中关于反射的那些事儿(2)

- 第三页:PCB设计中关于反射的那些事儿(3)

- 第四页:PCB设计中关于反射的那些事儿(4)

- 第五页:PCB设计中关于反射的那些事儿(5)

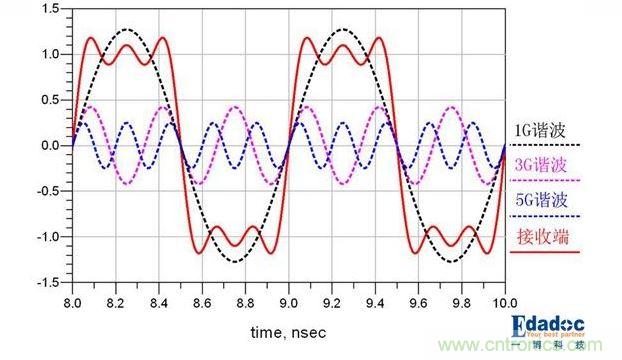

我们要在一条传输线上完成一个1GHz的正弦波,这条传输线大概需要6000mil。所以很多时候我们以为我们传输线上的波形是这样子的:

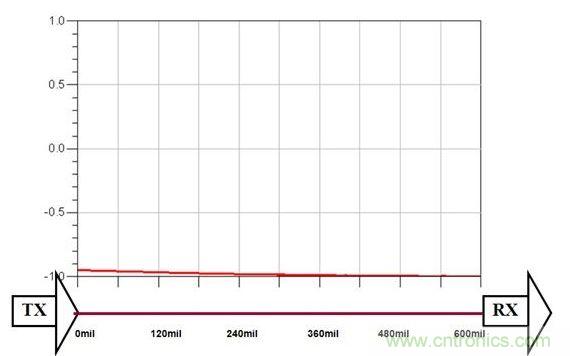

但其实我们传输线上实际的波形可能是这样子的:

但其实我们传输线上实际的波形可能是这样子的: 或者是这样子的:

或者是这样子的: 可以看到其实他们的dv/dX是非常小的,这里用dX不用dt是因为传输线的总电容/电感是跟X有关的。<上一页12345下一页>

可以看到其实他们的dv/dX是非常小的,这里用dX不用dt是因为传输线的总电容/电感是跟X有关的。<上一页12345下一页> - 第一页:PCB设计中关于反射的那些事儿(1)

- 第二页:PCB设计中关于反射的那些事儿(2)

- 第三页:PCB设计中关于反射的那些事儿(3)

- 第四页:PCB设计中关于反射的那些事儿(4)

- 第五页:PCB设计中关于反射的那些事儿(5)

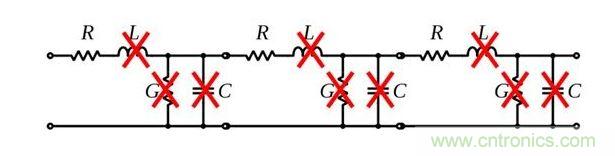

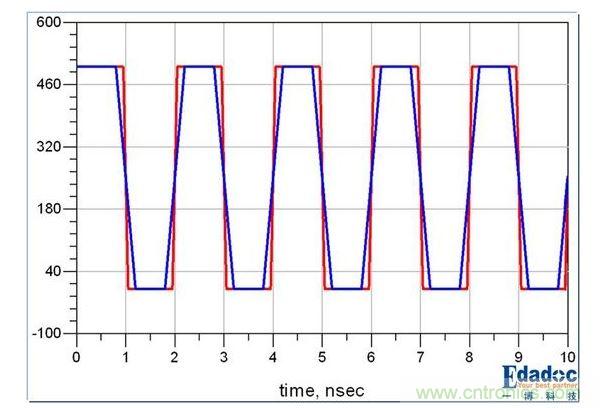

我们都知道地球是圆的,可是身处我们的位置去看的话地球就是平的。同样的,在集总参数中,由于在线路上的电压电流变化速度很慢,我们可以将它当做是直流,在这时,传输线的容抗与感抗都没有表现出来,这时传输线是透明的:

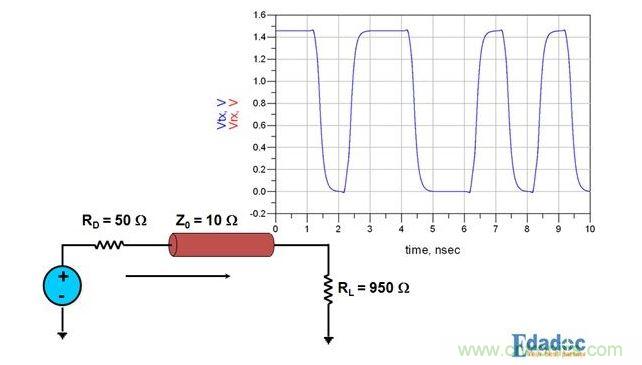

接收端接收到的就是发送端发出的信号,下面是传输线10Ω与传输线100Ω的对比:

接收端接收到的就是发送端发出的信号,下面是传输线10Ω与传输线100Ω的对比:

为什么以前的板子不需要控阻抗,为什么现在的一些模拟信号也是不需要控阻抗的,原因就在这里。通常我们1GHz的正弦波的λ/20在300mil左右,10MHz的正弦波的λ/20则有30000mil。传输线是透明的,接收端接收到的波形与传输的路径没有关系,这就是集总的世界。<上一页12345下一页>

- 第一页:PCB设计中关于反射的那些事儿(1)

- 第二页:PCB设计中关于反射的那些事儿(2)

- 第三页:PCB设计中关于反射的那些事儿(3)

- 第四页:PCB设计中关于反射的那些事儿(4)

- 第五页:PCB设计中关于反射的那些事儿(5)

一些经验公式在上面给大家展示的这张图其实是非常有代表意义的:

这是一个1GHz的信号,上升沿大概在0.1ns左右。大家想到了什么?是的,DDR3的时钟信号。五倍频谐波合成一个波形,上升沿时间为信号周期的十分之一,符合我们一切对信号完整性的预期。该信号五倍频率处的这个谐波称之为最高次有效谐波,我们前文中说的集总参数与分布参数界限的λ/20,指的就是最高次有效谐波的λ/20。所以一个1GHz的信号(注意这里说的是信号,不是正弦波),通常他的λ/20是60mil。但是否每个波形的最高次有效谐波都是信号的五倍频呢?并不一定,大家看下面两幅图:

这是一个1GHz的信号,上升沿大概在0.1ns左右。大家想到了什么?是的,DDR3的时钟信号。五倍频谐波合成一个波形,上升沿时间为信号周期的十分之一,符合我们一切对信号完整性的预期。该信号五倍频率处的这个谐波称之为最高次有效谐波,我们前文中说的集总参数与分布参数界限的λ/20,指的就是最高次有效谐波的λ/20。所以一个1GHz的信号(注意这里说的是信号,不是正弦波),通常他的λ/20是60mil。但是否每个波形的最高次有效谐波都是信号的五倍频呢?并不一定,大家看下面两幅图:

这是两个频率为500MHz的信号,他们周期相等,幅值也相等,但是上升沿不一样。很明显,上升沿较抖的红色信号直到9倍频处还有较为明显的频率分量,而上升沿较缓的蓝色信号在三倍频以后的频率分量就非常少了。<上一页12345下一页>

这是两个频率为500MHz的信号,他们周期相等,幅值也相等,但是上升沿不一样。很明显,上升沿较抖的红色信号直到9倍频处还有较为明显的频率分量,而上升沿较缓的蓝色信号在三倍频以后的频率分量就非常少了。<上一页12345下一页> - 第一页:PCB设计中关于反射的那些事儿(1)

- 第二页:PCB设计中关于反射的那些事儿(2)

- 第三页:PCB设计中关于反射的那些事儿(3)

- 第四页:PCB设计中关于反射的那些事儿(4)

- 第五页:PCB设计中关于反射的那些事儿(5)

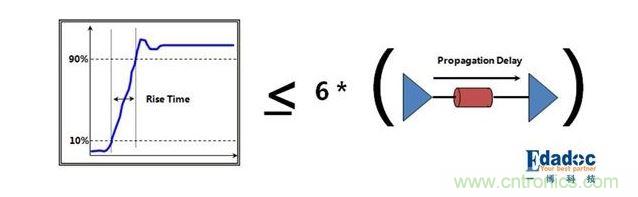

什么时候会出现这种状况呢,不是说好了上升沿时间为信号周期的十分之一吗?由于工艺的不断更新换代,芯片的die电容不断减小,现在大量的100MHz信号的上升沿达到了0.2ns甚至更少,高速先生不久前就碰到过66MHz的信号反射非常严重的。同样是因为工艺的原因,按照上升沿时间为信号周期的十分之一计算的话,25Gbps信号的上升时间应为8ps,臣妾做不到啊!所以在802.3bj中,要求的25G信号的上升沿为9.6ps(20%-80%)。而在现在的高速无源链路上只关心到信号中心频率的两倍频处,再高的频率分量由芯片来给你保证了。为了辅助我们得出最高次有效频率,我们还有这些经验公式:0.35/Tr,0.5/Tr......其中Tr单位使用ns的话,得到的频率为GHz,两个公式的区别在于对最高次有效谐波定义的严格与否。等等!各位看官不要走!如果您觉得这样计算最高次有效谐波的波长再除以二十再跟传输线长度来进行对比来判断是集总参数还是分布参数再去决定是否考虑传输线效应太麻烦的话,这里还有个最简单的:

就是这个了,如果上升时间小于六倍的传输延时,我们需要考虑传输线效应,称之为高速。最后,让我们来对比一下两种方法算出来的分布参数与高速有何不同,拿我们最开始的DDR3的波形举例:上升时间Tr为100ps;高速的临界条件为传输延时为16.6ps;16.6ps传输的长度为100mil;100mil为3GHz正弦波的λ/20;3GHz约等于使用0.35/Tr来算最高次谐波3.5GHz;如果使用0.5/Tr来算最高次谐波的话,他的最高次谐波为5GHz;回到文章顶部看我们最开始分享的那张图......其实我们用有效频率的二十分之波长来定义分布/集总参数与用六分之上升时间来定义高速/低速信号是完全一样的东西啊。耐心看完的朋友们都是英雄,我们下期再虐!<上一页12345

就是这个了,如果上升时间小于六倍的传输延时,我们需要考虑传输线效应,称之为高速。最后,让我们来对比一下两种方法算出来的分布参数与高速有何不同,拿我们最开始的DDR3的波形举例:上升时间Tr为100ps;高速的临界条件为传输延时为16.6ps;16.6ps传输的长度为100mil;100mil为3GHz正弦波的λ/20;3GHz约等于使用0.35/Tr来算最高次谐波3.5GHz;如果使用0.5/Tr来算最高次谐波的话,他的最高次谐波为5GHz;回到文章顶部看我们最开始分享的那张图......其实我们用有效频率的二十分之波长来定义分布/集总参数与用六分之上升时间来定义高速/低速信号是完全一样的东西啊。耐心看完的朋友们都是英雄,我们下期再虐!<上一页12345 - 第一页:PCB设计中关于反射的那些事儿(1)

- 第二页:PCB设计中关于反射的那些事儿(2)

- 第三页:PCB设计中关于反射的那些事儿(3)

- 第四页:PCB设计中关于反射的那些事儿(4)

- 第五页:PCB设计中关于反射的那些事儿(5)