芯片设计:速度面积功耗就一定能折中?

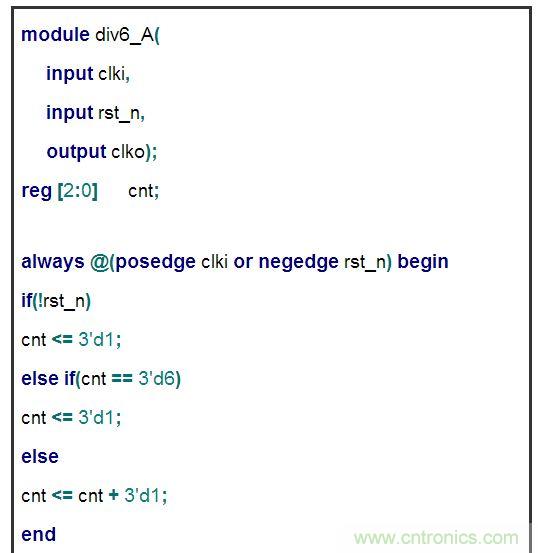

品慧电子讯芯片设计中几个重要的指标总是让设计工程师自以为是的想到各种折中的方法,实则不然。在实际电路设计中,不要仅仅考虑功能实现,需要多想想是否有更好的解决方案,让面积,速度,功耗表现更佳才是上策。当然这也是优秀的工程师和平庸的工程师设计出来的产品会有巨大的差异。在芯片设计中,大家通常都会注意到几个重要的指标:速度:电路可以跑多少MHz的时钟频率,一般来说,速度越快,能处理的数据量就越多,性能越好。面积:电路的物理实现需要占用硅片的面积,占用的面积越小,成本越低。功耗:电路工作所消耗的能量,功耗越低,芯片越省电,发热量 也越低,能耗低,环保。书本上说,速度、面积、功耗是互相牵制的,在相同的制造工艺(制程)条件下,一般来说,速度越快,晶体管尺寸越大,面积就越大,功耗也越高。为了降低功耗,可以降低芯片的工作速度,让时钟的跳变频率变慢。为了降低成本,减小芯片面积,可以采用面积比较小(W比较小)的晶体管,由于电流和W成正比,因此面积减小,速度会变慢。(为了即减小面积,同时提高速度,则必须让L变小,也就是提升制程,65nm换成45nm,45nm换成28nm等等)为了提高速度,我们需要加大充电电流,加大电流,必然导致功耗增加。(为了不增加电流而提高速度,必须减少电容,或者降低充电电压,这两个动作也是靠工艺水平的提升来实现,比如45nm换成28nm工艺)请大家注意,上面的速度、面积、功耗的折中和互相牵制是建立在相同制程,相同的IP Vendor,以及相同的电路条件下。我想要提醒的是,如果不满足这3个条件,这3个因素可能不是折中的关系,有可能会出现速度慢,面积大,功耗也高的情况。说明如下:1 )在相同的工艺制程,相同的IP Vendor(包括相同的标准单元)条件下,同一个功能,不同的电路实现方案,有可能会出现方案A比方案B面积大,速度慢,功耗高。举例说明:实现一个6分频电路:方案A:

12下一页>

- 第一页:芯片设计中的几个重要指标

- 第二页:方案对比说明速度面积功耗就一定能折中?

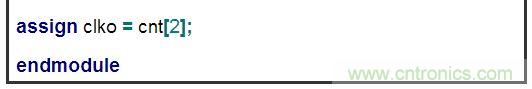

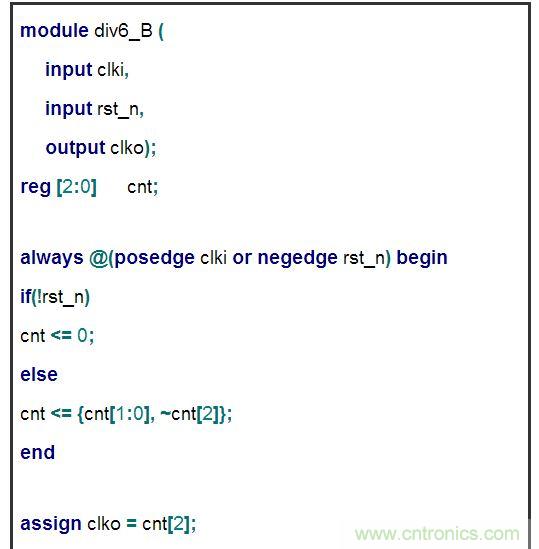

方案B:

上面的电路,功能一模一样,都实现了时钟6分频。方案A的使用了加法, 方案B采用了循环移位。很明显,# 加法比移位的逻辑电路多,方案A的面积比方案B大;# 加法需要的逻辑路径长,因此方案A的最快工作频率低于方案B# 方案B逻辑少,数据变化产生的节点电压变化少,并且,方案B类似格雷码,触发器的跳变次数也比方案A要少,因此方案B的功耗小。综上所述,方案A比方案B,面积大,速度慢,功耗高。彻底的完败。因此,在实际电路设计中,不要仅仅考虑功能实现,需要多想想是否有更好的解决方案,让面积,速度,功耗表现更佳;优秀的工程师和平庸的工程师设计出来的产品会有巨大的差异,竞争力体现在人才的智慧上,聪明的大脑在芯片设计中至关重要。我们每个设计工程师都要力争成为智慧的工程师。2)同样的数字电路,选择不同的标准单元库,有可能会出现标准单元库A的实现, 比标准单元库B的实现面积大,功耗大,速度也慢。可以参考上面的解释,因为不同的标准单元库是不同的人设计出来的,也有聪明和平庸之分。即使同一个 Vendor的不同标准单元库,也可能会发现新的改进库比原来的面积,速度,功耗都要优。模拟IP也如此,不同的Vendor有差异。 由于IP 库的差异,对设计工程师提出了更多要求,要求芯片设计者能够甄别比较优秀的IP,从而提升产品的整体竞争力。IP如果选择了比较平庸的,将来产品的竞争力 就会大打折扣。<上一页12

上面的电路,功能一模一样,都实现了时钟6分频。方案A的使用了加法, 方案B采用了循环移位。很明显,# 加法比移位的逻辑电路多,方案A的面积比方案B大;# 加法需要的逻辑路径长,因此方案A的最快工作频率低于方案B# 方案B逻辑少,数据变化产生的节点电压变化少,并且,方案B类似格雷码,触发器的跳变次数也比方案A要少,因此方案B的功耗小。综上所述,方案A比方案B,面积大,速度慢,功耗高。彻底的完败。因此,在实际电路设计中,不要仅仅考虑功能实现,需要多想想是否有更好的解决方案,让面积,速度,功耗表现更佳;优秀的工程师和平庸的工程师设计出来的产品会有巨大的差异,竞争力体现在人才的智慧上,聪明的大脑在芯片设计中至关重要。我们每个设计工程师都要力争成为智慧的工程师。2)同样的数字电路,选择不同的标准单元库,有可能会出现标准单元库A的实现, 比标准单元库B的实现面积大,功耗大,速度也慢。可以参考上面的解释,因为不同的标准单元库是不同的人设计出来的,也有聪明和平庸之分。即使同一个 Vendor的不同标准单元库,也可能会发现新的改进库比原来的面积,速度,功耗都要优。模拟IP也如此,不同的Vendor有差异。 由于IP 库的差异,对设计工程师提出了更多要求,要求芯片设计者能够甄别比较优秀的IP,从而提升产品的整体竞争力。IP如果选择了比较平庸的,将来产品的竞争力 就会大打折扣。<上一页12 - 第一页:芯片设计中的几个重要指标

- 第二页:方案对比说明速度面积功耗就一定能折中?