就是这么任性的DDR3设计,看专家怎么降服?

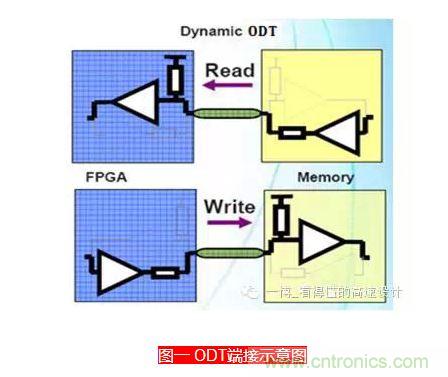

品慧电子讯DDR3主控为国外知名公司的芯片,按说该芯片的常规设计对于我们的设计人员来说应该没有太大的问题,但是,这个设计的硬件工程师出于后期调试和EMI的考虑在所有的数据信号线上加了串阻,这就使得原本就很紧张的布线空间捉襟见肘了,为此我们的设计人员叫苦不迭,这么紧张的空间怎么去绕等长呢?话说有三个人将被依次执行死刑,分别是牧师、律师、工程师。牧师第一个被推向绞刑架。侩子手拉动控制杆以抽出活板,但它失灵了。牧师宣称这是上帝的旨意,要求得到释放,于是他获得了自由。接着,律师走向了绞刑架。侩子手再一次拉动了控制杆,但它仍然失灵,律师同样要求获得释放,因为他不能因为同一罪状被判两次死刑,于是他也获得了自由。最后,轮到工程师了。他上去对脚手架仔细检查了一遍,在侩子手还没动手之前,他抬起头大声说,“啊哈,是这里出了故障!”看到这里,大家应该知道结果了吧,真是好奇害死猫,有时工程师的强迫症来了真的会差点累及无辜。这不,最近就遇到了一件很揪心的DDR3设计。该DDR3主控为国外知名公司的芯片,功能强大而且比较成熟了,该设计为32位系统,一个主控芯片拖了4片DDR3颗粒,采用6层板,空间比较紧张。这种常规设计对于我们的设计人员来说应该没有太大的问题,好歹我们一年也有好几千款的DDRx设计,在这个上面的技术积累还是很多的。但是,这个设计的硬件工程师出于后期调试和EMI的考虑在所有的数据信号线上加了串阻,这就使得原本就很紧张的布线空间捉襟见肘了,为此我们的设计人员叫苦不迭,这么紧张的空间怎么去绕等长呢?就算累到没朋友恐怕也很难保证很好的完成设计吧!无解了,只能请高速先生出招!首先查看了下主控芯片的数据手册,什么ODT、Write leveling该有的功能都有,好家伙,这下有救了。为什么呢?因为我们有任性的ODT功能。ODT是On Die Termination的缩写,又叫片内端接,顾名思义,就是将端接电阻放在了芯片内部,这个功能只有在DDR2以上的数据信号才有,其他信号无此宠幸!有了这个功能,原本需要在PCB板上加串阻的数据信号就不用再额外添加端接了,因为芯片内部可以打开这个ODT端接功能,而且端接还可调,哈哈,确实有点任性。下面是ODT的端接示意图。

当数据读操作的时候,主控(FPGA或CPU)读取Memory颗粒的数据,此时主控为接收端,可以根据需要选择是否打开ODT;当数据写操作的时候,主控(FPGA或CPU)将数据写入到Memory颗粒,此时颗粒为接收端,也可以根据需要选择是否打开ODT,这种操作可以在寄存器内部实现控制。现在回到我们前面的设计,这个数据串阻到底有没有必要呢?答案当然是非必要的,而且可以说是费力不讨好(针对此项目)!这也不能怪我们的硬件工程师,既要保证产品性能,又要保证产品有问题的时候多种调试手段,压力大,强迫症就这样来了!那又为什么说费力不讨好呢?主要有下面两点:其一是影响了布线空间,让寸土寸金的空间雪上加霜,牺牲了走线空间,线间距就很难保证,间接的导致串扰,减少系统裕量;其二是这个端接已经在芯片内部有了,再额外在板上加串阻会增加器件成本,同时串阻的位置也有待斟酌,是加在主控端好呢还是加在Memory颗粒端好呢?确实有点画蛇添足的赶脚!为了后期的好调试而带来其他的隐患,得不偿失啊!最后和硬件工程师进行了利害关系沟通后,终于同意去掉数据信号的串阻,现在板子已经调试成功,准备量产阶段 。

当数据读操作的时候,主控(FPGA或CPU)读取Memory颗粒的数据,此时主控为接收端,可以根据需要选择是否打开ODT;当数据写操作的时候,主控(FPGA或CPU)将数据写入到Memory颗粒,此时颗粒为接收端,也可以根据需要选择是否打开ODT,这种操作可以在寄存器内部实现控制。现在回到我们前面的设计,这个数据串阻到底有没有必要呢?答案当然是非必要的,而且可以说是费力不讨好(针对此项目)!这也不能怪我们的硬件工程师,既要保证产品性能,又要保证产品有问题的时候多种调试手段,压力大,强迫症就这样来了!那又为什么说费力不讨好呢?主要有下面两点:其一是影响了布线空间,让寸土寸金的空间雪上加霜,牺牲了走线空间,线间距就很难保证,间接的导致串扰,减少系统裕量;其二是这个端接已经在芯片内部有了,再额外在板上加串阻会增加器件成本,同时串阻的位置也有待斟酌,是加在主控端好呢还是加在Memory颗粒端好呢?确实有点画蛇添足的赶脚!为了后期的好调试而带来其他的隐患,得不偿失啊!最后和硬件工程师进行了利害关系沟通后,终于同意去掉数据信号的串阻,现在板子已经调试成功,准备量产阶段 。