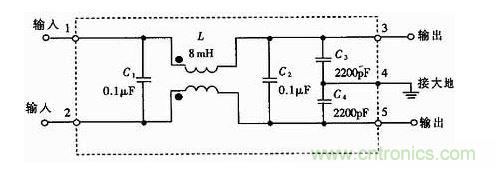

电路分析:电磁干扰滤波器原理图

本文介绍的是一款电磁干扰滤波器的原理电路,该五端器件有两个输入端、两个输出端和一个接地端,使用时外壳应接通大地。具体设计请看下文。

以下为一款电磁干扰滤波器的原理电路,该五端器件有两个输入端、两个输出端和一个接地端,使用时外壳应接通大地。电路中包括共模扼流圈(亦称共模电感)L、滤波电容C1~C4.L对串模干扰不起作用,但当出现共模干扰时,由于两个线圈的磁通方向相同,经过耦合后总电感量迅速增大,因此对共模信号呈现很大的感抗,使之不易通过,故称作共模扼流圈。它的两个线圈分别绕在低损耗、高导磁率的铁氧体磁环上,当有电流通过时,两个线圈上的磁场就会互相加强。当额定电流较大时,共模扼流圈的线径也要相应增大,以便能承受较大的电流。此外,适当增加电感量,可改善低频衰减特性。C1和C2采用薄膜电容器,容量范围大致是0.01μF~0.47μF,主要用来滤除串模干扰。C3和C4跨接在输出端,并将电容器的中点接地,能有效地抑制共模干扰。C3和C4亦可并联在输入端,仍选用陶瓷电容,容量范围是2200pF~0.1μF.为减小漏电流,电容量不得超过0.1μF,并且电容器中点应与大地接通。C1~C4的耐压值均为630VDC或250VAC.