如何调整PCB布局以降低超级结MOSFET辐射

要在不同应用中驱动快速开关超级结MOSFET,必须对器件寄生效应影响和PCB布局寄生效应影响都了解。设计适合快速开关超级结MOSFET的栅极驱动电路时有许多因素需考虑,这里接着为大家讲解。

本文接着上次的《如何解决超级结MOSFET时栅极振荡? 》来继续为大家讲解如何调整PCB布局以降低超级结MOSFET辐射。

最大限度降低器件和印刷电路板(PCB)的寄生电感和电容是重要的设计考虑因素,可减少不希望的噪声。要在不同应用中驱动快速开关超级结MOSFET,必须对器件寄生效应影响和PCB布局寄生效应影响都了解。设计适合快速开关超级结MOSFET的栅极驱动电路时有许多因素需考虑。关于最大限度减少不必要的噪声有几项主要准则。

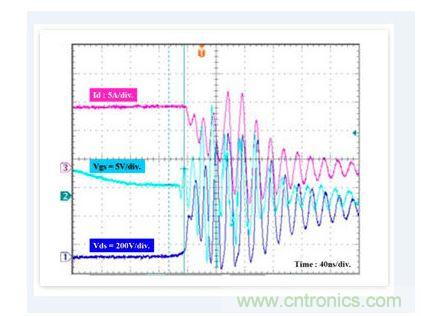

在某些情况下,比如输入电压瞬变或短路,MOSFET所承受的高di/dt和dv/dt可能会导致开关特性异常或器件损坏。图1显示的是关断瞬态期间PFC电路中超级结MOSFET的振荡波形。器件和电路板中的寄生元件毫无疑问是引起不必要振荡和噪声的主要原因。在这种情况下,增大栅极电阻能够抑制峰值漏源极电压并防止由超级结MOSFET的引脚电感和寄生电容引起的栅极振荡。而且还能在导通和关断期间减缓电压上升速率(dv/dt)和电流上升速率(di/dt)。不利的是,额外的外部栅极电阻也会影响MOSFET中的开关损耗。随着工作开关频率增大,控制开关损耗就很重要了,因为器件必须达到目标应用所要求的最高效率。

图1:使用超级结MOSFET的PFC电路的剧烈振荡波形

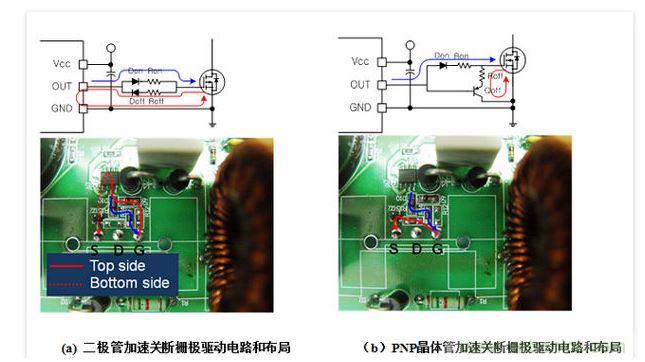

避免振荡的另一种重要方法是最大限度降低器件和电路板的电感。正确配置栅极驱动电路对于操作MOSFET的同时最大限度减少不必要噪声非常重要。有两种栅极驱动器可以考虑。(a)栅极驱动电路最适合快速可变导通和关断。尽管实施起来更为简单,但快速关断瞬态和较大的栅极关断环路仍可形成高di/dt,造成源极电感上的高压降(Ldi/dt)会引起栅极振荡。从而带来一些副作用,比如出现电压/电流尖峰或EMI性能恶化。另一种快速导通和快速关断的栅极驱动电路是(b)PNP晶体管关断栅极驱动电路。该更为有效的配置可最大限度降低较小栅极驱动环路中的源极电感,而且仍能实现快速关断。

图2:栅极驱动电路和布局

要实现平衡,重要的是要具有优化的栅极驱动电路,因为功率MOSFET是栅极控制型器件。下列建议对于实现高效率(无电压尖峰)和低电磁干扰(因快速开关MOSFET产生)非常重要。

快速超级结MOSFET的布局准则概要

●要实现超级结MOSFET的最佳性能,需要优化的布局

●栅极驱动器和Rg必须尽可能地靠近MOSFET栅极引脚。

●将电源GND 和栅极驱动器GND分开。

●最大限度降低PCB上的寄生电容Cgd和源极电感。

●对于并联超级结MOSFET,必须采用对称布局。

●通过增大Rg或使用铁氧体磁珠减缓dv/dt和di/dt